* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download combinational logic design

Flip-flop (electronics) wikipedia , lookup

Field-programmable gate array wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power MOSFET wikipedia , lookup

Invention of the integrated circuit wikipedia , lookup

Crossbar switch wikipedia , lookup

Opto-isolator wikipedia , lookup

Index of electronics articles wikipedia , lookup

Rectiverter wikipedia , lookup

Two-port network wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Integrated circuit wikipedia , lookup

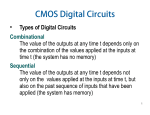

COMBINATIONAL LOGIC DESIGN EMT 251 CMOS Characteristics (Refresh) CMOS Transistors (N-type) CMOS Transistors (P-type) Reality NMOS pulling to GND (Pull Down Network) PMOS pulling to Vdd (Pull Up Network) Combinational vs Sequential Combinational vs Sequential Logic In Combinational Logic Circuit In Out Combinational Logic Circuit State Combinational Output = f ( In) Sequential Output = f(In, Previous In) Out Combinational vs Sequential Logic CMOS Schematic Combinational Logic (Static) • Complementary CMOS • Transmission Gates • Pass Transistor • Pseudo-NMOS Sequential Logic (Dynamic) • Domino Logic • NORA Logic Static Complementary CMOS Static Complementary CMOS • At every point in time (except during the switching transients) each gate output is connected to either VDD or Vss via a low-resistive path. • The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods). • This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes. Static Complementary CMOS VDD In1 In2 PUN InN In1 In2 InN PMOS only F(In1,In2,…InN) PDN NMOS only PUN and PDN are dual logic networks NMOS Transistors in Series/Parallel Connection Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high A B X Y Y = X if A and B A X B Y Y = X if A OR B NMOS Transistors pass a “strong” 0 but a “weak” 1 PMOS Transistors in Series/Parallel Connection PMOS switch closes when switch control input is low A B X Y Y = X if A AND B = A + B A X B Y Y = X if A OR B = AB PMOS Transistors pass a “strong” 1 but a “weak” 0 Inverter Gate NAND Gate NOR Gate Complex CMOS Gate B A C D OUT = D + A • (B + C) A D B C Constructing a Complex Gate VDD VDD C F SN4 F SN1 A SN3 D B C B SN2 A D A B D C F (a) pull-down network (b) Deriving the pull-up network hierarchically by identifying sub-nets A D B C (c) complete gate