* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lecture 10 - UniMAP Portal

Electrical ballast wikipedia , lookup

Solar micro-inverter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Signal-flow graph wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Power inverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Stray voltage wikipedia , lookup

Alternating current wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power electronics wikipedia , lookup

Current source wikipedia , lookup

Two-port network wikipedia , lookup

Mains electricity wikipedia , lookup

Voltage regulator wikipedia , lookup

Opto-isolator wikipedia , lookup

Distribution management system wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Current mirror wikipedia , lookup

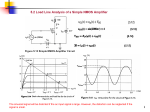

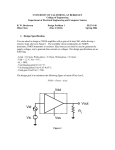

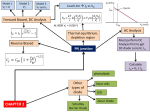

Transistor Characteristics EMT 251 Outline • • • • Introduction MOS Capacitor nMOS I-V Characteristics (ideal) pMOS I-V Characteristics (ideal) Introduction • So far, we have treated transistors as ideal switches • An ON transistor passes a finite amount of current – Depends on terminal voltages – Derive current-voltage (I-V) relationships • Transistor gate, source, drain all have capacitance – I = C (DV/Dt) -> Dt = (C/I) DV – Capacitance and current determine speed MOS Capacitor • Gate and body form MOS capacitor • Operating modes – Accumulation – Depletion – Inversion polysilicon gate silicon dioxide insulator Vg < 0 -V + - p-type body (a) 0 < V g < Vt V+ + - depletion region (b) V g > Vt V++ (c) + - inversion region depletion region Terminal Voltages • Mode of operation depends on Vg, Vd, Vs – Vgs = Vg – Vs – Vgd = Vg – Vd – Vds = Vd – Vs = Vgs - Vgd • Three regions of operation – Cutoff – Linear – Saturation nMOS Cutoff • No channel • Vgs < Vt • Ids = 0 Vgs = 0 + - g + - s d n+ n+ p-type body b Vgd nMOS Linear • Channel forms Vgs > Vt + - – Vds = Vgs-Vgd – If Vds=0 (i.e. Vgs=Vgd) • No electrical field tending to push current fr. d to s. • Small positive potential Vds • Current flows from d to s – e- from s to d • Ids increases with Vds • Similar to linear resistor g + - s d n+ n+ Vgd = Vgs Vds = 0 p-type body b Vgs > Vt + - g s + d n+ n+ p-type body b Vgs > Vgd > Vt Ids 0 < Vds < Vgs-Vt nMOS Saturation • Channel pinches off • Ids independent of Vds • We say current saturates • Similar to current source Vgs > Vt + - g + - Vgd < Vt d Ids s n+ n+ p-type body b Vds > Vgs-Vt Nmos region of operation 1. Cutoff region: VGS < VT, any value of VDS ID = 0 2. Linear (or Resistive, or Triode) region: VGS > VT, VDS < (VGS – VT) V I D VGS VT DS VDS 2 W where nCox L 3. Saturation region: VGS > VT, VDS > (VGS – VT) I DSAT 2 VGS VT 2 where n Cox W L “CUTOFF” region: VG < VT Example • We will be using a 0.6 m process for your project – From AMI Semiconductor 2.5 – tox = 100 Å V =5 2 – = 350 cm2/V*s 1.5 V =4 – Vt = 0.7 V 1 V =3 • Plot Ids vs. Vds 0.5 V =2 V =1 – Vgs = 0, 1, 2, 3, 4, 5 0 0 1 2 3 4 – Use W/L = 4/2 l V Ids (mA) gs gs gs gs gs ds 3.9 8.85 1014 W W W 2 Cox 350 120 A / V 8 L 100 10 L L 5 pMOS I-V • All doping and voltages are inverted for pMOS • Mobility mp is determined by holes – Typically 2-3x lower than that of electrons mn – 120 cm2/V*s in AMI 0.6 mm process • Thus pMOS must be wider to provide same current – In this class, assume mn / mp = 2 – *** plot I-V Transistor Operation • Current depends on region of transistor behavior • For what Vin and Vout are nMOS and pMOS in – Cutoff? – Linear? – Saturation? Schematic of CMOS inverter nMOS Operation Cutoff Vgsn < Vtn Vin < Vtn Linear Vgsn > Vtn Vin > Vtn Vdsn < Vgsn – Vtn Vout < Vin - Vtn Vgsn = Vin Saturated Vgsn > Vtn Vin > Vtn Vdsn > Vgsn – Vtn Vout > Vin - Vtn VDD Vdsn = Vout Vin Idsp Idsn Vout pMOS Operation Cutoff Vgsp > Vtp Vin > VDD + Vtp Vgsp = Vin - VDD Vdsp = Vout - VDD Linear Vgsp < Vtp Vin < VDD + Vtp Vdsp > Vgsp – Vtp Vout > Vin - Vtp Saturated Vgsp < Vtp Vin < VDD + Vtp Vdsp < Vgsp – Vtp Vout < Vin - Vtp VDD Vtp < 0 Vin Idsp Idsn Vout Calculation of VIL When the input voltage is Vin = VIL, the slope of the VTC is equal to [-1](dVout/dVin). At this point B, nMOS transistor operates in saturation while the pMOS transistor operates in the linear region. Using KCL at output node: [Id,n(saturation)= Id,p(linear)] Calculation of VIH At point D, input voltage is equal to VIH, the nMOS transistor operates in the linear region and pMOS transistor operates in saturation. By applying KCL at the output node: [ Id,n(linear) = Id,p(saturation)] Calculation of Vth Threshold voltage is defined as Vth=Vin=Vout. For Vin=Vout, both transistor operate in saturation region, refer point C. By applying KCL at output node: [ Idn(saturation)=Idp(saturation) ] Exercise 1 Consider a CMOS inverter circuit with the following parameters, calculate the (W/L) ratios of the nMOS and pMOS transistors if the switching voltage is Vth = 1.5 V. VDD = 3.3 V VT,n = 0.6 V VT,p = -0.7V µncox = 80 µA/V2 µpcox = 30 µA/V2 Exercise 2 Consider a CMOS inverter circuit with the following parameters, calculate the Switching voltage (Vth) of the circuit. VDD = 3.3 V VT,n = 0.6 V VT,p = -0.7V µncox = 80 µA/V2 µpcox = 30 µA/V2 (W/L)n = 8 (W/L)p = 12 Voltage transfer characteristic Inverter with n-Type MOSFET load Depletion-Load nMOS Inverter Calculation of VOH When the input voltage Vin is smaller than the driver threshold voltage VTO, the driver transistor is turned off and thus not conduct any drain current. ID,load = 0, VOH = VDD ID,load = 0 Calculation of VOL Assume Vin = VOH = VDD. Driver transistor operate in linear region and load transistor operate in saturation. By using KCL. Id,driver(linear) = Id,load(saturation) Calculation of VIL When Vin = VIL the slope of the VTC is equal to (-1),(dVout/dVin). Driver transistor operate in saturation region and load transistor operate in linear region. KCL Id,driver(saturation) = Id,load(linear) Calculation of VIH Driver transistor operate in linear region and load transistor operate in saturation region. Id,driver(linear) = Id,load(saturation) Operating Regions (Summary) nMOS pMOS 2.5 A Cutoff Linear 2 B Saturation Linear 1.5 C Saturation Saturation D Linear Saturation E Linear Cutoff NMOS off PMOS res NMOS s at PMOS res NMOS sat PMOS sat NMOS res PMOS sat 0.5 Region 1 Vout 0.5 1 1.5 2 NMOS res PMOS off 2.5 Vin Exercise 3 VDD = 3.3 V Threshold voltage nMOS (VT,n) = 0.6 V Threshold voltage pMOS (VT,p) = -0.7V Kn = 200 µA/V2 Kp = 80 µA/V2 Based on the inverter circuit and parameter in figure above, what is the value of: i) Switching Voltage, VTH ii) Input Voltage High, VIH THE END

![SpiceAss[2] - simonfoucher.com](http://s1.studyres.com/store/data/007214569_1-1b3e0e1e96d8c8a37166cbdff9c4eb24-150x150.png)