* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Slide 1

Power inverter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Buck converter wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrated circuit wikipedia , lookup

Control system wikipedia , lookup

Curry–Howard correspondence wikipedia , lookup

Power MOSFET wikipedia , lookup

Opto-isolator wikipedia , lookup

Immunity-aware programming wikipedia , lookup

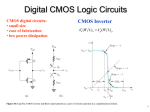

Field-Effect Transistors 1. Understand MOSFET operation. 2. Understand the basic operation of CMOS logic gates. 3. Make use of p-fet and n-fet for logic gate implementation NMOS AND PMOS TRANSISTORS The MOS Transistor Gate Oxyde Gate Source Polysilicon n+ Drain n+ p-substrate Bulk Contact CROSS-SECTION of NMOS Transistor Field-Oxyde (SiO2) p+ stopper Cross-Section of CMOS Technology MOS transistors Types and Symbols S D G G S NMOS Enhancement D PMOS Enhancement NMOS Threshold Voltage: Concept + S VGS - D G n+ n+ n-channel Depletion Region p-substrate B PMOS Mode of Operation • Cut off • Liner • Saturation Operation in the Cutoff Region iD 0 for vGS Vto Operation in the Linear Region Vto VDS VGS Vto iD K 2 ( vGS vto ) vDS v W K L KP 2 2 DS Operation in the Saturation VDS VGS Vto iD K vGS vto 2 iD Kv 2 DS Transistor in Saturation VGS VDS > VGS - VT G D S n+ - VGS - VT + n+ MOSFET Summary CMOS Inverter MOS transistors logic input S D G G D S NMOS Enhancement PMOS Enhancement G =‘1’ then turn on the n-fet as Vgs > V threshold G = ‘0’ then turn on the p-fet as Vgs is negative as Vs > Vg CMOS NAND Gate CMOS NOR Gate The Ideal Gate Vout Ri = Ro = 0 g= Vin Delay Definitions Vin 50% t t Vout t pLH pHL 90% 50% 10% tf t tr CMOS INVERTER The CMOS Inverter: A First Glance VDD Vin Vout CL CMOS Properties • Full rail-to-rail swing • Symmetrical VTC • Propagation delay function of load capacitance and resistance of transistors • No static power dissipation • Direct path current during switching Voltage Transfer Characteristic CMOS Inverter VTC NMOS off PMOS lin 5 Vou t 4 NMOS sat PMOS lin 2 3 NMOS sat PMOS sat 1 NMOS lin PMOS sat 1 2 3 4 NMOS lin PMOS off 5 Vin Simulated VTC Vout (V) 4.0 2.0 0.0 0.0 1.0 2.0 3.0 Vin (V) 4.0 5.0 Where Does Power Go in CMOS? • Dynamic Power Consumption Charging and Discharging Capacitors • Short Circuit Currents Short Circuit Path between Supply Rails during Switching • Leakage Leaking diodes and transistors Dynamic Power Dissipation Vdd Vin Vout CL 2 dd L Energy/transition = C * V L Power = Energy/transition * f = C * V 2 dd *f Not a function of Ltransistor sizes! dd Need to reduce C , V , and f to reduce power. CMOS Logic Implementation Vdd A CMOS logic gate consists of p-tree for pull-up n-tree for pull-down. P-tree Output Inputs N-tree CMOS Logic Implementation • Duality f = A+B’C if A = ‘1’ , or B=‘0’ and C=‘1’ , then f = ‘1’ if the logic function is in the form as f, then use Direct Implementation, for the P-tree implementation and logic function series connection so the term B`C is in series or logic function parallel connection so A, B`C is in parallel use complement of the input signals That is, A`, B and C` are used as inputs CMOS Logic Implementation f = A+B’C A = ‘1’ A`= ‘0’, P1 on B B’= ‘1’ B = ‘0’ P2 on C = ‘1’ C`= ‘0’, P3 on C` either P1 on or P2 and P3 are on then f = ‘1’ P2 P1 A` P3 Since ‘0’ is need to turn on the use A`, B and C` as the inputs to the P- tree, instead of the original input variables. Both p-tree and n-tree have the same set of inputs. CMOS Gate Implementation Once P-tree is designed, use duality for the N- tree P2 B P1 A` P3 C` f A` B N1 N2 N3 C` • Duality Series connection in P – tree parallel for N- tree Parallel connection in P-tree series for N-tree f = A+B’C if A = ‘1’ , A`=‘0’, B’=‘1, B=‘0’ and C=‘1’ , C`=‘0’, then f = ‘1’ pull up the output through the p-tree net if A = ‘0’ , A`=‘1’, B’=‘0’, B=‘1’ and C=‘0’ , C`=‘1’, then f = ‘0’ pull down the output through n-tree net CMOS Gate Implementation P2 B P1 P3 C` f = A+B’C A = ‘1’ , A`=‘0’, P1 turn on or B’=‘1, B=‘0’, P2 turn on and C=‘1’ , C`=‘0’, P3 turn on A` then f = ‘1’ pull up the output through the p-tree net through P1 or P2 and P3 f A` B N1 N2 N3 C` if A = ‘0’ , A`=‘1’, N1 turn on B’=‘0’, B=‘1’, N2 turn on or C=‘0’ , C`=‘1’, N3 turn on then f = ‘0’ pull down the output through n-tree net through N1 and N2 , or N1 and N3 CMOS Gate Implementation f A B`C If f is in this form, there are two ways to implement the logic gate for the logic function. 1. expand the logic function through de Morgan rule and direct implementation on the expanded function. f = (A+B`C)` = A`(B`C)`= A`(B``+C`) = A`(B+C`) Implement the logic gate with the previous method, the input signals are A, B` and C A B` P1 P2 P3 f C CMOS Gate Implementation f A B`C A Use duality to complete design for the n-tree B` P1 P2 C P3 f A B` N1 N2 N3 C CMOS Gate Implementation f A B`C 2. Take f g then , g = A+B`C Use g to define the n-tree configuration. If g is true f = ‘0’ Same implementation rule apply, and logic function series connection so the term B`C is in series or logic function parallel connection, and input variables remain un-change A = ‘1’, g is true, N1 on B`= ‘1’, and C = ‘1’, g is true N2 and N3 are on f B` N1 N2 N3 C CMOS Gate Implementation f A B`C A Use the duality to complete design for the p-tree. B` P1 P2 C P3 f A B` N1 N2 N3 C Comparison of Design Method f = (A+B`C)`, f =g`, g = A+B`C Use g to define the circuit configuration for the N-tree, and the input variables are those of the logic function, g; that is, A, B` and C By de Morgan rule on f, f = A`(B+C`), and use the expended form to define the circuit configuration for the P-tree, and the input variables are the complementary of the variables of the expended form. As f = A`(B+C`), the input variables are A`, B, and C`, the complementary of these signals are A, B` and C. Comparing the two approach, there is conflict between the two as the input variables are the same as A, B` and C. And the circuit configuration of P-tree and N-tree are in fact observe the de Morgan rule or duality. CMOS Gate Implementation It has to remind that the p-tree has to be connected to Vdd for pull-up the output and the n-tree has to be connected to GND for pull-down the output. It cannot use n-tree for the pull-up and p-tree for the pull-down as the full-swing property will not be maintained. i. e. logic ‘0’ ≠ zero volt logic ‘1’ ≠ Vdd volts Vdd P-tree Output Inputs N-tree