* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download V GS(on)

Survey

Document related concepts

Thermal runaway wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Stray voltage wikipedia , lookup

Current source wikipedia , lookup

Voltage optimisation wikipedia , lookup

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

Power inverter wikipedia , lookup

Power electronics wikipedia , lookup

Semiconductor device wikipedia , lookup

Opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Transcript

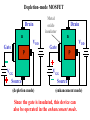

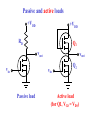

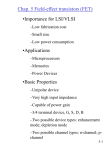

MALVINO Electronic PRINCIPLES SIXTH EDITION MOSFETs Chapter 14 Depletion-mode MOSFET Drain n Gate VDD p VGG Metal oxide insulator Drain n Gate VDD p VGG Source (depletion mode) Source (enhancement mode) Since the gate is insulated, this device can also be operated in the enhancement mode. MOSFETs • Current flows through a narrow channel between the gate and substrate. • SiO2 insulates the gate from the channel. • Depletion mode forces the carriers from the channel. • Enhancement mode attracts carriers into the channel. • E-MOSFETs are normally-off devices. n-channel E-MOSFET Drain n Gate p VGG n D VDD G S Source Gate bias enhances the channel and turns the device on. n-channel E-MOSFET • The p-substrate extends all the way to the silicon dioxide. • No n-channel exists between the source and drain. • This transistor is normally off when the gate voltage is zero. • A positive gate voltage attracts electrons into the p-region to create an n-type inversion layer and turns the device on. p-channel E-MOSFET Drain p Gate n VGG p D VDD G S Source Gate bias enhances the channel and turns the device on. p-channel E-MOSFET • The n-substrate extends all the way to the silicon dioxide. • No p-channel exists between the source and drain. • This transistor is normally off when the gate voltage is zero. • A negative gate voltage attracts holes into the n-region to create an p-type inversion layer and turns the device on. n-channel E-MOSFET drain curves +15 V Ohmic region Constant current region ID +10 V +5 V VDS VGS(th) n-channel E-MOSFET transconductance curve ID Ohmic ID(sat) Active VGS(th) VGS(on) VGS Gate breakdown • The SiO2 insulating layer is very thin. • It is easily destroyed by excessive gatesource voltage. • VGS(max) ratings are typically in tens of volts. • Circuit transients and static discharges can cause damage. • Some devices have built-in gate protection. Drain-source on resistance VGS = VGS(on) ID(on) Qtest RDS(on) = VDS(on) VDS(on) ID(on) Biasing in the ohmic region VGS = VGS(on) ID(on) ID(sat) +VDD Qtest RD Q VGS VDD ID(sat) < ID(on) when VGS = VGS(on) ensures saturation Passive and active loads +VDD +VDD RD Q1 vout vin vout vin Passive load Q2 Active load (for Q1, VGS = VDS) VGS = VDS produces a two-terminal curve +15 V +10 V ID VGS +5 V 5V 10 V VDS 15 V Active loading in a digital inverter +VDD RDQ1 = VDS(active) ID(active) Q1 vout +VDD 0V +VDD 0V vin Q2 It’s desirable that RDSQ2(on) << RDQ1. (The ideal output swings from 0 volts to +VDD.) Complementary MOS (CMOS) inverter +VDD Q1 (p-channel) +VDD 0V vin +VDD vout 0V Q2 (n-channel) PD(static) @ 0 CMOS inverter input-output graph vout VDD VDD 2 Crossover point PD(dynamic) > 0 VDD 2 VDD vin High-power EMOS • Use different channel geometries to extend ratings • Brand names such as VMOS, TMOS and hexFET • No thermal runaway • Can operate in parallel without current hogging • Faster switching due to no minority carriers dc-to-ac converter vac +VGS(on) 0V Power FET dc-to-dc converter vdc +VGS(on) 0V Power FET