* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Low Voltage Sequential Circuit With a Ring Oscillator Clock

Power over Ethernet wikipedia , lookup

Electrical ballast wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Electrification wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Electric power system wikipedia , lookup

Electrical substation wikipedia , lookup

Audio power wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Opto-isolator wikipedia , lookup

Utility frequency wikipedia , lookup

Three-phase electric power wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power engineering wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power MOSFET wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage regulator wikipedia , lookup

Stray voltage wikipedia , lookup

Surge protector wikipedia , lookup

Power inverter wikipedia , lookup

Buck converter wikipedia , lookup

Power electronics wikipedia , lookup

Power supply wikipedia , lookup

Alternating current wikipedia , lookup

Voltage optimisation wikipedia , lookup

Switched-mode power supply wikipedia , lookup

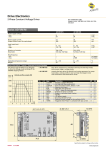

Low Voltage Sequential Circuit With a Ring Oscillator Clock ELEC 6270 Low power design of Electronic Circuits Spring, 2009 Presented by Mridula Allani Under the guidance of Dr. Vishwani Agrawal Dynamic Voltage and Frequency Scaling • Power Dissipation in electronic circuits. Ptotal pt (CL Vdd 2 fCLK ) + ISC Vdd Ileak Vd • The total power dissipation varies linearly with clock frequency and quadratically with supply voltage. • In idle periods a microprocessor is optimized to run at a lowvoltage and less than maximum speed to save power. • Generally, a power management unit controls this operation and reduces the Vdd and fclk after detecting an idle state. • Having an internally generated clock for such designs will decrease the burden on the power-management unit and save clock power . 2 Globally Asynchronous and Locally Synchronous Architecture Sequential Sequential Asynchronous Protocol Driven Communication Clock Generator Clock Generator • Power dissipation due to clock (appx. 40% of total) can be reduced using such architecture by designing clocks suitable for the local logic blocks. 3 Project Overview In_reg1 clear Sequence Generator (Binary Counter) In_reg2 count_enable Input Registers Combinational Logic (Ripple Adder) sum_out Output Registers cry_out cry_in ring_clock set Ring Oscillator Clock Distribution Network ENTITY local_synch IS PORT (set, clear, count_enable: IN STD_LOGIC; cry_out : OUT STD_LOGIC; sum_out: OUT STD_LOGIC_VECTOR( 3 DOWNTO 0 )); END local_synch; 4 Design Considerations • Ripple adder critical path delay = clock period of the ring oscillator. Td = n*(tpHL + tpLH) = 1/fclk tpHL, tpLH respectively are the fall and rise times of a single inverter Td critical delay of the ripple adder n = number of inverters in a ring oscillator and is odd fclk frequency of the ring oscillator • Assume the propagation delay for the high-to-low or low-to-high transitions of an inverter to be equal. tpHL + tpLH = 2*Tinv Td = n* 2*Tinv = 1/fclk Tinv is the inverter delay • Delays are calculated as the time between the 50% point of the input waveform and the 50% point of the output waveform. 5 Objectives • Design a ring oscillator clock to meet the critical path delay of the ripple adder. • Observe the variation in clock frequency of the ring oscillator with supply voltage and compare with the theoretical values. • Design a clock distribution network to distribute the clock generated by ring oscillator. • Design a binary counter to supply input vectors to the ripple adder. • Observe the variation of the average and peak powers and the delay of the complete system with supply voltage. • Find the optimum operation condition for the system from the power delay product. 6 Tools Used • ModelSim SE for behavioral modeling of the blocks. • Leonardo Spectrum for gate-level synthesis. • Design Architect for transistor-level synthesis. • Eldo Spice for voltage, delay, power and critical path delay. • ADK tsmc018 technology file for 0.18 um models. 7 Experimental Results • Schematic Diagram of the Whole System 8 Experimental Results • Inverter Average Power (uW) Maximum Voltage (V) Power (uW) 1.8 36.2283 134.6928 • Ring Delay(ps) Oscillator Average Energy = Power Maximum Power / Voltage Clock (uW) Power Delay(ns Clock Energy* (V) Frequency (uW) ) frequenc Delay(E(GHz) y(fJ) 24Js) 10.66338 1.8 0.5588 321.4063 413.1771 1.78947 575.172 1029.21 1.6 0.5071 216.509 1.4 0.4107 287.3531 1.97193 426.955 841.913 797.456 134.5032 182.2995 2.435 327.497 3 1.2 0.33023 73.6066 1.6 25.3686 95.0667 12.91967 1.4 17.1228 54.9572 17.03383 1.2 11.5631 37.004 23.38268 1.0 7.9412 23.5385 31.57895 0.8 7.9287 23.8102 55.85586 0.6 6.211 8.1721 128.6984 0.6 0.4 3.0039 0.194451 400.7 0.4 0.2 0.274565 0.000531 395541.6 0.2 1.0 0.8 109.5668 3.02817 222.895 674.948 151.479 0.2212 33.5073 63.5944 4.5211 7 684.855 892.950 0.1055 9.9393 20.1049 9.4782 94.211 7 3201.91 0.0168 0.9035546 7.8281 59.5348 53.783 78 50916.0 4.842E-04 0.0119375 0.117383 2065.22 24.654 75 4.54174E178260. 1443163 5.61E-06 05 0.000355 87 8.0958 .144 9 Experimental Results Energy*Delay (Ring Oscillator ) 3500 3000 2500 2000 Energy*Delay (Ring Oscillator ) 1500 1000 500 0 0 0.5 1 1.5 2 • From the graph, the optimum operation point is at VDD = 1V. 10 Theoretical Verification of Dependence of Voltage Scaling on the Frequency of Ring Oscillator • Variation of frequency with the supply voltage is given by the αpower law, given by (VDD – Vth)α f =k × ─────── α VDD •VDD is the supply voltage, Vth is the zero-bias threshold voltage, f is the clock frequency, k and α are constants. • Typical Vth for 0.18 um technology is 0.3932V. • ‘k’ and ‘α’ are calculated from the VDD and f values obtained for 1.8V and 1.6V supply voltage experimentally. • k = 1.097 G and α = 2.74 11 Comparison of Observed and Calculated Frequencies of Ring Oscillator •The experimental results obtained for the remaining voltage 1.4V to 0.2 V in steps of 0.2V are compared to the theoretical results and are tabulated as follows. Observed Clock Frequency Theoretical Clock Frequency . Voltage (V) (GHz) (GHz) 1.4 0.4107 0.4445 1.2 0.33023 0.3697 1.0 0.2212 0.2791 0.8 0.1055 0.1720 0.6 0.0168 0.0593 0.4 4.842E-04 0.1555E-04 0.2 5.61E-06 undefined •We observe that the calculated frequencies are found to be close to the theoretical results in almost all cases, but do not match the observed frequencies near and below threshold 12 voltages. Experimental Results • Ripple Voltage (V) 1.8 1.6 • Complete Adder Average Maximu Power m Power Critical Average (uW) (uW) Delay(ns) Power*Del ay 6.284 4.8427 928.2791 636.8054 1.0781 1.24825 System Clock Average Voltage (V) Frequency Power (uW) (GHz) Maximum Power Critical (uW) Delay(ns) Critical Delay of Ripple Adder(ns) 6.775 1.8 0.5588 1.6 0.5071 1.4 0.4107 1.2 0.33023 1.0 0.2212 0.8 0.1055 0.6 0.0168 6.045 1.4 3.5987 413.6859 1.51913 5.467 1.2 2.5949 272.8673 2.00965 5.2148 1.0 1.7407 179.5037 3.02571 5.2668 0.8 1.0849 56.7458 6.19 6.7155 0.6 0.562447 16.7108 35.187 19.79 0.4 0.031435 0.431696 1456.19 45.775 0.4 4.842E-04 0.2 0.000582 0.001475 105682.1 61.506 0.2 5.61E-06 13 Experimental Results Power*Delay (Ripple Carry Adder) 70 60 50 40 Power*Delay (Ripple Carry Adder) 30 20 10 0 0 0.5 1 1.5 2 • From the graph, the optimum operation point is at VDD = 1V. 14 Conclusions • The power-delay product of the ring oscillator was monotonically decreasing, but its energydelay product had a minimum at 1V supply voltage. • The power-delay product of ripple carry adder is minimum at 1V supply voltage. • Thus, VDD = 1V is the optimum supply voltage. • The whole system could not be simulated due to convergence errors in ELDO. 15 Future Work • The convergence errors need to be resolved. • This experiment has to be repeated for high leakage technologies and similar trends need to be compared. 16 References • Dr Agrawal’s class slides for ELEC6270, Spring 2009. • Power Management and Dynamic Voltage Scaling: Myths and Facts, David Snowdon, Sergio Ruocco and Gernot Heiser • A Deterministic Globally Asynchronous Locally Synchronous Microprocessor Architecture, Matthew Heath and Ian Harris • http://www.wikipedia.org/ 17