* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Multiplexing and Demultiplexing

Valve RF amplifier wikipedia , lookup

Digital electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Microcontroller wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

UniPro protocol stack wikipedia , lookup

Opto-isolator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

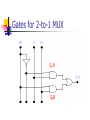

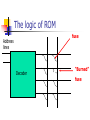

Multiplexing and Demultiplexing Multiplexing There are several data inputs and one of them is routed to the output In addition to data inputs, there must be select inputs How many select pins are needed? Like selecting a television channel Depends on number of inputs Multiplexer aka MUX Truth table for 2-to-1 MUX Select S0 0 0 Data A 0 0 B 0 1 Out 0 0 0 0 1 1 1 0 0 1 0 1 1 0 1 1 1 0 1 1 1 0 1 1 0 1 Algebra for 2-to-1 MUX Take expressions for 1’s found in truth table SAB + SAB + SAB + SAB SA(B+B) + S(A+A)B This can be factored as follows (B+B) = 1 Not B or B, doesn’t care about B SA + SB Gates for 2-to-1 MUX S0A S0B 4-to-1 MUX: truth table Select Data S1 S0 A B C D Out 0 0 A B C D A 0 1 A B C D B 1 0 A B C D C 1 1 A B C D D 4-to-1 MUX: gate version Addresses Each data input is assigned to a specific state of the select input The state can be interpreted as binary numbers E.g. low-low, low-high, high-low, high-high 00, 01, 10, 11 Two select Four addresses And these numbers are thought of as the “addresses” of the input 4-to-1 MUX: truth table (revisited) Select Data S1 S0 D0 D1 D2 D3 Out 0 0 D0 D1 D2 D3 D0 0 1 D0 D1 D2 D3 D1 1 0 D0 D1 D2 D3 D2 1 1 D0 D1 D2 D3 D3 Demultiplexing one input is routed to one of several outputs In addition to data input, there must be select inputs Like mail may be sent to any number of recipients To select from 2N data outputs requires N select inputs Demultiplexer aka DeMUX 1-to-4 DeMux: Truth table Select S1 S0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Data A 0 1 0 1 0 1 0 1 O0 0 1 0 0 0 0 0 0 Output O1 O2 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 O3 0 0 0 0 0 0 0 1 1-to-4 DeMUX: gate version Decoder A variation on the previous circuit is to have no input data the selected output will be high, the others low This can be used to activate a control pin on the selected part of circuit 1-to-4 Decode: Truth table Select Output S1 S0 O0 O1 O2 O3 0 0 1 0 1 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 1-to-4 Decode: gates Decoder plus registers = RAM Memory Address Register (MAR) holds an address associated with memory Memory Data Register (MDR) holds data for writing to memory Memory is a sequence of registers and a decoder Decoder output is connected to control pins (load in this example) of the RAM Decoder plus registers = RAM Load pins MAR Decoder MDR The logic of ROM fuse Address lines Decoder “Burned” fuse Logic of ROM (Cont.) Fuses connect output of decoder to output of ROM Normal voltage and current does not burn (“blow”) the fuse So when the selected decoder output is high, all ROM output lines to which it is connected are also high Logic of ROM (Cont.) Higher voltage and current will break the connections They are applied selectively to break certain connections The ROM output is not affected by the decoder output if the connection is broken (Implementation may be different, but this is the basic logic)