* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download HCF4527B

Solar micro-inverter wikipedia , lookup

Scattering parameters wikipedia , lookup

Linear time-invariant theory wikipedia , lookup

Stray voltage wikipedia , lookup

Current source wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power inverter wikipedia , lookup

Control system wikipedia , lookup

Alternating current wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Two-port network wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Voltage regulator wikipedia , lookup

Integrating ADC wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Current mirror wikipedia , lookup

Schmitt trigger wikipedia , lookup

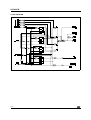

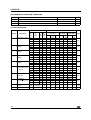

HCF4527B BCD RATE MULTIPLEXER ■ ■ ■ ■ ■ ■ ■ ■ CASCADABLE IN MULTIPLES OF 4-BITS SET TO 9 INPUT AND 9 DETECT OUTPUT QUIESCENT CURRENT SPECIFIED UP TO 20V STANDARDIZED SYMMETRICAL OUTPUT CHARACTERISTICS 5V, 10V AND 15V PARAMETRIC RATINGS INPUT LEAKAGE CURRENT II = 100nA (MAX) AT VDD = 18V TA = 25°C 100% TESTED FOR QUIESCENT CURRENT MEETS ALL REQUIREMENTS OF JEDEC JESD13B "STANDARD SPECIFICATIONS FOR DESCRIPTION OF B SERIES CMOS DEVICES" DESCRIPTION HCF4527B is a monolithic integrated circuit fabricated in Metal Oxide Semiconductor technology available in DIP package. This device is a low power 4-bit digital rate multiplier that provides an output pulse rate which is the clock input pulse rate multiplied by 1/10 times the BCD input. For example, when the BCD DIP ORDER CODES PACKAGE TUBE DIP HCF4527BEY T&R input is 8, there will be 8 output pulses for every 10 input pulses. This device may be used to perform arithmetic operations (add, subtract, divide, raise to a power), solve algebraic and differential equations, generate natural logarithms and trigonometric functions, A/D and D/A conversion, and frequency division. PIN CONNECTION October 2002 1/12 HCF4527B INPUT EQUIVALENT CIRCUIT FUNCTIONAL DIAGRAM 2/12 PIN DESCRIPTION PIN No SYMBOL NAME AND FUNCTION 14, 15, 2, 3 10 12 5, 6 9 11 4 13 7 1 BCD Rate Select Inputs Strobe Input Cascade Rate Outputs Clock Input Inhibit Input (Carry) Set Input Clear Input Inhibit Out (Carry) Output 8 A, B, C, D STROBE CASCADE OUT, OUT CLOCK INHIBIT IN SET T0 "9" CLEAR INHIBIT OUT "9" OUT VSS 16 VDD Positive Supply Voltage Negative Supply Voltage HCF4527B TRUTH TABLE INPUTS OUTPUTS Number of Pulses or Logic Level Number of Pulses or Output Logic Level D C B A CLK INH IN STR CAS CLR SET OUT OUT INH OUT "9" OUT L L L L L L L L H H H H H H H H X X X H L X L L L L H H H H L L L L H H H H X X X X X X L L H H L L H H L L H H L L H H X X X X X X L H L H L H L H L H L H L H L H X X X X X X 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 L L L L L L L L L L L L L L L H L L L L L L L L L L L L L L L L L L L L L L H L L L L L L L L L L L L L L L L L L L L L L L H L L L L L L L L L L L L L L L L L L L L L L H H L L L L L L L L L L L L L L L L L L L L L L H L 1 2 3 4 5 6 7 8 9 8 9 8 9 8 9 ** L H 10 L L H 1 2 3 4 5 6 7 8 9 8 9 8 9 8 9 ** H * 10 H H 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 H 1 1 H H L 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 ** 1 1 L L H X : Don’t Care ** : Depends on internal state of counter. * : Output same as the first 16 lines of this truth table (depending on value of A, B, C, D) 3/12 HCF4527B LOGIC DIAGRAM 4/12 HCF4527B TIMING CHART ABSOLUTE MAXIMUM RATINGS Symbol VDD Parameter Supply Voltage VI DC Input Voltage II DC Input Current PD Value Unit -0.5 to +22 V -0.5 to VDD + 0.5 ± 10 V mA 200 100 mW mW Top Power Dissipation per Package Power Dissipation per Output Transistor Operating Temperature -55 to +125 °C Tstg Storage Temperature -65 to +150 °C Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltage values are referred to VSS pin voltage. 5/12 HCF4527B RECOMMENDED OPERATING CONDITIONS Symbol VDD Parameter Value Supply Voltage VI Input Voltage Top Operating Temperature Unit 3 to 20 V 0 to VDD V -55 to 125 °C DC SPECIFICATIONS Test Condition Symbol IL VOH VOL VIH VIL IOH IOL IOL II CI Parameter Quiescent Current High Level Output Voltage Low Level Output Voltage VI (V) 0/5 0/10 0/15 0/20 0/5 0/10 0/15 5/0 10/0 15/0 High Level Input Voltage Low Level Input Voltage Output Drive Current (Source) Q, Q, Q’ CLD Output Sink Current Q Output Sink Current Q, Q’, CLD Input Leakage Current Input Capacitance VO (V) 0/5 0/5 0/10 0/15 0/5 0/10 0/15 0/5 0/10 0/15 0/18 0.5/4.5 1/9 1.5/13.5 4.5/0.5 9/1 13.5/1.5 2.5 4.6 9.5 13.5 0.4 0.5 1.5 0.4 0.5 1.5 Value |IO| VDD (µA) (V) <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 <1 Any Input Any Input 5 10 15 20 5 10 15 5 10 15 5 10 15 5 10 15 5 5 10 15 5 10 15 5 10 15 18 TA = 25°C Min. Typ. Max. 0.04 0.04 0.04 0.08 5 10 20 100 4.95 9.95 14.95 -40 to 85°C -55 to 125°C Min. Min. 150 300 600 3000 4.95 9.95 14.95 0.05 0.05 0.05 4.95 9.95 14.95 3.5 7 11 1.5 3 4 -3.2 -1 -2.6 -6.8 4 10.4 27.2 1 2.6 6.8 ±0.1 5 7.5 0.05 0.05 0.05 1.5 3 4 -1.1 -0.36 -0.9 -2.4 1.43 3.74 9.52 0.36 0.9 2.4 The Noise Margin for both "1" and "0" level is: 1V min. with VDD =5V, 2V min. with VDD=10V, 2.5V min. with VDD=15V 6/12 V V 1.5 3 4 ±1 µA V 3.5 7 11 -1.1 -0.36 -0.9 -2.4 1.43 3.74 9.52 0.36 0.9 2.4 ±10-5 Max. 150 300 600 3000 0.05 0.05 0.05 3.5 7 11 -1.36 -0.44 -1.1 -3.0 1.74 4.42 11.56 0.44 1.1 3.0 Max. Unit V mA mA mA ±1 µA pF HCF4527B DYNAMIC ELECTRICAL CHARACTERISTICS (Tamb = 25°C, CL = 50pF, RL = 200KΩ, tr = tf = 20 ns) Test Condition Symbol Parameter tPLH, tPHL Propagation Delay Time : Clock to Output tPLH, tPHL Propagation Delay Time : Clock or Strobe to Output tPLH tPHL Propagation Delay Time : Clock to Inhibit Output Propagation Delay Time : Clock to Inhibit Output tPLH, tPHL Propagation Delay Time : Clear to Output tPLH, tPHL Propagation Delay Time : Clock to "9" or "1" Q Output tPLH, tPHL Propagation Delay Time : Cascade to Output tPLH, tPHL Propagation Delay Time : Inhibit Input to Inhibit Output tPLH, tPHL Propagation Delay Time : Set to Output tTHL, tTLH Transition Time fCL tW tr, tf tW tsetup Maximum Clock Frequency Clock Pulse Width Clock Rise or Fall Time Set or Clear Pulse Width Inhibit Input Setup Time VDD (V) 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 5 10 15 Value (*) Unit Min. Typ. Max. 220 110 90 300 150 120 640 290 200 500 200 150 760 550 260 600 250 180 180 90 70 260 120 90 660 300 220 200 100 80 1.2 2.5 3.5 330 170 100 110 55 45 150 75 60 320 145 100 250 100 75 380 175 130 300 125 90 90 45 35 130 60 45 330 150 110 100 50 40 2.4 5 7 165 85 50 80 45 30 50 20 10 ns ns ns ns ns ns ns ns ns MHz ns 15 15 15 160 90 60 100 40 20 ns µs ns ns 7/12 HCF4527B Test Condition Symbol tR tR tR Parameter Inhibit Input Removal Time Set Removal Time Clear Removal Time Value (*) VDD (V) Min. Typ. 5 10 15 5 10 15 5 10 15 240 130 110 150 80 50 60 40 30 120 65 55 75 40 25 30 20 15 Unit Max. ns ns ns (*) Typical temperature coefficient for all VDD value is 0.3 %/°C. APPLICATION NOTE : For fractional multipliers with more than one digit, HCF4527B may be cascaded in two different modes: The ADD mode and the MULTIPLY mode (see figure 1 and 2). When two units are cascaded in ADD mode and programmed to 9 and 4 respectively, the more significant unit will have 9 output pulses for every 10 input pulses and the other will have 4 output pulses for every 100 input pulses for a total of : 9 4 94 + = 10 100 100 In the multiply mode, the fraction programmed into the first rate multiplier is multiplied by the fraction programmed into the second one : If N1 = 9 and N 2 =4 4 fOUT2 = fOUT1 10 9 fOUT1 = fCLOCK 10 4 9 36 fOUT2 = x ( fCLOCK ) = fCLOCK 10 10 100 Therefore 36 output pulses for every 100 clock input pulses Two HCF4527B Cascaded in the ADD mode with a Preset Number 8/12 HCF4527B Two HCF4527B Cascaded in the MULTIPLY Mode with a Preset Number TEST CIRCUIT CL = 50pF or equivalent (includes jig and probe capacitance) RL = 200KΩ RT = ZOUT of pulse generator (typically 50Ω) 9/12 HCF4527B WAVEFORM : PROPAGATION DELAY TIMES (f=1MHz; 50% duty cycle) 10/12 HCF4527B Plastic DIP-16 (0.25) MECHANICAL DATA mm. inch DIM. MIN. a1 0.51 B 0.77 TYP MAX. MIN. TYP. MAX. 0.020 1.65 0.030 0.065 b 0.5 0.020 b1 0.25 0.010 D 20 0.787 E 8.5 0.335 e 2.54 0.100 e3 17.78 0.700 F 7.1 0.280 I 5.1 0.201 L Z 3.3 0.130 1.27 0.050 P001C 11/12 HCF4527B Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. © The ST logo is a registered trademark of STMicroelectronics © 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. © http://www.st.com 12/12