* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download High Speed Op-amp Design

Three-phase electric power wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power inverter wikipedia , lookup

Utility frequency wikipedia , lookup

Audio power wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Mains electricity wikipedia , lookup

Electronic engineering wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Buck converter wikipedia , lookup

Negative feedback wikipedia , lookup

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Alternating current wikipedia , lookup

Regenerative circuit wikipedia , lookup

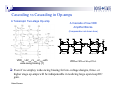

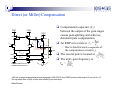

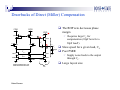

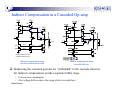

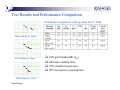

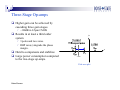

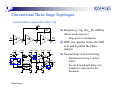

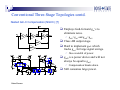

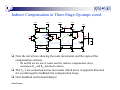

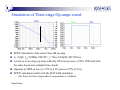

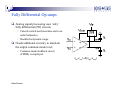

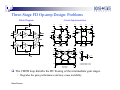

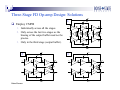

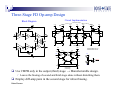

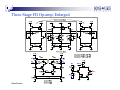

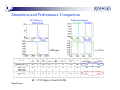

High Speed Op-amp Design: Compensation and Topologies for Two and Three Stage Designs R. Jacob Baker and Vishal Saxena Department of Electrical and Computer Engineering Boise State University 1910 University Dr., MEC 108 Boise, ID 83725 [email protected] and [email protected] Abstract : As CMOS technology continues to evolve, the supply voltages are decreasing while at the same time the transistor threshold voltages are remaining relatively constant. Making matters worse, the inherent gain available from the nano-CMOS transistors is dropping. Traditional techniques for achieving high gain by vertically stacking (i.e. cascoding) transistors becomes less useful in sub-100nm processes. Horizontal cascading (multistage) must be used in order to realize op-amps in low supply voltage processes. This seminar discusses new design techniques for the realization of multi-stage op-amps. Both single- and fully-differential op-amps are presented where low power, small VDD, and high speed are important. The proposed, and experimentally verified, opamps exhibit significant improvements in speed over the traditional op-amp designs while at the same time having smaller layout area. Baker/Saxena Outline Introduction Two-stage Op-amp Compensation Multi-stage Op-amp Design Multi-stage Fully-Differential Op-amps Conclusion Baker/Saxena Op-amps and CMOS Scaling The Operational Amplifier (op-amp) is a fundamental building block in Mixed Signal design. 9 Employed profusely in data converters, filters, sensors, drivers etc. Continued scaling in CMOS technology has been challenging the established paradigms for op-amp design. With downscaling in channel length (L) 9 Transition frequency increases (more speed). 9 Open-loop gain reduces (lower gains). 9 Supply voltage is scaled down (lower headroom) [1]. Baker/Saxena CMOS Scaling Trends VDD is scaling down but VTHN is almost constant. 9 Design headroom is shrinking faster. Transistor open-loop gain is dropping (~10’s in nano-CMOS) 9 Results in lower op-amp open-loop gain. But we need gain! Random offsets due to device mismatches. [3], [4]. Baker/Saxena Integration of Analog into Nano-CMOS? Design low-VDD op-amps. 9 Replace vertical stacking (cascoding) by horizontal cascading of gain stages (see the next slide). Explore more effective op-amp compensation techniques. Offset tolerant designs. Also minimize power and layout area to keep up with the digital trend. Better power supply noise rejection (PSRR). Baker/Saxena Cascoding vs Cascading in Op-amps A Telescopic Two-stage Op-amp A Cascade of low-VDD Amplifier Blocks. (Compensation not shown here) VDD VDD VDD VDD VDD VDD VDD 2 n-1 1 vm vp n vout CL VDDmin>4Vovn+Vovp+VTHP with wide-swing biasing. [1] Vbiasn Vbiasn Vbiasn Stage 1 Stage 2 Stage (n-1) Stage n VDDmin=2Vovn+Vovp+VTHP. Even if we employ wide-swing biasing for low-voltage designs, three- or higher stage op-amps will be indispensable in realizing large open-loop DC gain. Baker/Saxena TWO-STAGE OP-AMP COMPENSATION Baker/Saxena Direct (or Miller) Compensation VDD Compensation capacitor (Cc) between the output of the gain stages causes pole-splitting and achieves dominant pole compensation. An RHP zero exists at VDD VDD M3 M4 M7 1 220/2 750Ω vm M1 M2 vp iC ff M6TL M6BL iC fb CC 10pF 2 Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. M6TR M8T M6BR M8B CL 30pF Vbias3 Vbias4 vout 100/2 100/2 9 Due to feed-forward component of the compensation current (iC). The second pole is located at The unity-gain frequency is x10 All the op-amps presented have been designed in AMI C5N 0.5μm CMOS process with scale=0.3 μm and Lmin=2. The op-amps drive a 30pF off-chip load offered by the test-setup. Baker/Saxena Drawbacks of Direct (Miller) Compensation VDD The RHP zero decreases phase margin VDD VDD M3 M4 M7 1 9 Requires large CC for compensation (10pF here for a 30pF load!). 220/2 vm M1 M2 vp CC vout 2 10pF M6TL M6BL Vbias3 M6TR M8T Vbias4 M6BR Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. Baker/Saxena CL 30pF 100/2 100/2 M8B Slow-speed for a given load, CL. Poor PSRR 9 Supply noise feeds to the output through CC. Large layout size. x10 Indirect Compensation VDD The RHP zero can be eliminated by blocking the feed-forward compensation current component by using VDD VDD VDD M3 vm M4 M1 M9 1 ic M2 MCG vp M7 220/2 Cc 2 A vout CL 30pF M6TL M6BL Vbias3 M6TR M10T M8T M10B M8B 100/2 Vbias4 M6BR Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. 100/2 x10 An indirect-compensated op-amp using a common-gate stage. Baker/Saxena 9 A common gate stage, 9 A voltage buffer, 9 Common gate “embedded” in the cascode diff-amp, or 9 A current mirror buffer. Now, the compensation current is fedback from the output to node-1 indirectly through a low-Z node-A. Since node-1 is not loaded by CC, this results in higher unity-gain frequency (fun). Indirect Compensation in a Cascoded Op-amp VDD VDD M4T M3T A Vbias2 M3B ic M4B VDD M7 110/2 1 vm M1 M2 vp CC 2 1.5pF Vbias3 M6TL M6TR M8T M6BR M8B Vbias4 M6BL CC vout CL 30pF vm vp vout CL 50/2 50/2 Unlabeled NMOS are 10/2. Unlabeled PMOS are 44/2. Indirect-compensation using cascoded current mirror load. Indirect-compensation using cascoded diff-pair. Employing the common gate device “embedded” in the cascode structure for indirect compensation avoids a separate buffer stage. 9 Lower power consumption. 9 Also voltage buffer reduces the swing which is avoided here. Baker/Saxena Analytical Modeling of Indirect Compensation The compensation current (iC) is indirectly fed-back to node-1. Block Diagram vout ic ≈ 1 sCc + Rc RC is the resistance attached to node-A. Small signal analytical model Baker/Saxena Derivation of the Small-Signal Model Resistance roc is assumed to be large. The small-signal model for a common gate indirect compensated opamp topology is approximated to the simplified model seen in the last slide. gmc>>roc-1, RA-1, CC>>CA Baker/Saxena Analytical Results for Indirect Compensation jω −ω un σ p3 p2 z1 p1 Pole-zero plot Pole p2 is much farther away from fun. 9 Can use smaller gm2=>less power! LHP zero improves phase margin. Much faster op-amp with lower power and smaller CC. Better slew rate as CC is smaller. Baker/Saxena LHP zero Indirect Compensation Using Split-Length Devices As VDD scales down, cascoding is becoming tough. Then how to realize indirect compensation as we have no low-Z node available? Solution: Employ split-length devices to create a low-Z node. 9 Creates a pseudo-cascode stack but its really a single device. In the NMOS case, the lower device is always in triode hence node-A is a low-Z node. Similarly for the PMOS, node-A is low-Z. NMOS Baker/Saxena PMOS Split-length 44/4(=22/2) PMOS layout Split-Length Current Mirror Load (SLCL) Op-amp VDD VDD VDD M4T M3T ic A M3B 220/2 M7T M4B 220/2 1 vm M1 M2 M7B vp CC 2pF M6TL M6BL Vbias3 M6TR M8T M6BR M8B Vbias4 vout 2 CL 30pF 50/2 50/2 Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. The current mirror load devices are split-length to create low-Z node-A. Here, fun=20MHz, PM=75° and ts=60ns. Baker/Saxena Frequency Response ts Small step-input settling in follower configuration SLCL Op-amp Analysis 1 gmp 1 gmp gm1v s + A - 2 1 gmp g m1 − v gmp s Cc Cc vout 1 id2 − A id1 vs vs 2 2 vout 1 id1 2 2 vs CL 2 v=0 (a) (b) rop 1 Cc A 2 + gm1v s 2 + + vsgA v1 R1 C1 - gmpvsgA - − 1 gmp 1 gmp CA gm2v1 gm 1 v gmp s 2 + + Cc v1 R1 C1 ic gm2v1 - Baker/Saxena R2 1 gmp vout C2 - ic ≈ vout 1 1 + sCc gmp R2 vout C2 - 1 g m1v s CL Here fz1=3.77fun 9 LHP zero appears at a higher frequency than fun. Split-Length Diff-Pair (SLDP) Op-amp VDD VDD VDD M3 M4 M7 110/2 1 vm M1T M2T 20/2 20/2 vp ic vout A 20/2 M1B M6TL M6BL 2pF 20/2 CC 2 CL 30pF M2B Vbias3 Vbias4 M6TR M8T M6BR M8B 50/2 Frequency Response 50/2 Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. The diff-pair devices are split-length to create low-Z node-A. Here, fun=35MHz, PM=62°, ts=75ns. Better PSRR due to isolation of node-A from the supply rails. Baker/Saxena Small step-input settling in follower configuration SLDP Op-amp Analysis vout vs − vout vs 2 2 1 gmn vs 2 1 gmn gmn v s 1 gmn 4 id 2 = − Cc 1 ron A 2 + 1 gmn + + vgs1 gmnvgs1 - 1 gmn vA CA - gmn v s R1 C1 R2 gm2v1 4 vs - 2 1 2 + gmn v s 2 Cc v1 R1 C1 ic gm2v1 ic ≈ Baker/Saxena R2 1 gmn + vout C2 - vout 1 1 + sCc gmn vout C2 Here fz1=0.94fun, 9 LHP zero appears slightly before fun and flattens the magnitude response. 9 This may degrade the phase margin. Not as good as SLCL, but is of great utility in multi-stage op-amp design due to higher PSRR. Test Chip 1: Two-stage Op-amps Miller SLCL Indirect 3-Stage Indirect SLDP Indirect Miller with Rz AMI C5N 0.5μm CMOS, 1.5mmX1.5mm die size. Baker/Saxena Test Results and Performance Comparison Performance comparison of the op-amps for CL=30pF. Miller with Rz (ts=250ns) SLCL Indirect (ts=60ns) SLDP Indirect (ts=75ns) Baker/Saxena 10X gain bandwidth (fun). 4X faster settling time. 55% smaller layout area. 40% less power consumption. MULTI-STAGE OP-AMP DESIGN Baker/Saxena Three-Stage Op-amps Higher gain can be achieved by cascading three gain stages. 9 ~100dB in 0.5μm CMOS Results in at least a third order system jω 9 3 poles and two zeros. 9 RHP zero(s) degrade the phase margin. Hard to compensate and stabilize. Large power consumption compared to the two-stage op-amps. σ − ω un Pole-zero plot Baker/Saxena Biasing of Multi-Stage Op-amps Diff-amps should be employed in inner gain stages to properly bias second and third gain stages Robust Biasing 9 Current in third stage is precisely set. 9 Robust against large offsets. 9 Boosts the CMRR of the opamp (needed). Common source second stage should be avoided. 9 Will work in feedback configuration but will have offsets in nano-CMOS processes. Fallible Biasing Baker/Saxena Conventional Three-Stage Topologies Nested Miller Compensation (NMC) [6] Requires p3=2p2=4ωun for stability (Butterworth response) 9 Huge power consumption RHP zero appears before the LHP zero and degrades the phase margin. Second stage is non-inverting 9 Implemented using a current mirror. 9 Excess forward path delay (not modeled or discussed in the literature). Baker/Saxena Conventional Three-Stage Topologies contd. Nested Gm-C Compensation (NGCC) [7] Employs feed-forward gm’s to eliminate zeros. 9 gmf1=gm1 and gmf2=gm2 Class AB output stage. Hard to implement gmf1 which tracks gm1 for large signal swings. 9 Also wasteful of power. gmf2 is a power device and will not always be equal to gm2. 9 Compensation breaks down. Still consumes large power. Baker/Saxena Conventional Three-Stage Topologies contd. Transconductance with Capacitive Feedback Compensation (TCFC) [14] Four poles and double LHP zeros 9 One LHP zero z1 cancels the pole p3. 9 Other LHP zero z2 enhances phase margin. VDD VDD VDD VB1 VDD gm2/2 VB7 gmf VB5 VB2 CC2 VB6 3 gmt 2 VB3 VB4 1:2 Baker/Saxena gm3 Set p2=2ωun for PM=60°. Relatively low power. Still design criterions are complex. Complicated bias circuit. 9 More power. CC1 vp gm1 VDD VDD 1 vm vout Excess forward path delay. Three-Stage Topologies: Latest in the literature Reverse Nested Miller with Voltage Buffer and Resistance (RNMC-VBR) [8] Employs reverse nesting of compensation capacitors 9 Since output is only loaded by only CC2, results in potentially higher fun. 9 Third stage is always non-inverting. VDD VDD VDD vp gm1 20uA 3 vout 2 Cc2 CL gm3 gmVB 1 gm2 Baker/Saxena VDD Cc1 RC1 vm VDD VDD gmf Uses pole-zero cancellation to realize higher phase margins. Excess forward path delay. Biasing not robust against process variations. How do you control the current in the output buffer? Three-Stage Topologies: Latest in the literature contd. Active Feedback Frequency Compensation (AFFC) [9] Reversed nested with elimination of RHP zero. High-Gain Block (HGB) Cm Input Block vs -A1 +A2 1 2 -A3 -gmf Ca +gma High-Speed Block (HSB) vout 3 9 High gain block (HGB) realizes gain by cascading stages. 9 High speed block (HSB) implements compensation at high frequencies. Complex design criterions. Excess forward path delay. Again, uses a non-inverting gain stage. Employs a complicated bias circuit. 9 More power consumption. Baker/Saxena Three-Stage Topologies: Latest in the literature contd. Various topologies have been recently reported by combining the earlier techniques. 9 RNMC feed-forward with nulling resistor (RNMCFNR) [17]. 9 Reverse active feedback frequency compensation (RAFFC) [17]. Further improvements are required in 9 Eliminating excess forward path delay arising due to the compulsory noninverting stages. 9 Robust biasing against random offsets in nano-CMOS. 9 Further reduction in power and circuit complexity. 9 Better PSRR. Baker/Saxena Indirect Compensation in Three-Stage Op-amps Indirectly feedback the compensation currents ic1 and ic2. 9 Reversed Nested Thus named RNIC. Employ diff-amp stages for robust biasing and higher CMRR. Use SLDP for higher PSRR. Minimum forward path delay. No compulsion on the polarity of gain stages. 9 Can realize any permutation of stage polarities by just changing the sign of the fed-back compensation current using ‘fbr’ and ‘fbl’ nodes. Low-voltage design. Note Class A (we’ll modify after theory is discussed). Baker/Saxena VDD VDD VDD VDD VDD 2 -ve 1 vm fbl +ve fbr ic1 fbl vp vout Cc1 3 ic2 fbr Cc2 Vbiasn CL Indirect Compensation in Three-Stage Op-amps contd. VDD VDD VDD VDD VDD 2 -ve 1 vm fbl +ve fbr ic1 fbl vp vout Cc1 3 ic2 CL fbr Cc2 Vbiasn Note the red arrows showing the node movements and the signs of the compensation currents. 9 fbr and fbl are the low-Z nodes used for indirect compensation (have resistances Rc1 and Rc2 attached to them). The CC’s are connected across two-nodes which move in opposite direction for overall negative feedback the compensation loops. Note feedback and forward delays! Baker/Saxena Analysis of the Indirect Compensated 3-Stage Op-amp Plug in the indirect compensation model developed for the two-stage opamps. i c1 ≈ v2 1 sCc1 + Rc 1 ic 2 ≈ Two LHP zeros Baker/Saxena vout 1 sCc 2 + Rc 2 Four non-dominant poles. Pole-zero Cancellation Poles p4,5 are parasitic conjugated poles located far away in frequency. 9 Appear due to the loading of the nodes fbr and fbl. The small signal transfer function can be written as The quadratic expression in the denominator describing the poles p2 and p3 can be canceled by the numerator which describes the LHP zeros. 9 Results in LHP zeros z1 and z2 canceling the poles p2 and p3 resp. The resulting expression looks like a single pole system for low frequencies. →Phase margin close to 90°. Baker/Saxena Pole-zero Cancellation contd. jω Place pole-zero doublets (p2-z1 and p3z2) out of fun for clean transients. 9 i.e. fp2, fp3 > fun. Best possible pole-zero arrangement for low power design. Results into design equations independent of parasitics (C3≈CL here). Rc1 and Rc2 are realized by adding poly R’s in series with CC1 and CC2. 9 Also Rc1, Rc2≥Rc0, the impedance attached to the low-Z nodes fbr/fbl. Robust against even 50% process variations in R’s and C’s as long as the pole-zero doublets stay out of fun. Baker/Saxena σ −ω un Design Equations Pole-zero cancelled Class-A Op-amp A Here, the poly resistors are estimated as Low power, simple, robust and manufacturable topology*. The presented three-stage op-amps have been designed with transient and SR performances to be comparable to their two-stage counterparts. Baker/Saxena Pole-zero cancelled Class-AB Op-amp 1 A dual-gain path, low-power Class-AB op-amp topology (RNIC-1). The design equation for Rc1 is modified as Baker/Saxena Pole-zero cancelled Class-AB Op-amp 2 VDD M4 VDD VDD M8 M5 Vbiasp M9 VDD M10 1 M1T 20/2 fbl vm VDD VDD 20/2 M2T vp fbr 20/2 20/2 M1B M2B 220/2 66/2 M5 fbl R1c 7.65K 1p Vbiasn M3L Vpcas 66/2 M6 Cc1 Vncas MFCN MFCP 11/2 10/2 2 fbr R2c Cc2 4.08K 2p M11 Vbiasn M3R M7L M7R Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. A single-gain path, Class-AB op-amp topology for good THD performance. 9 Floating current source for biasing the output buffer. 9 Here, Vncas= 2VGS and Vpcas=VDD − 2VSG. 9 Note the lack of gratuitous forward delay. Baker/Saxena vout 3 CL 100/2 30pF Simulation of Three-stage Op-amps Bode Diagram Magnitude (dB) 100 50 0 -50 -100 Phase (deg) -150 0 -45 -90 -135 -180 -225 2 10 4 10 6 10 8 10 10 10 Frequency (Hz) Analytical model of the Class-AB (RNIC-1) topology is simulated in MATLAB. The pole-zero plot illustrates the double pole-zero cancelation (collocation). 9 p4 and p5 are parasitic poles located at frequencies close to that of the fT limited (or mirror) poles. Here, fun≈30MHz and PM=90° for CL=30pF. Baker/Saxena Simulation of Three-stage Op-amps contd. SPICE simulation of the same Class AB op-amp. CL=30pF: fun=30MHz, PM≈88°, ts=70ns, 0.84mW, SR=20V/μs. As fast as a two-stage op-amp with only 20% more power, at 50% VDD and with the same layout area (simpler bias circuit). Operates at VDD as low as 1.25V in a 5V process (25% of VDD). SPICE simulation match with the MATLAB simulation 9 Our theory for three-stage indirect compensation is validated. Baker/Saxena Chip 2: Low-VDD 3-Stage Op-amps Best Performance AMI C5N 0.5μm CMOS, 1.5mmX1.5mm die size. Baker/Saxena Performance Comparison Figures of Merit 9 9 9 9 FoMS=funCL/Power FoML=SR.CL/Power IFoMS=funCL/IDD IFoML=SR.CL/IDD RNIC op-amp designed for 500pF load for a fair comparison. FoMs>2X than state-ofthe-art at VDD=3V. Comparable performance even at lower VDD=2V. Practical, stable and production worthy. Baker/Saxena Performance Comparison contd. 60000 50000 40000 FOM_S FOM_L 30000 IFOM_S 20000 IFOM_L 10000 C M C C FN R D FC FC AF F AC C B C F TC FC R DP N M ZC C VB F SM NR R FF N M C C F R NR R A N F IC RA F C R - 2 ( FF N IC Thi C L R N -3 s w P IC (T o R -2A hi s rk ) N IC (T wo -3 hi rk A sw ) (T hi ork s ) w or k) G N N M N M C 0 Baker/Saxena Higher performance figures than state-of-the-art. 10X faster settling. Better phase margins. Layout area same or smaller. Flowchart for RNIC Op-amp Design Start with the initial specifications on fun, CL, Av, and SR. Split DC gain AOLDC across A1, A2 and A3. Select the overdrive (% of VDD) which will set VGS, fT and transistor gain gm*ro. Identify gm1. Can initially set gm2 equal to gm1 or a to lower value. Select Cc2 = gm1/fun Select Cc1 and gm3 such that the p2-z1 and p3-z2 doublet locations are outside fun. Move the corresponding pi-zj doublet to a lower frequency by changing Cci and Rci. May have to sacrifice fun. Calculate R1c and R2c. Yes Is either of R1c and R2c negative? Are the parasitic poles p4,5 degrading PM by closing on fun? No No Simulate the design for frequency response and transient settling. No More Speed? Yes Yes Increase gm2. Increase gm1 or decrease Cc2. No Does the design meet the specifications? Lower power? Yes Decrease gm3 or gm2. In the worst case scenario decrease gm1. No Yes Smaller layout area? End Yes Reduce Cc1, Cc2 or gm3. No Nothing works! Revisit biasing. Baker/Saxena No Better SR? Yes Increase bias current in the first stage (i.e. ISS1) or use smaller CC’s N-Stage Indirect Compensation Theory The three-stage indirect compensation theory has been extended to Nstages and the closed form small signal transfer function is obtained. Cc n−1 Cc n−2 Cc 2 Cc ic 1 n−1 ic n−2 ic 2 ic 1 Baker/Saxena MULTI-STAGE FULLY-DIFFERENTIAL OP-AMPS Baker/Saxena Fully Differential Op-amps Analog signal processing uses ‘only’ fully differential (FD) circuits. 9 Cancels switch non-linearities and even order harmonics. 9 Double the dynamic range. Needs additional circuitry to maintain the output common-mode level. 9 Common-mode feedback circuit (CMFB) is employed. vop-vom=-A(vinp-vinm) Baker/Saxena Three-Stage FD Op-amp Design: Problems Block Diagram Circuit Implementation VDD VDD vom1 vop1 20/2 VCM fbl 20/2 20/2 fbr 20/2 20/2 20/2 vp vop1 vom Cc2 R2c vop2 vom1 Vbiasp Second Stage VDD vop2 R2c Cc2 fbr 50/2 vop 50/2 VCM VCMFB3 vop 110/2 VDD fbl 100/2 R1c Cc1 100/2 100f First Stage VDD fbl VDD Vbiasn vom2 100/2 fbr VCMFB1 110/2 VDD VCM VCMFB1 100f VDD vom2 Cc1 R1c 30K Vbiasn VDD 30K vm VDD VDD vom 100/2 Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. Output Buffer (Third Stage) The CMFB loop disturbs the DC biasing of the intermediate gain stages. 9 Degrades the gain, performance and may cause instability. Baker/Saxena Three-Stage FD Op-amp Design: Solutions Cc2 1. Employ CMFB 1. Individually across all the stages. 2. Only across the last two stages as the biasing of the output buffer need not be precise. 3. Only in the third stage (output buffer). Cc1 + vp -A1 1p - 2p +A2 vbiasp vm -A1 - 3p vop vCM vbiasn +A2 1m + -A3 -A3 2m 3m vom Cc1 Cc2 Cc2 2. vp Cc1 + -A1 - 1p 2p +A2 -A3 vCMFB vm -A1 + - 1m 3p vop vp Cc1 + -A1 - 1p 2p +A2 +A2 2m -A3 3m vom vm -A1 + - 1m +A2 2m Cc1 Cc2 -A3 vCMFB vCM Cc1 Baker/Saxena Cc2 3. Cc2 -A3 3p vop vCM 3m vom Three-Stage FD Op-amp Design Circuit Implementation Block Diagram Second Gain Stage VDD VDD VDD vom2 Cc1 R1c VDD VDD VDD vom1 VDD vop1 fbr fbl vm 20/2 VCM fbl 20/2 20/2 fbr 20/2 20/2 20/2 Vbiasn R1c Cc1 vop2 vp Vbiasn Vbiasn First Gain Stage VDD vom2 110/2 VDD R2c Cc2 fbl vop vop 30K fbr 50/2 50/2 VCM VCMFB3 VCM 100/2 100/2 VCMFB3 100f 100/2 100/2 110/2 VDD Cc2 R2c 30K vom Unlabeled NMOS are 10/2. Unlabeled PMOS are 22/2. vop2 100f VDD vom Output Buffer (Third Stage) Use CMFB only in the output (third) stage. → Manufacturable design. 9 Leaves the biasing of second and third stage alone without disturbing them. Employ diff-amp pairs in the second stage for robust biasing. Baker/Saxena Baker/Saxena 30K 100f 30K 100f Three-Stage FD Op-amp: Enlarged Chip 3: Low-VDD FD Op-amps Best Performance AMI C5N 0.5μm CMOS, 1.5mmX1.5mm die size. Baker/Saxena Simulation and Performance Comparison DC behavior Transient response 82dB gain >2.5X figure of merit (FoM). Baker/Saxena ts=275ns Flowchart for Three-Stage FD Op-amp Design Start with the initial specifications on fun, CL, Av, and SR. Design a singly-ended pole-zero cancelled three-stage op-amp for the given specifications. Convert the singly-ended op-amp into a fully differential one by mirroring it. Use a pair of diff-pairs for the second stage for robust biasing. Add a CMFB circuit in the output buffer. No Update the value of gm3 corresponding to the output buffer and recalculate R1C and R2C. Simulate the design. Does the design meet specifications? Yes End Baker/Saxena Conclusions Indirect compensation leads to significantly faster, lower power op-amps with smaller layout area. Indirect compensation using split-length devices facilitates low-VDD opamp design. Novel pole-zero canceled three-stage RNIC op-amps exhibit substantial improvement over the state-of-the-art. A theory for multi-stage op-amps is presented. New methodologies for designing multi-stage FD op-amps proposed which improve the state-of-the-art. All proposed op-amps are low voltage 9 Open new avenues for low-VDD mixed signal system design. Baker/Saxena Future Scope Mathematical optimization of PZC op-amps. Design of low-VDD systems in nano-CMOS process 9 Pipelined and Delta-Sigma data converters, 9 Analog filters, 9 Audio drivers, etc. Further investigation into indirect-compensated op-amps for n≥4 stages. Baker/Saxena References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] Baker, R.J., “CMOS: Circuit Design, Layout, and Simulation,” 2nd Ed., Wiley Interscience, 2005. Saxena, V., “Indirect Compensation Techniques for Multi-Stage Operational Amplifiers,” M.S. Thesis, ECE Dept., Boise State University, Oct 2007. The International Technology Roadmap for Semiconductors (ITRS), 2006 [Online]. Available: http://www.itrs.net/Links/2006Update/2006UpdateFinal.htm Zhao, W., Cao, Yu, "New Generation of Predictive Technology Model for sub-45nm Design Exploration" [Online]. Available: http://www.eas.asu.edu/~ptm/ Slide courtesy: bwrc.eecs.berkeley.edu/People/Faculty/jan/presentations/ASPDACJanuary05.pdf Leung, K.N., Mok, P.K.T., "Analysis of Multistage Amplifier-Frequency Compensation," IEEE Transactions on Circuits and Systems I, Fundamental Theory and Applications, vol. 48, no. 9, Sep 2001. You, F., Embabi, S.H.K., Sanchez-Sinencio, E., "Multistage Amplifier Topologies with Nested Gm-C Compensation," IEEE Journal of Solid State Circuits, vol.32, no.12, Dec 1997. Grasso, A.D., Marano, D., Palumbo, G., Pennisi, S., "Improved Reversed Nested Miller Frequency Compensation Technique with Voltage Buffer and Resistor," IEEE Transactions on Circuits and Systems-II, Express Briefs, vol.54, no.5, May 2007. Lee, H., Mok, P.K.T., "Advances in Active-Feedback Frequency Compensation With Power Optimization and Transient Improvement," IEEE Transactions on Circuits and Systems I, Fundamental Theory and Applications, vol.51, no.9, Sep 2004. Eschauzier, R.G.H., Huijsing, J.H., "A 100-MHz 100-dB operational amplifier with multipath Nested Miller compensation," IEEE Journal of Solid State Circuits, vol. 27, no. 12, pp. 1709-1716, Dec. 1992. Leung, K. N., Mok, P. K. T., "Nested Miller compensation in low-power CMOS design," IEEE Transaction on Circuits and Systems II, Analog and Digital Signal Processing, vol. 48, no. 4, pp. 388-394, Apr. 2001. Leung, K. N., Mok, P. K. T., Ki, W. H., Sin, J. K. O., "Three-stage large capacitive load amplifier with damping factor control frequency compensation," IEEE Journal of Solid State Circuits, vol. 35, no. 2, pp. 221-230, Feb. 2000. Baker/Saxena References contd. [13] [14] [15] [16] [17] [18] Peng, X., Sansen, W., "AC boosting compensation scheme for low-power multistage amplifiers," IEEE Journal of Solid State Circuits, vol. 39, no. 11, pp. 2074-2077, Nov. 2004. Peng, X., Sansen, W., "Transconductances with capacitances feedback compensation for multistage amplifiers," IEEE Journal of Solid State Circuits, vol. 40, no. 7, pp. 1515-1520, July 2005. Ho, K.-P.,Chan, C.-F., Choy, C.-S., Pun, K.-P., "Reverse nested Miller Compensation with voltage buffer and nulling resistor," IEEE Journal of Solid State Circuits, vol. 38, no. 7, pp. 1735-1738, Oct 2003. Fan, X., Mishra, C., Sanchez-Sinencio, "Single Miller capacitor frequency compensation technique for low-power multistage amplifiers," IEEE Journal of Solid State Circuits, vol. 40, no. 3, pp. 584-592, March 2005. Grasso, A.D., Palumbo, G., Pennisi, S., "Advances in Reversed Nested Miller Compensation," IEEE Transactions on Circuits and Systems-I, Regular Papers, vol.54, no.7, July 2007. Shen, Meng-Hung et al., "A 1.2V Fully Differential Amplifier with Buffered Reverse Nested Miller and Feedforward Compensation," IEEE Asian Solid-State Circuits Conference, 2006, p 171-174. Baker/Saxena