* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Design Strategy For Barrel Shifter Using 2:1 Mux at 45 nm

Electronic engineering wikipedia , lookup

Electrification wikipedia , lookup

Electrical substation wikipedia , lookup

Audio power wikipedia , lookup

Power over Ethernet wikipedia , lookup

Buck converter wikipedia , lookup

Electric power system wikipedia , lookup

Power electronics wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Integrated circuit wikipedia , lookup

Rectiverter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power engineering wikipedia , lookup

Control system wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Alternating current wikipedia , lookup

Mains electricity wikipedia , lookup

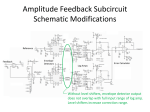

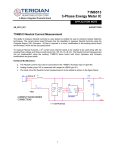

IJSART - volume 1 Issue 4 –APRIL 2015 ISSN [ONLINE]: 2395-1052 Design Strategy For Barrel Shifter Using 2:1 Mux at 45 nm and 90 nm Technology Node Amrita Pahadia1,Dr. Uma Rathore Bhatt2,Mr. Vijay Bhatt3 Department of Electronics & Telecommunication. 1, 2 Institute of Engg. &Technology ,DAVV 3 Chamelidevi Institute of Techology and management, Indore Abstract- Designing a mux for low power to use it as a repetitive block in the barrel shifter will considerably reduce the simulation time .our basic objective is to compare existing 2:1 multiplexers with proposed multiplexer design in term of power consumption ,temperature sustainability ,noise immunity and frequency, so that a fast and optimized barrel shifter can be designed by the help of it.a 2:1 multiplexer[7] is a basic building block of the “switch logic”. The multiplexer circuit is typically used to combine two or more digital signals onto a single line, by placing them there at different times. Technically, this is known as time-division multiplexing. Multiplexers can also be used as programmable logic devices. By specifying the logic arrangement in the input signals, a custom logic circuit can be created. The selector inputs then act as the logic inputs. This is especially useful in situations when cost is a factor and for modularity. The increasing prominence of portable systems and need to limit power consumption has led to rapid and innovative developments in low power vlsi design during recent years. The driving forces behind these developments are portable device applications requiring low power consumption and high throughput due to their small chip size with large density of components, increased complexity and high frequencies. Keywords: power temperature consumption, propagation Bit vector for A is denoted as a7a6a5a4a3a2a1a0 and the shift/rotate amount, B, is 3 bits. A= a7a6a5a4a3a2a1a0 and B= 3 Operation Y 3-bit shift right logical 0 0 0 a7 a6 a5 a4 a3 3-bit shift right arithmetic a7 a7 a7 a7 a6 a5 a4 a3 3-bit rotate right a2 a1 a0 a7 a6 a5 a4 a3 3-bit shift left logical 3-bit shift left arithmetic a4 a3 a2 a1 a0 0 0 0 a7 a3 a2 a1 a0 0 0 0 3-bit rotate left a4 a3 a2 a1 a0 a7 a6 a5 delay I. INTRODUCTION Barrel shifter is an integral component of many computing systems due to its useful property that it can shift and rotate multiple bits in a single cycle . Barrel shifter is an important block of a floating point arithmetic block and used to shift the data by n bits.logic diagram of barrel shifter is shown in fig1. designed using Dsch tool The design of barrel shifter is almost symmetric and can be done using repetitive combinational logic blocks. The shifter[5] is an integral part of many digital designs .there are many application that require shift operation including CPUs ,floating point operation(like addition, subtraction, normalization),variable length coding etc.A barrel shifter needs nlog2 mux for n bit shifting and therefore designing a mux for low power to use it as a repetitive block in the barrel shifter will considerably reduce Page | 192 the simulation time .We designed and compare the various existing 2:1 multiplexer in term of power supply voltage versus power consumption and, temperature sustainability. All the post layout simulation have been performed at 45nm and 90nm technology on dsch 3.5 version and microwind 3.5 version EDA tool.We assume A to be the input operand, B to be the shift/rotate amount, and Y to be the shifted/rotated result. We define A to be an n-bit value, where n is an integer power of two. Therefore,B is a log2(n)-bit integer representing values from 0 to n-1. Table I .shift and rotate examples for A= a7a6a5a4a3a2a1a0 and B= 3 bit Materials and methods: A B-bit shift right logical operation performs a B-bit right shift and sets the upper B bits of the result to zeros. A B-bit shift right arithmetic operation performs a B-bit right shift and sets the upper B bits of the result to a n-1 ,which corresponds to the sign bit of A. A B-bit rotate right operation performs a B-bit right shift and sets the upper B bits of the result to the lower B bits of A. www.ijsart.com IJSART - volume 1 Issue 4 –APRIL 2015 A B-bit shift left logical operation performs a B-bit left shift and sets the lower B bits of the result to zeros. A B-bit shift left arithmetic operation performs a B-bit left shift and sets the lower B bits of the result to zeros. The sign bit of the result is set to a n-1. A B-bit rotate left operation performs a B-bit left shift and sets the lower B bits of the result to the upper B bits of A. Various 2:1 multiplexer circuits simulations are performed on 90nm and 45nm technologies with supply voltage ranging from 0.6V to 1.4V. In order to find out the optimized design in terms of power, delay, power-delay product, the simulation have been carried out at varying supply voltages, temperatures and operating frequencies.. ISSN [ONLINE]: 2395-1052 product, the simulation have been carried out at varying supply voltages , temperatures and operating frequencies. III. PRIOR WORK Prior design was differential cascade voltage switch logic. require both true and complemented signals to be routed gate. As shown in Design Fig.2 the circuit require both inverting and non inverting signals which takes large wiring area. So by adding two NMOS transistor in pull up part of existing 2:1 multiplexer[5] the circuit shows remarkable improvement over the existing design. Results and discussion: 1) VDD versus power consumption of existing and and proposed mux at 90nm and 45nm technology. Existing 2:1 multiplexer: DCVSL (Differential Cascode Voltage Swith Logic) The Prior technique of designing low power 2:1 Mux[7] Presented is Differential Cascode Voltage Swith Logic(DCVSL)circuit. Schematic of DCVSL circuit is shown in the Fig. 3. Cascode Voltage Switch Logic (CVSL) refers to a CMOS-type logic family which is designed for certain advantages. A logic function and its inverse are automatically implemented in this logic style. The pull-down network implemented by the NMOS logic tree generated complementary output. The advantage of DCVSL is in its logic density that is achieved by elimination of large PFETS from each logic function. Fig 1: logic diagram of barrel shifter II. RESEARCH ELABORATIONS We compares the proposed design(MDCVSL) and existing 2:1 multiplexer design(DCVSL)[7] in term of power consumption and temperature for two technology nodes i.e. 45nm and 90nm. Various 2:1 multiplexer circuits simulations [6]are performed on 90nm and 45nm technologies with supply voltage ranging from 0.6V to 1.4V. In order to find out the optimized design in terms of power, delay, power-delay Page | 193 www.ijsart.com IJSART - volume 1 Issue S.N O. VDD (v) 1 0.6 2 0.8 3 1 4 1.2 5 1.4 IV. 4 –APRIL 2015 POWE R CONS UMPT ION OF PROP OSED MUX( MDCV SL) 90nm (µw) POWE R CONS UMPTI ON Of PROP OSED MUX (MDC VSL) 45nm 15.626 µw 33.836 µw 59.422 µw 92.763 µw 0.134 mw 7.916 µw 16.653 µw 29.276 µw 46.172 µw 67.730 µw ISSN [ONLINE]: 2395-1052 POW ER CONS UMP TION OF EXIS TING MUX (DCV SL) 90nm POWER CONSU MPTIO N OF EXISTI NG MUX (DCVSL ) 45nm 20.427 µw 46.004 µw 82.201 µw 0.129 mw 0.186 mw 9.542 µw 20.253 µw 35.462 µw 55.495 µw 80.622 µw Fig 2: Exist ing 2:1 Mult iplex er Desi gn (DC VSL ) 60 50 40 30 20 10 0 VDD(v) mdcvsl (µw)at 45nm 0.6 0.8 1 1.2 Fig.5 shows graph between Vdd versus power consumption for 45nm technology node 2) Temperature versus power consumption of existing and proposed mux at 90nm and 45nm technology Tem p. (°C) PROPOSED 2:1 MULTIPLEXER DESIGN MDCVSL (Multiplexer double cascade voltage switch logic) 10 30 50 70 90 POWE R CONSU MPTIO N OF PROPO SED MUX( MDCV SL) 90nm in µw 62.27 58.957 56.118 53.662 51.516 POWER CONSU MPTION Of PROPOS ED MUX(M DCVSL) 45nm in µw 29.276 27.858 26.642 25.590 24.670 POWER CONSUM PTION OF EXISTING MUX POWER CONSUM PTION OF EXISTING MUX (DCVSL) 90nm in µw (DCVSL) 45nm in µw 86.358 81.522 77.354 73.738 70.581 84.748 79.949 33.723 32.420 31.275 LAYOUT DIAGRAM OF MDVSL: Fig3: proposed 2:1 Multiplexer Design (DCVSL) 100 80 60 40 20 0 VDD(v) 0.6 0.8 1 1.2 mdcvsl( µw)at 90nm Fig.4 shows graph between Vdd versus power consumption for 90nm technology node Page | 194 Fig.5 Layout diagram of proposed mux in 45 nm technology www.ijsart.com IJSART - volume 1 Issue 4 –APRIL 2015 ISSN [ONLINE]: 2395-1052 V. CONCLUSION This paper concluded with the efficient approach of 2:1 multiplexer designed using Dsch tool for 45nm and 90nm technology.power consumption for given supply voltage is smaller in 45nm technology compare to 90nm technology .The post layout simulation have been done for the proposed circuit in order to show improvement in power consumption over supply voltages,temperature.The net effect is that proposed 2:1 multiplexer shows a much better performance for 45nm technology compared to 90nm technology. REFERENCES [1] [1] Shen-fu Hsiao, Jia-Stang Yeh, and Da-Yen Chen, “High Performance Multiplexer Based Logic Synthesis Using Pass-transistor Logic”,Taylor & francis Gropu, VLSI Design, vol. 15(1), pp. 417-426, in year 2002. [2] [2] M. Morris Mano, R. Kime, Logic and Computer Design Fundamentals, Pearson Education, 2nd edition, 2001. [3] N. Weste and D. Harris. CMOS VLSI Design: A Circuits and Systems Perspective, Addison Welsey, 3rd Ed., 2004. [4] M. Janaki Rani ,S. Malarkann, leakage power reduction and analysis of CMOS sequential circuits, International Journal of VLSI design & communication Systems (VLSICS) ,vol.3, no.1, Feb.2012, pp.13-23. [5] Abhijit Asati, Chanda Shekhar, A purely Mux based high speed barrel shifter VLSI implementation using three different logic design styles, International Conference on Mechanical Engineering and Technology, Springer, vol.125, pp.639-646,2012 [6] Illa Gupta, Neha Arora, and Prof. B.P. Singh, “Simulation and analysis of 2:1 mux in 90nm technology,” IJMER, Vol. 1, Issue.2,mar-april 2012,pp642-646,ISSN:2249-6645 [7] Prasad D Khandekar, Dr. Mrs. Shaila Subbaraman, Venkat Raman Vinjamoori ”Low Power 2:1 MUX for Barrel Shifter” First International Conference on Emerging Trends in Engineering and Technology. [8] Rinu Pappachan,V.Vijaykumar, T. Ravi and V. Kannan, “Design and Analysis of 4-Bit Low-Power Barrel Shifter in 20nm FINFET Technology”, IJES, Volume-2, Issue3, pp.17-25, 2013. [9] Behzad Razavi.”design of analog CMOS Intgration circuit”,Tata McGrew Hill Edition year 2002. Page | 195 www.ijsart.com