* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download 1.0 Introduction - Electrical and Computer Engineering

Ground loop (electricity) wikipedia , lookup

Three-phase electric power wikipedia , lookup

Immunity-aware programming wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical ballast wikipedia , lookup

Power inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Electrical substation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Current source wikipedia , lookup

Two-port network wikipedia , lookup

Stray voltage wikipedia , lookup

Integrating ADC wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Regenerative circuit wikipedia , lookup

Alternating current wikipedia , lookup

Surge protector wikipedia , lookup

Voltage optimisation wikipedia , lookup

Voltage regulator wikipedia , lookup

Schmitt trigger wikipedia , lookup

History of the transistor wikipedia , lookup

Mains electricity wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

UNIVERSITY OF VICTORIA

Department of Electrical and Computer Engineering

DC –DC ZVT Converter

ELEC 499B

Group #: 8

Company Name:

Power Electronic Solutions

Strive Hard And Create Results

Submitted on: April 2,2004

To: Dr. Bhat

Group Members:

Kam Sangha

Jimmy Virk

Patrick Iemma

0127686

0127685

0127670

Table of Contents

Summary………………………………………………………………………….

1.0 Introduction………………………………………………………………….

2.0 Discussion…………………………………………………………………...

2.1 Project Specifications:…………………………………………..

2.2 Proposed Solution…………………………………………….

2.3 Design Process:…………………………………………………….

2.3.1 Assumptions………………………………………………

2.3.2 Calculations …………………………………………..

2.3.3 Micro Controller ……………………………………………

2.3.3.1 Micro controller codes………………………

2.3.4 Driver Circuit ……………….…………………………

2.4 Converter Features………………………………………

2.5 Operation principles……………………………………….

2.6 Results…………………………………………………………….

3.0 Conclusions………………………………………………………………

4.0 Recommendations ………………………………………………………..

Team……………………………………………………………………………

References………………………………………………………………………..

Summary:

The object of the project was to design and built a step-up dc-to-dc converter operating

with zero-voltage-transition, in the laboratory. Ideal product should take 25 to 32 dc

voltage and output 120 dc voltage with a switching frequency of 200 kHz. The unique

feature of this converter is that gating signals for transistors and the gain of the converter

is controlled by a micro controller. The design includes two transistors. The main

transistor that handles most of the current is switched under zero voltage and the auxiliary

transistor is switched under zero current. Additionally, it has a simple structure, low cost,

and ease of control. With using soft switching in the converter increases the efficiency of

the converter to 97% compare to 91% with hard switching. The laboratory built converter

was up to 94% efficient when the input voltage was set to 32 V. This circuit has s

resonant circuit and switching losses are reduced by the means of the commutations

which are realized with zero voltage switching.

1.0 Introduction:

Soft-switching techniques are used to reduce the switching losses in power converters.

Zero-voltage-transition and zero-current-transition are the two recently proposed

techniques used to reduce the switching losses. Pulse Width Modulated (PWM) dc-dc

converters are widely used in industry due to their high power density, fast transient

response and ease of control. Increasing the switching frequency achieves a higher power

density and faster transient response. With the implementation of a higher switching

frequency, the more switching losses and electromagnetic interference (EMI) noise occur.

To utilize a higher switching frequency, a decrease in switching loss must occur. To

decrease the switching losses a snubber circuit is used. There are many documented

snubber

cell

circuit

designs

such

as

the

RC/RCD,

polarized/nonpolarized,

resonant/nonresonant, and active/passive snubbers.

In recent years, a number of zero voltage transition (ZVT) and zero current transition

(ZCT) PWM converters have been proposed by adding resonant active snubbers to

conventional PWM converters to combine the desirable features of both resonant and

normal PWM techniques. With these converters turn off and on take place under zero

voltage transition during very short period of ZVT time provided by resonance.

In this project, the design used is a new active snubber cell that ideally overcomes most

of the problems of the normal ZVT-PWM converter. The main transistor that handles

most of the current is switched under zero voltage and the auxiliary transistor is switched

under zero current. Additionally, it has a simple structure, low cost, and ease of control.

2.0 Discussion:

2.1 Project Specifications:

The object of this project was to design and built a step-up dc-to-dc converter operating

with zero-voltage-transition, in the laboratory. The specifications of the converter are:

Ideal Product

Input voltage (dc) = 25 to 32 V

Output dc voltage = 120 V

Switching frequency = 200 kHz

2.2Proposed Solution:

Our proposed solution to the above problem is to increase the efficiency and reduce the

cost of the step-up circuit. The design of the circuit is not an original design of Power

Electronic Solutions (PES); however, the control of the circuit is unique and will be

explained later in the report. The ZVT – PWM DC-DC converter described within this

report is far more efficient and less costly then the previously method used. The basic

idea of the circuit is to ‘control’ the MOSFET switching and regulate the output of the

circuit without the need to do any tedious functions or conversions as can be seen above

with the switching from DC-AC-DC. The limited switching loss of this circuit creates a

highly efficient circuit which can be implemented within and practical application.

2.3 Design Process:

After researching various methods of creating a step-up voltage circuit it was determined

that the following circuit was the most appropriate for the task at hand:

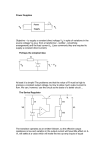

The circuit in figure 1 satisfies all the criteria theoretically. Since it was determined that

the efficiency if a boost converter decreases rapidly above the gain of 3, it was decided to

implement 2 stages to achieve the design goals efficiently . To satisfy the requirement of

having a gain of 5 it was determined that a two stage power circuit would be the best

solution.

D1,D2, Dr, Df - MUR102OC7

T1, T2 - IRFP350

Lf 2mH

Df

Dr

24V

T1

Cr

1nF

Lr

10uH

3.9k

Cb

82nF

RL

D1

100k

D2

T2

Cf

470uF

QT1

Feedback

Signal

QT2

University of Victoria

ELEC499B

Project:

DC-DC ZVT CONVERTER

Group #

Date

03/26/04

Rev

00

8

Group Members

Jimmy Virk

Kam Sangha

Patrick Iemma

Figure 1: Proposed DC – DC ZVT converter.

The circuit given the figure 1 is the proposed DC – DC ZVT converter. The snubber part

of the circuit consists of inductor, Lr, a resonant capacitor CB, an auxiliary transistor T2

and diodes (D1, D2).

2.3.1 Assumptions:

There were some assumptions made to simplify the steady state analysis of the circuit

during one switching cycle and calculations for all the devices for the circuit. The

assumptions made were:

a) Input voltage Vi is constant.

b) Output voltage Vo is constant or output capacitor CF is large enough.

c) Input current Ii is constant or main inductor LF is large enough.

d) Resonant circuits are ideal.

e) Main inductor LF is much larger than snubber inductor Lr.

f)

Voltage drops and parasitic capacitors of semiconductor devices are ignored.

g) Reverse recovery time of all diodes except the main D is ignored.

2.3.2 Calculations:

Sunbber inductor Lr is selected to allow current rise rate to maximum input current at the

most, within three times the normal reverse recovery time of the main diode. CB is

selected to charge up to the output voltage. The snubber inductor Lr and snubber

capacitor CB is selected so that the voltage rise time rates of both of the transistors to be

minimally their fall time ratings.

Vo

* 3 * trr Ii (max)

Lr

1

1

1

* Lr * ( I i (max) I rr (max) ) 2 C r * V 2 * C B * Vo 2

2

2

2

o

Lr * C B t f 2

2

Cr C B

* Vo t f 1

I i (max)

Vo G * Vi

1

1 D

Ton

D

T

G

In the above formula, Vo is the output voltage, Ii is the input current and Irr is the reverse

recovery current for the main diode.

For MUR 1020CT

t rr 35ns

From the above formulas, it was calculated that

Lr 1.26 H Select Lr= 10H

Cr= 1F

CB 82F

Dr, D1, D2, Df =MUR102OCT

T1, T2 = IRFP350

Lf = 2mH

Cf = 470F

Switching frequency = 200 KHz

2.3.3 Micro Controller:

The unique feature of the proposed converter is that the gating signals for the transistor

T1 and T2 are controlled by a micro controller. The micro controller that used for this

purpose was ATMEGA8-16BC. The circuit diagram is given in figure 2. The duty cycle

of the waveform of the main transistor changes according to the gain required for the

converter. As it can be seen in the results section that as the input voltage is increased the

gain decreases.

28

2

27

3

26

4

25

5

24

5V

10 pF

7

8

9

10 pF

TO Gate of

Main

Transistor

ATMEGA8-16BC

6

23

22

21

20

10

11

19

12

17

13

16

14

Feedback

5V

5V

18

15

To Gate of Auxiliary

Transistor

University of Victoria

ELEC499B

Project:

Group #

Date

03/26/04

Rev

00

8

Group Members

Jimmy Virk

Kam Sangha

Patrick Iemma

Figure2: Micro-controller connections.

The microcontroller is used to control the gating signals to the FETs. The gating signal to

the auxiliary FET has to be 500ns pulse. But due to the speed constraints for the

microprocessor, the minimum pulse width achievable was 1.6micro seconds. The pulse of

the main transistor starts when the pulse to the auxiliary FET is turned off. The duty cycle

of the main FET determines the gain for the circuit. The duty cycle of the main FET was

kept variable so that the gain can be changes as requited. The duty cycle is determined by

the feedback. The feedback is set so that the feedback voltage is exactly 2.5V when the

output voltage is equal to the desired output. If the output voltage is less than the desired

output, the feedback voltage is less than 2.5V. Hence the program increases the duty

cycle. If the output voltage is more then the desired voltage, the feedback voltage is more

then 2.5V, and the program will decrease the duty cycle of to decrease the gain of the

circuit.

The gating signals are produced using interrupts. This is a very accurate method to

generate gating signals because the gating signals will take propriety over all other tasks.

There Initially the auxiliary transistor is turned ON. The output compare interrupt is set

up to occur when the counter reaches 3. This point is referred to at point A. When the

interrupt occurs, the auxiliary FET is turned OFF and the main transistor is turned ON.

The next interrupt is set to occur when the counter reached point B. Point B is variable

and changes to vary the gain. When the interrupt occurs at point B, the main FET is

turned OFF. The next interrupt is set to occur at point C. This point determines the

frequency of operation. When the interrupt occurs at point C, the auxiliary transistor is

turned ON and the next interrupt is set to occur at point A.

The value of B is initillay set at 80 (in hex numbers). This ensures that the duty cycle at

startup is 50%. Then the microcontroller reads the feedback voltage at ADC0 pin. If the

voltage is less than 2.5V, the microcontroller decreases B by one and if the voltage at

ADC0 pin is more then 2.5V, the micro increases the value of B.

Given below is the flow diagram for the microcontroller code.

Figure 3: Flow diagram of the codes for micro controller.

2.3.3.1 Micro Controller codes:

;*************************************************************************************

****

;Program Name:Program1.asm

;Date: March 1, 2004

;Objective: Produce gating signals for the FETs used in the DC-DC ZVT

;converter

;Specifications: PortB is used to output the signals, PB0 is the main

;transistor and PB1 is the auxillary transistor

;The gating signals to the two transistors are to be syncronised. The frequency

;of the gating signals can be changed by changing the value of C. The pulse width

;of the auxillary transistor can be changed by changing the value of A. The pulse

;width of the main transistor can be changes by changing the value of B.

;The program implements the closed loop system. The duty cycle of the main transistor

;is changes according to the gain required in the circuit. The feedback from the circuit

;is obtained by using a voltage divider at the output. The voltage divider is so selected

;that the voltage at the feedback point is 2.5V at the desired output. The program

;adjusts the value of B so that the feedback voltage is 2.5V by increasing or decreasing

;the duty cycle of the main transistor.

;*************************************************************************************

; include the definition file

.include "m8def.inc"

;declare the variable registers

.def

temp

=

R16

.def

temp1 =

R17

.def

tolerance

=

.def

sweetspot

=

.def

A

=

R20

.def

B

=

R21

.def

C

=

R22

.def

STATE = R25

.def

temp2 = R26

R18

R19

.org 0x0000

rjmp reset

; set up the interrupt vactors

.org OC1Aaddr

rjmp OC1A

.org 0x0122

reset:

cli

ldi temp,high(RAMEND)

out SPH, temp

ldi temp, low(RAMEND)

out SPL, temp

;Set port B as O/P and port C as input

ldi temp, 0xFF

out DDRB, temp

out

DDRD, temp

ldi temp, 0x00

out PORTB, temp

out DDRC, temp

out PORTD, temp

;Define variables

ldi A, 0x03

ldi B, 0x80

ldi C, 0xFF

ldi tolerance, 0x01

ldi sweetspot, 0x7E

; Initial value of OCR

ldi temp, 0x00

out OCR1AH, temp

mov temp, A

out OCR1AL, temp

; initialize timer1 and timer1 to compare output with OCRA1

ldi temp, 0x00

out TCNT1H, temp

out TCNT1L, temp

out TCCR1A, temp

ldi temp, 0x10

out TIFR, temp

ldi temp, 0x10

out TIMSK, temp

ldi temp, 0x01

out TCCR1B, temp

;Set ADC to read ADC0 in free running mode

ldi temp, 0x20

out ADMUX, temp

ldi temp, 0xE0

out ADCSR, temp

ldi STATE, 0x01

ldi temp, 0x0A

out PORTB, temp

ldi

ldi

sei

temp1, 0xFF

temp2, 0xFF

dec

cpi

brne

dec

cpi

brne

jmp

temp1

temp1, 0x02

loop

temp2

temp2, 0x02

loop

ADC1

loop:

OC1A:

;cli

in temp, SREG

push temp

cpi STATE, 0x01

brne STATE2

;jmp STATE2

STATE1:

ldi STATE, 0x02

ldi

temp, 0x05

out PORTB, temp

ldi temp, 0x00

out OCR1AH, temp

mov temp, B

out OCR1AL, temp

;0X01

pop temp

out SREG, temp

;sei

reti

STATE2:

cpi STATE, 0x02

brne

STATE3

;jmp STATE3

ldi STATE, 0x03

ldi

temp, 0x00

out PORTB, temp

ldi temp, 0x00

out OCR1AH, temp

mov temp, C

out OCR1AL, temp

pop temp

out SREG, temp

;sei

reti

STATE3:

ldi STATE, 0x01

ldi

temp, 0x0A

out PORTB, temp

ldi temp, 0x00

out TCNT1H, temp

out TCNT1L, temp

out OCR1AH, temp

;mov temp, A

out OCR1AL, A

pop temp

out SREG, temp

;sei

reti

ADC1:

in temp,ADCH

mov temp1, temp

cln

sub temp, sweetspot

brmi RESNEG

sub temp, tolerance

brmi ADCOK

cpi

B, 0x20

breq

ADCOK

dec B

jmp ADCOK

RESNEG:

cln

mov

temp, sweetspot

sub temp, temp1

cln

sub temp, tolerance

brmi ADCOK

cpi

B, 0xE5

breq

ADCOK

inc B

ADCOK:

;0x02

ldi

temp1, 0xFF

ldi

temp2, 0xFF

jmp loop

2.3.4 Driver Circuit:

Driver Circuit takes input from 0-5 V from the microcontroller and provides an output of

0-10V that drives the gate of the transistors. The purpose of the driver circuit is to

provide a large amount of current that is required to charge the source to drain capacitor

of the transistor at turn on time. Two anti parallel zener diodes are there to protect the

main circuit from voltage surges. If the voltage from source to the drain becomes more

than -15V or less than -15V, the zener diodes break down and hence provide protection to

the FETs . The 10 K resister discharges the source to drain capacitor of the transistor at

the time transistor is turned off.

Figure 4: Driver Circuit for the converter.

Figure 5 shows the driver circuit with the converter. The only thing missing from the

circuit is the micro controller and is shown in figure 3.

Figure 5: Converter circuit with driver circuit.

2.4 Converter Features:

1.The two FETs are turned on and off under exact or near ZVS and/or ZCS.

T1, the main transistor, is switched on under perfect ZVS provided with ZVT.

DF, the main diode, is switched on/off with ZVS.

T2, the auxiliary transistor, is switched on under near ZCS and switched off with

near ZVS.

The auxiliary diodes {Dr, D1, D2} operate with soft switching.

2. The converter has a simple design and low cost. Although the design is simple and cost

low, this circuit overcomes most of the drawbacks of the normal ZVT-PWM converter.

3.The control of this circuit is quite easy. In this project a micro-controller was used to

control the duty cycle of the control signal to both the main and auxiliary transistors.

2.5

Operation principles:

There are seven stages that occur in the steady state operation of the converter shown in

figure 1 over one switching cycle. See figure 6 for the switching cycle.

Stage 1 [t0 < t < t2]:

The main transistor T1 and the auxiliary transistor T2 are in the off state before t=

t0. Diode DF conducts the current Ii of inductor LF.

At t = t0, a signal is applied to the auxiliary transistor T2. Devices Dr and T2 are

turned on under near ZCS. The current through Dr and T2 is limited by the

snubber inductor Lr. T2 current rises and DF current falls simultaneously and

linearly.

At t = t1, T2 current reaches Ii and DF current falls to zero.

At t = t2, The reverse recovery current of DF drops to -Irr, thus the diode is turned

off under ZVS.

Stage 2 [t2 < t < t3]:

Transistor t1 and diode DF are off state before t=t2.

The auxiliary transistor T2 is in the on state and conducts current Ii + Irr.

At t = t2, a parallel resonance between Lr and Cr begins via the path Cr - Dr - Lr T2.

At t = t3 the transfer of the energy stored in the capacitor Cr to the inductor Lr is

completed and energy in Lr reaches maximum at the same time.

Stage 3 [t3 < t < t4]:

Auxiliary transistor T2 is on state and conducing maximum current of Lr.

VCr = 0, Vcb = 0 at t = t3, the antiparallel diode DT1 of the main transistor T1

conducts.

In this stage, in which DT1 is in the on state, basically provides zero voltage

transition (ZVT) for the main transistor T1.

Stage 4 [t4 < t < t5]:

At t = t4, a signal is applied to the main transistor T1 and the signal to T2 is

removed simultaneously.

A serial resonance between Lr and CB begins via the path Lr - D1 - CB - Dr under

max inductor current ILrmax.

At t = t4 the auxiliary diode D1 is turned on with ZVS.

The energy stored in Lr is transferred to the capacitor CB.

At t = t5 and iLr = 0, the auxiliary diodes Dr and D1 are turned off under near ZCS

through Lr.

Stage 5 [t5 < t < t6]:

T1 continues to conduct the input current Ii and the snubber current is not active.

Stage 6 [t6 < t < t7]:

At t = t6 the signal to T1 is turned off (signal removed) under near ZVS and the

auxiliary diode D2 is turned on with ZVS because of CB charged to V0.

Cr is charged and CB is discharged.

At t = t7 ( Cr = V0 and CB = 0), DF is turned on with ZVS and D2 is turned off

with ZVS.

Stage 7 [t7 < t < t8]:

Diode DF continues conducting the input current Ii and the snubber circuit is not

active.

At t = t8 one cycle is completes and another cycle begins

Figure6: Expected wave form of converter

2.6 Results:

To verify the predicted results given in the figure 6, circuit given in figure 5 was built in

the laboratory.

Waveforms taken using an oscilloscope are given in figures 7 to 9. The figure 7 shows

the gating waveforms that were created by the micro controller for transistor 1 and

transistor 2. Figure 8 shows the gating signal for transistor 1 and voltage across transistor

1. This figure shows the transistor 1 turns on at perfectly with zero voltage transition and

turns off near zero voltage transition.

Figure 7: Channel 1 shows the gating signal for transistor 2 and Channel 2 shows

gating signal for transistor 1.

Figure 8:Channel 1 shows voltage across transistor 1 and channel 2 shows the

gating signal for transistor 1.

Figure 9: Channel 1 shows the current through inductor Lf and channel shows

gating signal for transistor 1.

It can be seen figure 8 that the main transistor operated at ZVT. The voltage across the

FET is zero and then the gating signal is applied to the FET.

Figure 9 shows that the circuit operates in continuous current mode.

64V Version

Vin

Iin

0.8

0.4

1.9

0.5

5.2

0.7

7.8

1.1

10.2

1.4

15.1

1.9

20.2

2.1

24.0

9.0

25.0

9.7

28.0

7.7

30.0

8.1

32.0

8.1

Vout

4.2

10.9

31.8

48.4

63.8

64.0

64.2

64.0

64.2

64.1

63.8

64.0

Iout

0.02

0.04

0.1

0.16

0.21

0.42

0.62

3.2

3.6

3.2

3.6

3.8

Gain

5.25

5.74

6.12

6.21

6.25

4.24

3.18

2.67

2.57

2.29

2.13

2.00

Efficiency

0.2625

0.458947

0.873626

0.902564

0.938235

0.936912

0.938331

0.948148

0.953072

0.951391

0.945185

0.938272

120V Version

Vin

Iin

20.0

7.4

24.0

7.5

26.0

5.9

28.0

5.5

30.0

5.2

32.0

4.9

Vout

110

116

116

116

116

116

Iout

1.2

1.4

1.2

1.2

1.2

1.2

Gain

5.50

4.83

4.46

4.14

3.87

3.63

Efficiency

0.891892

0.902222

0.907432

0.903896

0.892308

0.887755

Gain = Vout/Vin

Efficiency = Vout * Iout/ (Vin*Iin)

Table 1: Shows input current, input voltage, output current,

output voltage, gain and efficiency.

The results in the table 1 show that as that output voltage goes to 116 as the input is

increased to 32 V for the120 V version. It has the efficiency of 90% when the input

voltage is 24 V and drops to 88.8% as the input voltage is increased to 32V. For 64 V

version the efficiency increases as the input voltage is increased. At the input voltage of

32 V the efficiency of the converter is 94%.

Gain Vs Input voltage for 64V version

7

6

Voltage Gain

5

4

3

2

1

0

0

5

10

15

20

25

30

35

Inpur Viltage [V]

Figure 10: Voltage gain Vs input voltage for the 64V version

Input Voltage Vs Efficiecy for 64V varsion

1.2

1

Efficiency

0.8

0.6

0.4

0.2

0

0

5

10

15

20

25

Input Voltage [V]

Figure 11: Efficiency Vs input voltage for the 64V version

30

35

Imput Voltage Vs Gain for 120V varsion

6

5.5

5

Voltage Gain

4.5

4

3.5

3

2.5

2

15

17

19

21

23

25

27

29

31

33

Input Voltage [V]

Figure 12: Voltage gain Vs input voltage for the 120V version

Input Voltage Vs Effiecincy for 120V Version

0.91

0.905

Efficiency

0.9

0.895

0.89

0.885

17

19

21

23

25

27

29

31

33

Input Voltage [V]

Figure 13: Input voltage Vs efficiency for 120V version

It must be mentioned here that although in our initial design, a two stage converter was

designed, it was later on determined to go with a single stage. This decision was taken

considering the efficiency of the circuit. The efficiency of a 2 stage converter would be

too low resulting in losses. Hence a single stage high gain unit was tested successfully.

3.0 Conclusions:

A step-up DC-DC converter was designed, built and test as a requirement of this project.

The drawbacks of the conventional ZVT converter are cover come by the active snubber

cell. All the semiconductor devices turn off and on at near or exact ZVS. The gain of the

circuit was controlled by the micro controller codes.

The duty cycle of the main

transistor’s gating signal is changing according to the gain required for the converter to

regulate the output. This is done in the software for micro controller. Even though earliar

it was predicted that the efficiency of the converter will increase up to 97% but the obtain

results only show maximum efficiency of 94%. There were two different units built for

testing. For the first test unit, the output was regulated to 64V. Then the second unit was

assembled. The two units are identical except for the feedback voltage divider circuit. It

was determined that the units could not operate at 250W. The output current for the 120V

version was 3.6A. Above this, the losses are too large and cause the main FET to

malfunction. Hence the goals of our design were partially acheieved. The DC-DC

converter operates from 24V to 32V input and regulates the output to 120V. The

switching frequency was set at 57KHz.

References:

1. Hacy Bodur, Member, IEEE, and A. Faruk Bakan, A new ZVT –PWM DC-DC

Converter, IEEE Transaction on Power Electronics, vol. 17,NO. 1, January 2002.

The Team

Jimmy Virk ([email protected]) – Software Architect/Hardware Design

Jimmy was an instrumental influence in the decision to develop this project. His main

role was the design and implementation of the software algorithms to control the power

circuit. The team relied on Jimmy’s past experience with circuit design to develop a

realistic circuit design for the project.

Kam Sangha ([email protected]) – Hardware Design/Project Presentation

Kam was responsible for all project presentation including, but not limited to, the project

poster and project website. She had a great influence in all aspects of the project during

the development of the design and production phase. The team relied on Kam to develop

a realistic circuit design for the project

Patrick Iemma ([email protected]) – Hardware Development/Debug

The team relied on Patrick’s past experience with circuit fabrication to come up with a

working and yet presentable model of the project. He was responsible for the debugging

of the design and fabrication of the circuit.