* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download WORD - University of California, Berkeley

Wireless power transfer wikipedia , lookup

Mains electricity wikipedia , lookup

Opto-isolator wikipedia , lookup

History of electric power transmission wikipedia , lookup

Alternating current wikipedia , lookup

Power engineering wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Immunity-aware programming wikipedia , lookup

General Electric wikipedia , lookup

Electrification wikipedia , lookup

Electric motorsport wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrated circuit wikipedia , lookup

Semiconductor device wikipedia , lookup

Two-port network wikipedia , lookup

Power MOSFET wikipedia , lookup

History of the transistor wikipedia , lookup

UNIVERSITY OF CALIFORNIA

College of Engineering

Department of Electrical Engineering and Computer Sciences

Lab #2: Layout and Simulation

NTU IC541CA (Fall 2001)

1

Assumed Knowledge

This lab assumes use of the Electric CAD system (v6.04), which is a free package distributed under the GNU public

license. The package is available for a number of operating systems and is freely distributed in source code format

from http://www.staticfreesoft.com.

If you choose to use your own toolset, make sure that it is capable of performing all the following tasks. Otherwise,

you may find yourself unable to complete the project requirements. The directions are divided into a CAD tool

independent background and Electric-specific parts.

2

CAD Tool Independent Background

Layout is not just the product; it is the process of converting a schematic into geometry. A significant design effort

is required before ever drawing a rectangle in a CAD tool. Depending on the design characteristics and

requirements, the certain aspects of the layout must be emphasized during the initial floorplanning steps.

Floorplanning is the process of creating a high level block diagram for the chip, including locations of I/O pads, size

of modules, estimated inter-block wiring complexity, global wiring delay budgets, clock tree distribution, power

distribution, etc. Maximal benefit is realized when the design is partitioned into a hierarchy in the schematics.

Once floorplanned, individual blocks are implemented according to the aspect ratio (ratio of height to width)

required by the floorplan. For ease of integration into the final chip, most blocks are rectangular.

One goal of custom layout is to minimize the wiring at every level of hierarchy. This can be accomplished by

carefully planning the routes of wires in and out of sub-blocks (including power rails). If the design has several

stages, the outputs of the first stage can have the same pitch and metal layer as the input of the second stage. In this

way, the two blocks can be connected by abutment, ie. by just placing them next to each other such that the metal

touches.

3

Layout in Electric

In Electric, each facet that has a schematic view should have a corresponding layout. In this lab, you will create the

layouts for the inverter and buffer schematics from lab #1. A working set of schematics is available if you did not

finish lab #1.

1

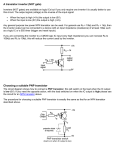

Open the completed inverter schematic. It

should look like the schematic in Figure 1.

Due to the default design rules checking

library, the minimum size transistor for

the technology is 3/2. Note that in this

example, the W/L of the PMOS is 6/2 and

the NMOS is 3/2.

Create a new view for the inverter with

view type layout:

Select menu: Facets: Edit Facet…

Press: New Facet

Enter the name: inverter

Choose view: layout

Check: make new window

Press: Ok

Now pick the technology file for the

layout:

Figure 1: Inverter schematic components

Select menu:

Technology|Change Current

Technology…

Choose: mocmos

Press: Ok

The component window changes to include symbols for pins, wires, transistors, etc.

4

Create an Inverter Layout

Just like in the schematics, Electric differentiates between two coincident shapes and the connection between those

shapes. Take care when making connections throughout this lab. Single left-clicking on a node, such as a via, will

highlight the entire connected net. If something does not highlight correctly, it means that it is not correctly

connected.

Begin by dropping in a NMOS transistor. Select the ‘N-Transistor’

box in the component window (use the status bar hint text to find the

right component) and click in the facet area. Next select the ‘PTransistor’ box and drop it in slightly above the NMOS. Use the

zoom commands on the Windows menu if the scale is too small or

large (Ctrl-9 fits to screen). Examine each transistor carefully. Each

has a large box of ‘active’ area denoted by shading. A very faint

smaller box inside that is the ‘select’ area. The green rectangles are

diffusion and the pink is polysilicon. A small connection crosshair

appears when the green or pink rectangles are selected by leftclicking on them.

Since an inverter has a trivial Euler path, it is easy to connect the

polysilicon by rotating the transistors and making a vertical

connection between them. Select each transistor and rotate it using

Edit|Rotate or Ctrl-J until the polysilicon (pink) is vertical. Select

the lower polysilicon rectangle of the PMOS. Then click the right

button on the crosshair and drag it to the NMOS poly. A pink poly

wire should be created, as shown in Figure 2.

Figure 2: Inverter transistors

2

Figure 3: Power rails and contacts

Figure 4: Connections between contacts

Next, size the transistors so that they match the schematic. Double-click on the PMOS and set its width to 6 and

length to 2. Set the NMOS width to 3 and length to 2. Note that the transistors shape changes according to the size

setting, as expected.

We will run a power (vdd) rail and a ground (gnd) rail on the top and bottom of the inverter, respectively. Since

there is no node in the circuit named vdd, we must create one out of a piece of metal-1. Choose Edit|New Pure

Layer Node… and pick metal-1-node. Click in the facet area and a blue box should appear. Select this box, resize

it using Ctrl-B, and move it into location above the transistors. Either repeat the process or copy and paste to make

another rail below the transistors. The power rails should resemble the blue boxes in Figure 3.

Each transistor needs a contact to connect the active diffusion to the metal-1 layer (shared diffusion transistors can

be connected directly). Choose the Metal-1-N-Active-Con component and place one to the left and right sides of

the NMOS. Next, place Metal-1-P-Active-Con on the left and right sides of the PMOS. Notice that the shading of

the active regions should be the same as the transistor. For each contact, select it and connect it to the green

diffusion using the right mouse button. Electric draws an arc of diffusion to show the connection. Single leftclicking on the contact should highlight the connected network. Verify that the layout appears like Figure 3 and that

the contacts are connected as expected.

Now connect the left contact of the PMOS to the top (vdd) power rail. Connect the left contact of the NMOS to the

bottom (gnd) rail. Connect the right contacts together to form the output of the inverter.

You may have noticed activity in the status window indicating design rule checker (DRC) errors. Electric performs

a quick DRC after every movement of the layout. This feature can be used to make compact designs without the

need to fully understand all the design rules. Move all the contacts closer to the transistor until a DRC error occurs,

then move back a bit. The layout should now look like Figure 4.

The active area needs to be driven correctly to form the body of the transistor (remember a transistor is a four

terminal device). Place a Metal-1-N-Well-Con on the facet near the n-well on the left side of the PMOS. Move the

well contact as close as possible to the transistor without causing a DRC violation. Connect the well contact to the

power rail (or to the source of the transistor). Do the same for a Metal-1-P-Well-Con and connect it to the ground

rail or source of the NMOS.

Now create two Metal-1-Nodes (pure layer nodes) for the input and output pins using the same procedure as the

power rails. Place one in the middle of the left side (input) and one in the middle of the right side (output). Connect

the output to the metal-1 connecting the transistor drains. Place a Metal-1-Polysilicon-1-Con between the input

metal-1 and the poly for the transistors and connect them. The location of the contact is not critical, but metal has a

3

layer resistance than poly, so move it as close to the poly wire as possible without causing a DRC violation in the

status window.

As a last step, all the exports in the schematic must have corresponding

exports in the layout. Select the power rail, choose Export|Create

Export…, type vdd, pick power, and hit Ok. Do the same to create a

ground export called gnd, an input export called In, and an output export

called Out. The completed inverter layout should look similar to Figure

5.

Perform a full DRC by selecting Tools|DRC|Hierarchical Check.

Correct any errors before continuing.

Now, make sure the only two open facets are the inverter schematic and

inverter layout. Electric can perform a layout vs. schematic (LVS) by

invoking a network consistency check. Select Tools|Network|Do

Consistency Check. Fix any differences before continuing. If you

make any changes, be sure to rerun the DRC. Be sure to save your

work.

5

Figure 5: Final inverter layout

Hierarchical Designs

In this step, you will create a buffer using two instances of the inverter you just created. Create a new layout facet

called buffer. Then insert two instances of the inverter{lay} facet. Depending on the mode, the facets may appear

as actual layout or as boxes with just the exports. To switch modes, select the desired instances (use shift to

multiply-select), and choose Facet|Expand Facet Instances|One Level Down or Facet|Unexpand Facet

Instances|One Level Down. One level down means Electric will show the geometry added by the next level of

hierarchy ‘under’ the instance. You can expand/unexpand an arbitrary number of levels, including all of them. In a

large design, there may be millions of rectangles so hiding some detail speeds the editor up quite a bit.

Expand both instances and move them together so the power rails and In/Out connections overlap each other.

Remember that just touching does not mean ‘connected’ to Electric. A DRC check indicates this problem by

complaining about many spacing errors between metal-1. To have Electric automatically connect wires that abut,

use the stitching tool. Select both instances and choose Tools|Routing|Auto-Stitch Highlighted Now. Three

metal-1 arcs should be created to connect the vdd, In/Out, and gnd metal (check the status window). You can also

unexpand the instances to see the wires on this level of hierarchy.

4

Figure 6: Final buffer layout

Create pure metal-1 layer nodes for the power, ground, input, and output. Connect them to the connection crosshairs

or use auto stitching. Create exports for each of them of the right type. Move everything as close together as

possible without causing any DRC violations. Run a hierarchical DRC check and a network consistency check.

When both of these pass cleanly, you have successfully created the buffer out of inverters. My layout is shown in

Figure 6.

6

Exporting to HSPICE

Select Tools|Simulation Interface|SPICE Options and choose HSPICE level 3. Make sure that Use parasitics is

checked and hit Ok. Then choose Tools|Simulation Interface|Write SPICE Deck. Examine the output file and

you should see the two instances of the inverter subcircuit. There are also capacitive parasitics present due to the

wiring. Make sure you understand what Electric has done here so that you can fix any problems that occur in larger

circuits. Note that all the gnd nets are labeled as node 0. All the power nets are called vdd.

It is a real pain to make a decent testbench in Electric, so it is much easier to make one by hand. Essentially, you

need to provide the N and P models (in the g25.mod card), power the vdd net with an independent voltage source,

and provide some input waveform to the In node. This is left as an exercise for the student.

5