* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download CMOS Differential Amplifier with Active Load: CMRR and Mismatch

Brushed DC electric motor wikipedia , lookup

Skin effect wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Electrical substation wikipedia , lookup

Thermal runaway wikipedia , lookup

Three-phase electric power wikipedia , lookup

Power inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Stepper motor wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Voltage regulator wikipedia , lookup

Surge protector wikipedia , lookup

Stray voltage wikipedia , lookup

Mains electricity wikipedia , lookup

Two-port network wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Current source wikipedia , lookup

Wilson current mirror wikipedia , lookup

CMOS Differential Amplifier with Active

Load: CMRR and Mismatch Contribution

for ro3 = ro2.

With mismatched transistors, assuming

vd1=0 and gate-source voltages are equal,

With vgs= vic- vs, vd1=0 and vd2=0,

CMRR-1 =

€

*

,

,

,

,

,

+

#

%

%

%

%

%

$

&

(

(

(

(

(

'

Acm

Acm

Δg m

Δgo 1

1

1

=

=

+

−

A

g m 2g m R

µ

go µ

SS

dm g m ro2 ro4

f

f

(

)

24

/

/

/

/

/

.

Offset Voltage

• Ideal Op-Amp: vOut = ADMvIn

– When vIn = 0, vOut = 0.

• Transistor variation (mismatch)

introduces offset voltage

– Random offset

• Circuit topology can also cause

“systematic offsets”

+

+

_

-

vIn

vOut

vOS

_

25

+

_

+

vIn

+

-

vOut

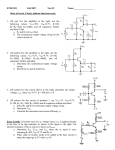

Bipolar Differential Amplifier with

Active Load: DC Analysis

Differential amplifier is completely balanced at dc when:

Current gain defect in current mirror upsets dc balance.

With BJTs in forward-active region, VEC4 adjusts to make

up for current-gain defect.

I

IC3 = IC1 = IC2 =IC4 =IEE/2.

If βFO is very large, current

€

mirror ratio is set by Q3 and

Q4 and is exactly 1 when VEC4

= VEC3=VEB.

C4

=I

(1+(VCE4 /VA ))

C1 # V

2 &

CE

3

(

%1+ V + β

$

A

FO4 '

As IC2 =IC4 and IC2

=IC1, MR must be 1.

This causes an equivalent

input offset voltage of

26

Bipolar Differential Amplifier with Active

Load: Differential-Mode Signal Analysis

Thevenin equivalent

output resistance:

Differential-mode voltage gain:

(

€

To eliminate offset error,

buffered current mirror active

load is used. Total short

circuit output current:

)

isc R R

"

%

L

th

$

A =

= g $r r R '' = g R

m2# o2 o4 L & m2 L

dm

v

dm

With added stages, the

resistance at the output

of the differential input

stage is:

27

Bipolar Differential Amplifier with Active

Load: Common-Mode Signal Analysis

Current forced in differential output resistance

is doubled due to current mirror action.

From small-signal equivalent:

Due to mismatches,

28

Active Loads in Op Amps: Voltage Gain

€

va v b vo

A =

= A A (1)≅ A A

vt1 vt2

vt1 vt2

dm v v v

id a b

µ µ

= f2 f5

4

If Wilson stage is used in first-stage active

load, Avt1 = µf2. If current source M10 is

replaced by a Wilson or cascode source,

Avt2 = µf5.Overall gain can be raised to:

Gain of output stage is approximately 1.

29

Active Loads in Op Amps: DC Design

Considerations

•

When op amp with active load is

operated in closed-loop

configuration, ID5 = I2, the output

current of source M10.

•

For minimum offset voltage, (W/

L)5 must be such that VSG5 = VSD4

= VSG3 precisely sets ID5 = I2 and

accounts for VDS and λ differences

between M5 and M10.

•

RGG, (W/L)6 and (W/L)7 determine

quiescent current in class-AB

output stage.

VGS11 can be used to bias output

stage in place of RGG.

•

30

CMOS Op Amp Analysis

Problem: Find small-signal characteristics of given CMOS op amp.

Given data: IREF = 100 µA, VDD = VSS = 5 V, VTN = 1 V, VTP = -0.75 V,

Kn‘ = 25 µA/V2, Kp‘ = 10 µA/V2, λ = 0.0125 V-1

Analysis:

I

= I /2 = I

=100µA

D2 1

REF

I

= I = 2I

= 200µA

2

REF

D5

€

As ID6 = ID7, VGS6 = VSG7 = VGS11 /2

250 µA

I

=I

=

(1.27V− 0.75V)2

D7 D6

= 33.7µA

€

€

X

2 V2

Bipolar Widlar Current Source

Cannot assume VBE=0.7V

Current through R is given by:&

#

$I

!

I

V

'V

V

$ REF

!

S

2

BE

1

BE

2

T

I

=

=

ln$

!

E2

R

R $$ I

I !!

O

S1 "

%

If transistors are matched,

&

$I

A #!

V

I =' I

= T ln$$ REF E 2 !!

F E2 R $ I

O

A !!

$

O

E1 "

%

R in Widlar source allows

adjustment of mirror ratio.

&

$

$

$

$

$

%

I

#

!

!

!

!

!

"

&

$

$

$

$

$

%

I

V

=V ln 1+ REF 'V ln REF

T

BE1 T

I

I

S1

S1

&

&

#

$

$ I

!

I #!

$

!

$ O !

O

V

=V ln 1+

! ' V ln$

!

T $I

BE 2 T $$ I

!

!

$

!

$

!

S2 "

%

% S2 "

Rout ! r '%%1+ g R $""

o2 &

m2 #

#

!

!

!

!

!

"

'

%

%

%

%

%

&

'I

= r 1+ ln% REF

o2

% I

& O

V ! KV

CS

A2

$ $"

S 2 " "" = Kr

o2

I " ""

S1 # #

I

Typically 1 < K < 10.

31

Designing Bipolar Widlar Mirror

• IC = ISexp(VBE/UT)

• IC2/IC1 = IS2/IS1exp(V(R)/UT)

• With known IRef, desired IOut, IC1 = IRef - IRef/β - IOut/β

• V(R) = UTln[(IC2 IS1)/(IC1 IS2)]

• R = IE2/V(R)

• Ex: IRef = 1mA, IOut = 250µA

– V(R) = 25mV ln(1/.25)=36mV

– R = 6.9 kΩ

32

MOS Widlar Current Source

I

#

!

I

(

W

/

L

)

2

O =1

!

O

1

1'

I

(W / L) !!

I

R I REF Kn1

REF

2"

REF

&

$

$

$

$

%

•If

IO is known, IREF can be directly

calculated

•If IREF , R and W/L ratios are known,

Current through R is given by:

we can write a quadratic equation in

terms of

•If IREF , IO, and W/L known, design

procedure similar to BJT Widlar

•Small-signal model is C-S stage w/

source degeneration 'R = r &$1+ g R #!

out o2 $%

m2 !"

33

MOS Wilson Current Source

•Feedback loop holds current equal by

adjusting VG3

•M3 absorbs excess output voltage, reduces

error due to VDS1 - VDS2

•During operation, all transistors

are in

active region.

-ID2 = IREF ,

ID3 = ID1 = IO,

-VGS3 = VGS1=VGS

1+2λV )

(

GS

I

=I

D2 D1

(1+ λVGS )

€

1+ 2λV

(

GS )

I =I

O

REF

(1+ λVGS )

34

where

MOS Wilson Current Source

From small-signal model,

vx = v3 + v1 = (ix gm3 vgs )ro3 ) + v1

v2 = v1 gm2 ro2 = v1 µf 2

v1 = ix /gm1

ix

( µf 2 1)

vgs = v2 v1 =

gm1

ix

vx = (ix gm3 (

( µf 2 1)))ro3 ) + ix /gm

gm1

⇥

vx

gm3

ROut =

= ro3 1 +

(µf 2 + 1) + 1/gm

ix

gm1

ROut ⇥ µf 2 ro3

compare to 1/λ for single FET

35

Bipolar Wilson Current Source

I =I

O REF #

%1+

$

€

&

2V

2

BE

+

β (β

+2) V (

FO FO

A '

Addition of extra BJT can balance the

circuit and reduce errors.

During operation, all transistors are

in active region. But some current is

lost at base of Q3 and current gain

error is formed by Q1 and Q2.

VCE2 = VBE+VBE3 -VBE4

= VBE

IREF = IC2 + IB3

VCE1 = VBE

(1+(VBE /VA ))

VCE2 = 2VBE

36

MOS Cascode Current Source

ID1 = ID3 = IREF Also IO = ID4 = ID2. So current

mirror forces output current to be approximately

equal to the reference current. If all transistors are

matched with equal W/L ratios,

VDS2 = VGS1+ VGS3 -VGS4 = VGS = VDS1

From the small-signal model,

37

Bipolar Cascode Current Source

IC1 = IC3 = IREF Also IO = IC4 = IC2. So current

mirror forces output current to be

approximately equal to the reference current.

If all transistors are matched,

VCE2 = VBE1+ VBE3 -VBE4 = VGS = VCE1

Recall general Ric equation:

✓

Ric = ro 1 +

RBB

RE

+ r⇡ + RE

◆

RBB=2/gm; RE=ro is large (>> other 2).

IB4 enters current mirror, reduces ROut by 1/2

38

Electronic Current Source Design

Example

Problem: Design IC current source to meet given specifications.

Given data: IREF = 25 µA, VSS = 20 V, λ = 0.02 V-1 , VTN = 0.75 V, Kn’ = 50 µA/V2, VA =

50 V, βFO = 100, ISO = 0.5 fA

Analysis: MR <0.1 % requires output current of 25 µA±25 nA when output voltage is

20 V. Choose 1GΩ for safety margin.

20V

Rout ≥

= 800MΩ

25nA

Cascode or Wilson source’s voltage-balanced MOS version must be used to meet

this value of VCS and for small MR. We can choose cascode source as it doesn’t

involve internal feedback loop.W/L ratios are all same as MR=1.

€

Using µf =500, λ =0.02/V and ID =25 µA gives value of Kn=1.25 mS. Since Kn =

Kn’(W/L) we need a W/L ratio of 25/1 for given technology.

X

Comparisons of the Basic Current Mirrors

39

Supply-Independent Biasing: VBE -based

Reference and Widlar Current Source

•

Output current is now logarithmically

Output current is determined by dependent on supply voltage. However, it is

base-emitter voltage of Q1 . For temperature dependent due to temperature

coefficients of both VBE and R.

high current gain,

Widlar source also achieves similar supply

independence of output current.

X

Reference Current Generation

•

•

Reference current is required by all current mirrors.

When resistor is used, source’s output current is directly

proportional to VEE.

•

Gate-source voltages of MOSFETs can be large and several

MOS devices can be connected in series between supplies to

eliminate large resistors.

VDD + VSS = VSG4+ VGS3 + VGS1 and ID3 = ID1 = I4

•

Change in supply directly alters gate-source voltage of

MOSFETs and the reference current.

BJTs can’t similarly be connected in series due to small fixed

voltage developed across each diode and exponential

relationship between voltage and current.

•

40

Supply-Independent Biasing: Bias Cell

Using Widlar Source and Current Mirror

Actual value of output current depends on temperature

and absolute value of R. IC1 = IC2 =0 is also a stable

operating point and start-up circuits must be included

in IC realizations to ensure that circuit reaches desires

operating point.

Base-emitter voltages of Q1 and Q4 can be used as

reference voltages for other current mirrors.

Assuming high current gain, pnp In MOS analog of the circuit, I = I and so

D3

D4

current mirror forces IC1 = IC2.

ID1 = ID2.

Emitter area ratio for Widlar

source is shown to be 20.

V

0.0749V

∴I

= T ln#%$20&(' =

C2 R

R

€

41

Reference Current Design Example

Problem: Design supply-independent current source to

meet given specifications.

Given data: output current = 45 µA,T=300 K, total

current< 60 µA VCC = VEE= 5 V, VA = 75 V, βFO = 100, ISO = 0.1 fA, VT = 25.88 mV

!

$

A

I R

# I

Analysis: ln # C1 E2 && = C2 ' ( 45µ A )(1k() =1.739

IC2 AE1 &&% V

T

I

A

C1 E2 ' 5.69

I

A

C2 E1

#

#

"

25.88mV

I

Also C2 ≥ 45µA = 3 . Choose IC2=5 IC1. Then AE2/ AE1 <28.45 Choosing

I

15µA

C1

25.88mVln(4)"$# 45µA%'&"$#1kΩ%'&

R=

= 797Ω

AE2/AE1 =20,

45µA

€

Finally, AE1=A, AE2=20 A, AE3=A, AE4=5 A with 35.88 mV across R.

€

42