* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download File - David Callen

Operational amplifier wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Printed circuit board wikipedia , lookup

Radio transmitter design wikipedia , lookup

Zobel network wikipedia , lookup

Index of electronics articles wikipedia , lookup

Two-port network wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Regenerative circuit wikipedia , lookup

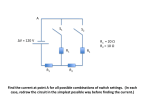

EE 414 Lab 3 Amplifier Design Tyler Bohlke David Callen Introduction In this lab we put into practice the methods of amplifier design learned in class. These methods include, but are not limited to simultaneous conjugate match, tuning, stability, and sparameter calculation. Our task was to design an amplifier that was stable from 300 kHz to 6.0 GHz with an operating frequency of 1.1 GHz. The circuit had a specification to maintain a bandwidth of +/- 5 MHz and have a gain of 20 log|𝑆21 | ≥ 16 − (6 ∗ 1.1) = 9.4 dB In order to be sure we achieve this gain, we were encouraged to add 3 dB to our calculated gain so we could ensure 20*log|S11| and 20*log|S22| (our return loss) stayed below -15 dB. The drawback to adding this gain was that it would ultimately make our circuit more difficult to stabilize along our desired frequency range. Step 1: Adding Solder Pads to the BJT The first step in designing our amplifier was to add MLIN structures (75x75 mil2) to each terminal of the BJT (emitter, base, collector). These structures are used to simulate the solder pads of the device once it is finally assembled. Figure 1 shows an MLIN used in our design. At this point it was necessary to add a 0.3 nH inductor to the device to model our ground once the physical circuit is built. This inductor is connected to a solder pad that is split in half, and it is the most accurate model for a ground we can obtain for our circuit. Figure 1: MLIN structure Step 2: Stabilizing the Initial Network The second step in designing our amplifier was to stabilize the transistor (BFP620) before we added any components to it. In order to stabilize the initial circuit, we needed find a suitable value for the stabilization resistor RSTAB. This was done by finding our desired stability using the following equation. Once we found this value of K, we inserted a 1Ω resistor at the base of the transistor and found a new K (all of this was done using ADS). We could now find the slope that these two values of K and the 1Ω resistor created, and from there, find a value for RSTAB that would ensure stabilization (K > 1, or µ > 1). All calculations to find RSTAB were done using either ADS or MATLAB. The MATLAB code and final values are attached at the end of lab. Our final value for RSTAB came out to be 2.4826Ω. At this point the transistor portion of our circuit is complete. Figure 2 shows our circuit at this point in the design stage. Figure 2: The BJT with solder pads, ground, and RSTAB Step 3: Simultaneous Conjugate Matching Once the BJT was modeled with a proper stabilization resistor and our ground, it was time to match each end to 50Ω terminations. To do this, first we had to convert our s-parameters into z-parameters, with a normalization impedance (Z0) of 50Ω. We decided to use MATLAB for the conversions, and the MATLAB code can be found at the end of this lab. For simplicity’s sake, we used the Smith chart tool (in ADS) to obtain values for our inductors and capacitors for the simultaneous conjugate match. For port S11 we chose to go with a high-pass match, and for port S22 we again used a high pass match. The reason we chose high pass for each port was because we would ultimately use the series capacitors to facilitate our DC blocking needs. Figure 3 shows the ADS Smith chart tool in use. The initial value for our series capacitor at the port 1 match was 14.4462pF, and our parallel inductor was 4.3383nH. At port 3, our initial value for the series capacitor was 1.2246pF and our parallel inductor had a value of 14.580nH. It is worthwhile to note that the initial value for our matching components are only to get our terminals to match our Zin* and Zout*. Because we will be Figure 3: The Smith chart tool used to calculate our matching networks. adding more components to our amplifier, the matching networks will be frequently tuned to new values to ensure we maintain our proper gain and stability. This conjugate match simply gives us a nice starting point. Step 4: Stabilization Across all Frequencies Once the simultaneous conjugate match was complete, it was time to stabilize our amplifier across the necessary frequency range. For this lab, our range was from 300 kHz to 6.0 GHz. Stabilization requires us to add loss to the amplifier at frequencies other than the design frequency. To do this, we must place either a series LC component in parallel with a series resistor (figure 4), or a parallel LC component in series with a shunt resistor (figure 5). When we do this, we chose our inductor and capacitor so they Figure 4: Series LC in parallel with R resonate at the design frequency. With the series LC in parallel with the resistor, at resonant frequency (1.1GHz) they act as a short circuit, and so the resistor will not affect the loss at that frequency. In contrast, the parallel LC component in series with the resistor act as an open circuit at resonant frequency, so the signal will not pass Figure 5: Parallel LC in series with R through those components, which are connected to ground. By arranging where we place each of these components, we can effectively stabilize our amplifier across all frequencies. We chose to place each of these blocks at port 2 of our amplifier, because at our design frequency, that location gave us the most gain and least amount of instability. We were able to simply tune the circuit to where (at this point) 20log|S11| and 20log|S22| were approximately -45 dB and our µ value (stability) was greater than 1 for all required frequencies. Step 5: Adding Real Components and RETMA Values At this point, this amplifier has it matching networks in place, is stable across the desired frequency range, and has a return loss (20*log|S11|) of around -35dB to -40dB. We are not finished with the design because all of our connections and components are ideal, and we are using non-RETMA values for our resistors, capacitors, and inductors. It is at this point where must design our circuit to the point where it can be realistically fabricated. We do this by introducing solder pads (MLIN), inserting our physically modeled R, L, and C components, and then finally changing those component values to RETMA values. We started with the solder pads. We needed at least a 75x75mil2 solder pad to connect one terminal to another. Several terminals had at least 3 necessary connections which meant we needed to adjust the size of the solder pad in order to acclimate it to multiple connections. Figure 6 shows a connection of four terminals, which required us to adjust the physical dimension of the pad by doubling it. As we added more and more pads, the circuit would slowly start lose gain, and at some point would become unstable. This was dealt with by meticulously adjusting our component values for our Figure 6: A four terminal solder pad matching networks. Depending on the location of the pad, it would act slightly inductive, or slightly capacitive, and we would tune our matching networks accordingly to absorb the parasitics. Once all of the solder pads were in place, and our matching networks were sufficiently tuned, it was time to add our models for our resistor, capacitor, and inductor. These models were found and adjusted in the previous lab. One by one the models were inserted and the circuit was tuned to maintain stability. After the models were all in place, it was time to switch them all to RETMA values. These last two steps were the largest contributors to our loss of gain throughout the design process. Before we started inserting component models and RETMA values, we sitting at around -38 dB for return loss, after everything was complete (up to this point) our return loss was a respectable -23.469 dB for S11 and -20.518 dB for S22. The Final Circuit Our final completed circuit can be seen in figures 7, 8, and 9. We have the DC connections set up, but no DC bias regulator circuit. That will be designed in a future lab (the oscillator). The full schematic can be found in the appendix at the end of this lab report. Figure 7: The source terminal and Γin = Γs* match Figure 8: The BJT and DC connection Figure 9: The load terminal and Γout = Γl* match Conclusion In this lab we were able to successfully design and simulate an RF amplifier with a gain of 9.4dB, a return loss of -23 dB and -20 dB for S11 and S22 respectively, and stability from 300 kHz to 6.0 GHz. This was an intense and detail-oriented lab. The most difficult part was tuning our component values to ensure stability and the lowest possible return loss. While the effort put forth was tremendous, the information gained was just as worthwhile. It is satisfying to see how an amplifier of this sort is designed from start to finish, and it gave us an insight as to how more effectively design amplifiers in the future. Appendix 1. 2. 3. 4. The Full image of our final circuit The return loss (top) and stability verification (bottom) of the final circuit The MATLAB code for finding input and output impedance (Zin and Zout) The MATLAB outputs for input and output impedance (Zin and Zout)