* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download High Power DC/DC Converter Topologies

Audio power wikipedia , lookup

Wireless power transfer wikipedia , lookup

Power factor wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Electrification wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electric power system wikipedia , lookup

Utility frequency wikipedia , lookup

Electrical ballast wikipedia , lookup

Stepper motor wikipedia , lookup

Current source wikipedia , lookup

Power engineering wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Stray voltage wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Surge protector wikipedia , lookup

History of electric power transmission wikipedia , lookup

Transformer wikipedia , lookup

Voltage regulator wikipedia , lookup

Electrical substation wikipedia , lookup

Power inverter wikipedia , lookup

Integrating ADC wikipedia , lookup

Opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Three-phase electric power wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Transformer types wikipedia , lookup

Mains electricity wikipedia , lookup

Resonant inductive coupling wikipedia , lookup

Power MOSFET wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Alternating current wikipedia , lookup

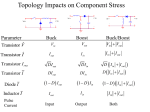

HVDC converter wikipedia , lookup

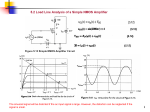

The Power to Amaze. POWER CONVERTER TOPOLOGY TRENDS Name: Steve Mappus Systems Engineer Date: October 02, 2014 www.psma.com, [email protected] Agenda Topology Overview Non Isolated Topologies Isolated DC-DC Derivatives Single Ended Topologies Transformer Reset Techniques Flyback Converter Forward Converter Double Ended Topologies Push Pull Half Bridge Full Bridge Summary 2 Isolated Power Topology Derivatives BOOST VO 1 = Vi 1 − D BUCK-BOOST VO D =− Vi 1− D VO =D Vi BUCK NON-ISOLATED ISOLATED SINGLE-ENDED SINGLE-ENDED LOW POWER (< 100 W) FLYBACK MID-POWER (100 W - 500 W) HIGH-POWER (> 500 W) Power levels numbers for general discussion only. Exceptions aplenty. DOUBLE-ENDED PUSH-PULL FORWARD 2-SWITCH 2-SWITCH ACTIVE CLAMP ACTIVE CLAMP HALF BRIDGE LLC FULL BRIDGE 8 “Mainstream” Converter Topologies Non-Isolated 1. Boost 2. Buck-Boost 3. Buck Isolated 4. Flyback 5. Forward 6. Push-Pull 7. Half Bridge 8. Full Bridge ZVT/PHASE SHIFT HARD SWITCHED 3 Other Topologies? Numerous Variations Exist Sepic Cuk Current Fed Buck Tapped Inductors Multiple Outputs Interleaving More? Different Ways to Operate Them Voltage Mode Control Current Mode Control Digital Control Variable Frequency CCM, DCM, BCM ZVS ZCS Synchronous Rectification Some Practical Converter Topology Advice Most power conversion requirements can be met using one or more of the 8 mainstream topologies Save more difficult topologies for unique application requirements Beware of publications proclaiming the “best” topology 4 Multi-Stage Topology Typical Distributed Power System AC Line 85 V < VAC < 265 V 48 V to 12 V IBC (Intermediate Bus Converter) VDC = 400 V 400 V to 48 V Bus Converter Telecom Rectifier VPOL_1 < 5 V PFC Boost High Power DC-DC Scalable, efficient, complex protection functions, sequencing, redundancy, digital control, etc Efficiency example VPOL_N < 5 V η SYS = η PFC ×η DC ×η DC ×η POL POL DC-DC η SYS = 98% × 95% × 95% × 96% = 84.9% 5 Single-Stage Topology PFC Flyback AC-DC AC EMI PFC FL7733A Difficult to meet: Low cost, high PF, low THD, high efficiency, wide VIN with single-stage η = 84.9% 6 Non-Isolated Converter Topologies 7 Boost Converter (Step Up) VIN(t) L VOUT VGS(Q) VOUT VL D COUT CBYP VAC Q VDS(Q) IL BCM IL IDS(Q) VIN(t) L VOUT VL ID D COUT CBYP VAC Q IL Inductor volt-second balance: 〈𝑉𝑉𝐿𝐿 〉 𝑇𝑇𝑆𝑆 = 𝑉𝑉𝐼𝐼𝐼𝐼(𝑡𝑡) × 𝑡𝑡𝑂𝑂𝑁𝑁 + ��𝑉𝑉𝐼𝐼𝐼𝐼(𝑡𝑡) − 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 � × 𝑡𝑡𝑂𝑂𝐹𝐹𝐹𝐹 � = 0 𝑉𝑉𝐼𝐼𝐼𝐼(𝑡𝑡) × (𝑡𝑡𝑂𝑂𝑂𝑂 + 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 ) = 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 𝑉𝑉𝐼𝐼𝐼𝐼(𝑡𝑡) × 𝑇𝑇𝑆𝑆 = 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 tON tOFF TS Boost CCM transfer function: 1 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 𝑇𝑇𝑆𝑆 = = 𝑉𝑉𝐼𝐼𝐼𝐼(𝑡𝑡) 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 1 − 𝐷𝐷 VIN < VOUT Most efficient at lower D Continuous input current CCM, BCM, DCM modes 8 L VIN(t) Operating Mode VOUT D IL CBYP COUT VAC CCM, BCM or DCM Q VDS VGS IL(PK) IL(PK) IL(PK) ∆IL IL(MIN) ∆IL IL ∆IL IL 0A 0A 0A VOUT VOUT VDS VDS VDS VIN 2x(VIN – VOUT) 0V VGS 0V VGS 0V VGS 0V 0V tON tOFF t 0V tON tOFF tRES t tON tOFF t tD TS TS TS CCM (Fixed Freq) BCM (Variable Freq) DCM (Fixed Freq) 9 Buck Converter (Step Down) L VIN CIN VOUT VIN+VF VL Q VGS(Q) COUT VDS(Q) D VIN IL VD VIN-VOUT VL L VIN CIN -VOUT VOUT VL Q VF D IL COUT IDS(Q) ID tON tOFF TS Inductor volt-second balance: 〈𝑉𝑉𝐿𝐿 〉 𝑇𝑇𝑆𝑆 = [(𝑉𝑉𝐼𝐼𝐼𝐼 − 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 ) × 𝑡𝑡𝑂𝑂𝑂𝑂 ] − 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 = 0 𝑉𝑉𝐼𝐼𝐼𝐼 × 𝑡𝑡𝑂𝑂𝑂𝑂 = 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × (𝑡𝑡𝑂𝑂𝑂𝑂 + 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 ) 𝑉𝑉𝐼𝐼𝐼𝐼 × 𝑡𝑡𝑂𝑂𝑂𝑂 = 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑇𝑇𝑆𝑆 Buck CCM transfer function: 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 𝑡𝑡𝑂𝑂𝑂𝑂 = = 𝐷𝐷 𝑉𝑉𝐼𝐼𝐼𝐼 𝑇𝑇𝑆𝑆 VIN > VOUT Most efficient at higher D 10 Buck-Boost Converter (Inverting) D -VOUT VGS(Q) VIN VIN CIN Q L VIN VL D CIN Q -VOUT COUT L -VOUT VDS(Q) VL IL VIN VIN+|-VOUT| COUT VOUT-VF IL IDS(Q) VL ID IL Inductor volt-second balance: 〈𝑉𝑉𝐿𝐿 〉 𝑇𝑇𝑆𝑆 = 𝑉𝑉𝐼𝐼𝐼𝐼 × 𝑡𝑡𝑂𝑂𝑂𝑂 + 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 = 0 𝑉𝑉𝐼𝐼𝐼𝐼 × 𝑡𝑡𝑂𝑂𝑂𝑂 = −(𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 × 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 ) 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 𝑡𝑡𝑂𝑂𝑂𝑂 /𝑇𝑇𝑆𝑆 𝑡𝑡𝑂𝑂𝑂𝑂 /𝑇𝑇𝑆𝑆 = −� � = −� � (𝑇𝑇𝑆𝑆 − 𝑡𝑡𝑂𝑂𝑂𝑂 )/𝑇𝑇𝑆𝑆 𝑉𝑉𝐼𝐼𝐼𝐼 𝑡𝑡𝑂𝑂𝑂𝑂𝑂𝑂 /𝑇𝑇𝑆𝑆 tON tOFF TS Buck-Boost CCM transfer function: 𝑉𝑉𝑂𝑂𝑂𝑂𝑂𝑂 𝐷𝐷 = −� � 𝑉𝑉𝐼𝐼𝐼𝐼 1 − 𝐷𝐷 VIN < VOUT or VIN > VOUT Used for negative VOUT 11 Single Ended Converter Topologies 12 Benefits of a Transformer 1. Provides primary to secondary safety isolation – subject to regulatory standards DC Output AC AC Load (or DC) 2. Voltage conversion resolution L VIN Q1 CIN D1 D1 VO CO VO =D VIN NP VIN NS L D2 CO CIN VO N VO = S D VIN N P Q1 Ex: For FSW=300kHz (TSW=3.33µs), NP:NS=4:1, 36V<VIN<75 and VO=5V Buck Converter Isolated Buck (Forward) Converter 6% < D < 14% 200 ns < tON < 467 ns 27% < D < 55% 900 ns < tON < 1.8 µs 3. Potential ground differences between primary and secondary 4. Multiple outputs can be regulated/quasi-regulated 13 Transformer Characteristics NP NS CP-S(MUTUAL) VOUT VIN LP(LEAK) RP NP RCORE Perfect coupling between Np:Ns No energy storage VIN NS RS NS LMAG CS(W) CP(W) Ideal transformer NP LS(LEAK) Parasitic Transformer Model VGS VOUT Overshoot/ringing due to Leakage Inductance Flyback “transformer” Really a coupled inductor Primary energy stored during tON Power transferred during tOFF VDS CCM Flyback (VDS = 32 V, VLK = 12 V) 14 Single Ended Topologies Defined Single Ended – Transformer operation limited to first quadrant B ∝ Vt B ∝ Vt +BSAT B2 +BSAT B2 ∆B ∆B B1 UNGAPPED H ∝ NI -BSAT -BSAT (a) Forward Converter Transformer Hysteresis Reset Circuit NP NS D2 D NP CO VIN CIN Q1 (b) Forward Converter H ∝ NI (c) Gapped Flyback “Transformer” L D1 GAPPED B1 RESET CIRCUIT: 1. Third winding 2. RCD reset 3. Resonant reset 4. Active clamp reset NS CO VO CIN Q1 (b) Flyback Converter 15 Flyback Converter Derivation D VIN CIN Q -VOUT D n:1 COUT VIN L VOUT COUT CIN LM Q (a) (d) D VIN CIN 1:1 Q -VOUT VOUT n:1 COUT VIN L COUT CIN LM Q (b) D VIN CIN 1:1 Q LM (e) -VOUT COUT D a) b) c) d) e) Non-isolated buck-boost Coupled inductor buck-boost Isolated buck-boost Isolated flyback converter D can be in return path (c) 16 Flyback Converter CCM Operation VOUT PWM NP n:1 NS VIN COUT CIN LM Q 0 VIN+(NP/NS)VOUT VDS D 0 (a) Flyback Converter CCM Transfer Function VO N S D = × VIN N P 1 − D Limitations Q1 switching loss (hard switched) D2 conduction loss Q1(VDS) > VIN 50% duty cycle limit Right half plane zero in CCM Output rectifier reverse recovery VOUT 0 VS -(NS/NP)VIN IQ1 0 ID1 0 IL 0 (b) CCM Waveforms 17 Quasi-Resonant Flyback Conventional Valley Switching Wide frequency variation depends on output load condition iD T1 t Output load decreases vDS Operating frequency increases t fS [Hz] iD PSwitching Loss ∝ COSSV DS2 f S T2 t vDS t Output Power [W] 18 Quasi-Resonant Flyback Window Valley Switching Tsmax=10.8us Light Load Frequency variation depends on output load conditions tB=7.8us tW=3.0us (a) fs_A=110kHz Operating frequency is within narrow variation (127.5 kHz ~ 92.6 kHz) (b) fs_B=122kHz vDS (100V/div) (c) fs_C=127.5kHz iD (100mA/div) (d) Time scale 2usec/div fs_D=92.6kHz Heavy Load 19 Two-Switch, Quasi-Resonant Flyback VIN (FROM PFC) PBIAS C3 D5 D4 FAN7382 Q1 1 VCC VB 8 2 HIN HO 7 3 LIN VS 6 VHS C2 VLED D1 D2 4 COM LO Q2 5 VA R2 FAN6300H DET HV 8 2 FB NC 7 3 CS VDD 6 4 GND GATE 5 C1 R1 R3 1 D3 CC FB CV R4 ACIN PBIAS RDY (FROM PFC) 20 Two-Switch Quasi-Resonant Flyback Switching Waveforms VIN+VHS VGS(HS) VIN PBIAS VGS(LS) 0V IDET(SOURCE)>30µA tDELAY=200ns 0V VA VA 5µs VO OVP 2.5V 0.7V VDET Quasi-resonant, variable frequency HS and LS MOSFETs switch synchronously Switching period, TS = tOFF + tf + tON Inductor current switches from 0 A (ZCS) every switching cycle VDS 0V ZVS → VOUT > 2×VIN Valley switch → otherwise Window valley switching IDS 0A ID 0A VRO 2 VIN 2 VDS VRO 2 VIN 2 0V tOFF tf tON TS 21 Two-Switch Quasi-Resonant Flyback Measured Waveforms VDS Valley Switching on First Valley VOUT < ½ VIN D = 42% FS = 63 kHz POUT = 85 W Extended Window Valley Switching VOUT < ½ VIN D = 11% FS = 68 kHz POUT = 24 W 22 Forward Converter Basics L D1 PWM VIN CIN D3 NR NP NS D2 CO VO 0 VR+VIN VDS(Q1) VIN Q1 0 VIN (a) Forward Converter with Reset Winding VP 0 VR = −VIN N × P NR 0 IMAG 0 IQ1 VO N = S ×D V IN N P 0 IL 0 ID1 Limitations 0 ID2 Really a Transformer Coupled Buck CCM Transfer Function Q1 switching loss (hard switched) D2 conduction loss Q1(VDS) > 2 VIN 50% duty cycle limit (NP:NR = 1:1) (b) DCM Waveforms (D<0.5) 23 Problems with Duty Cycle > 50% VP VIN Equal Vxt Area Common practice is to use 1:1 bifilar transformer winding for NP:NR 0 t − VIN × IMAG DTS D = 40% NP NR D2TS D 3T S t TS VP Unequal Vxt Area VIN D = 67% t D=40% − VIN × D=67% NP NR IMAG DTS D2TS TS Converter operates in DCM Transformer is completely reset on every switching cycle 2TS 3TS Converter wants to operate in CCM Transformer can NOT reset on every switching cycle IMAG increases due to volt second product imbalance Transformer saturation will result Operation beyond D = 50% requires additional reset voltage t 24 Duty Cycle Greater Than 50% NP NR NS For NP:NR = 1:2 VDS (V) VDS vs Vin Third Winding Reset VDS=3VIN 216 204 192 180 168 156 144 132 120 108 96 84 72 Q1 VP 36 42 48 54 60 66 72 VIN Equal Vxt Area } } D=67% Vin (V) − VIN × Np:NR=1:1 VDS Np:NR=1:2 t NP:NR=1:1 NP:NR=1:2 NP NR IMAG DTS D2TS TS 2TS 3TS t Conclusion: Reset winding technique, D > 50% not practical for high VIN applications due to additional MOSFET VDS stress 25 Active Clamp Forward Converter L D1 CCL NP NS Advantages CO D2 Q2 CIN Q1 PWM 0 Q2 VGS 0 VIN+VCL Q1 VDS 0 IMAG ICL 0 IQ1 0 IP Reduced MOSFET VDS voltage stress Higher efficiency through ZVS Use of parasitic elements Higher frequency operation Suitable for off-line (HS clamp) or DC-DC (LS clamp) Disadvantages Conditional ZVS only Dual primary side gate drive with accurate deadtime control and max duty cycle clamp required Poor transient response due to CCL Transfer Function VO N = S ×D V IN N P VIN 0 VP VRESET 26 Active Clamp Forward Converter Two Versions D1 CCL NP NS L D2 D1 NP CO NS L D2 CO CCL Q2 CIN CIN Q2 Q1 PARAMETER VDS VRESET VCL (a) Q1 High-Side Active Clamp (Flyback Clamp) HIGH-SIDE ACTIVE CLAMP (off-line) (b) Low-Side Active Clamp (Boost Clamp) LOW-SIDE ACTIVE CLAMP (telecom) 1 × V IN 1− D D × V IN 1− D 1 × V IN 1− D D × V IN 1− D D × V IN 1− D 1 × V IN 1− D CCL (applied voltage) Lower voltage by VIN volts Highest VCL occurs at DMAX Higher voltage by VIN volts Not practical for off-line CCL (cap value) Same value as low-side for given ripple voltage Same value as high-side for given ripple voltage Clamp MOSFET (Q2) N-Channel Can be used for > 500 V P-Channel Can be used up to 500 V Gate Drive Gate drive transformer required Level shifting gate drive required 27 Active Clamp Forward Converter Zero Voltage Switching (ZVS) ZVS occurs when the voltage across the MOSFET, VDS, is positioned to “zero volts” prior to the start of the next switching cycle. Benefits of ZVS Reduced switching losses Higher operating frequency possible (smaller passive component size) Higher converter efficiency Increased reliability Reduced radiated emissions (EMI) VDS ID PSW=VDS x ID x FSW (a) Hard Switching (b) “Ideal” ZVS 28 Active Clamp Forward Converter Zero Voltage Switching (ZVS) Parasitic elements can be used to benefit ZVS CD1 CP-S(MUTUAL) RP CCL Q2 CDS LP(LEAK) NP RCORE CP(W) D2 LS(LEAK) NS RS D1 LMAG CS(W) L D2 CD2 CO CDS Q1 D1 VDS Active Clamp Forward converter uses fixed frequency resonant transitions to achieve ZVS when specific operating conditions are met 29 Single Ended (<500W) 2 Switch Forward Converter Advantages Q2 D4 D1 D3 CIN NP L NS D2 Q1 0 VIN VIN/2 0 VIN/NP 0 -VIN/NP PWM (Q1, Q2) VDS (Q1, Q2) VS ID3, ID4 0 IQ1, IQ2 0 0 Disadvantages Limited to less than 50% duty cycle High side gate drive required for Q2 Hard switching Transfer Function IMAG 0 0 IO CO Ruggedness MOSFET voltage stress limited to VIN Magnetizing energy recycled by D3, D4 Universal input, 150 W < P < 500 W VO N = S ×D V IN N P IL ID1 ID2 30 Single Ended (>1kW) Interleaved 2 Switch Forward Converter Advantages Can operate multiple power stages out of phase Ripple current cancellation at output capacitor Reduced RMS current at input capacitor Multiple stages can add up to kW of power Smaller output inductors can improve transient response Q2 D4 D1 D3 CIN NP NS L CO D2 Q1 Q4 D8 D5 D7 NP NS L D6 Q3 Disadvantages Design complexity PCB layout can be challenging Qn Dn Dn Dn NP NS L Dn Qn 31 Double Ended Converter Topologies 32 Double Ended Topologies Defined Double Ended – Transformer operation occurs in first and third quadrants B ∝ Vt B ∝ Vt +BSAT B2 B2 (RCD Reset) ∆ B B1 H ∝ NI ∆B +BSAT B2 ∆ B (Active Clamp) H ∝ NI B1 B1 -BSAT -BSAT Half-Bridge, Full-Bridge Active Clamp Forward Symmetrical operation between first and third quadrants No transformer reset circuitry required “Single ended” but operates slightly into the third quadrant Normal Flux Imbalance Saturation Primary Current 33 Double Ended (<500 W) Half Bridge Converter (Symmetrical) D1 Q2 C1 Advantages L NP NS CO VP CIN C2 NS Q1 D2 PWM, Q1 PWM, Q2 VIN/2 -VIN/2 VIN VDS(Q1, Q3) VIN VDS(Q2, Q4) VP IP ID1 ID2 IO IL Better transformer utilization MOSFET voltage stress limited to VIN Best for high VIN off line applications up to 500W Single winding primary Transformer balanced by C1 and C2 Asymmetric and resonant versions can ZVS Disadvantages Totem pole primary gate drive High primary current Possible cross conduction between Q1 and Q2 Hard switching Transfer Function VO N = 2× S × D VIN NP 34 Asymmetrical Half Bridge Converter Vd 0 Symmetric square waveform + Vd + Vp + Vp - - - Vd 0 Asymmetric square waveform 1:1 What if an asymmetric square wave is introduced to the transformer? Transformer will be saturated What if an asymmetric square wave is introduced to the transformer in series with a DC blocking capacitor? Not saturated due to the voltage of the blocking capacitor, CB + VCB + Vd 0 - CB + Vp + Vp - 1:1 Same area 0 VCB 35 Asymmetrical Half Bridge Converter D=0.46 D=0.23 D1 Q2 Q2 (D) NP NS Q1 (D) VIN/2 NS VP Q1 -VIN/2 CO VP CIN VIN/2 L D2 -VIN/2 IP CB VO N = 2 × S × D × (1 − D ) V IN NP Asymmetrical Gate Drive (a) Symmetrical HB waveforms D=0.46 D=0.23 Q2 (D) Q1 (1-D) VIN-VCB VIN-VCB Equal Area VP VCB VCB IP (b) Asymmetrical HB waveforms Q2 modulated by D Q1 driven by 1-D Fixed dead time between Q1 and Q2 Dead time optimized for ZVS and anti cross conduction Fixed frequency ZVS PWM operation Near D=0.5, operation is same as symmetrical HB BUT, excessive voltage stress is applied to secondary rectifier at VIN(MAX) 36 Asymmetrical Half Bridge Converter Secondary rectifier voltage stress: VD 2 = VO × (1 − D ) Reverse recovery and parasitic ringing Wide ∆D range requires use of high voltage rectifiers Converter operates best near D = 0.5 40 Diode Voltage Stress (V) VD1 = D × VO Asymmetrical Half Bridge VD vs D, VO=50 V 35 30 25 20 15 10 5 0 0.20 0.23 0.26 0.29 0.32 0.35 0.38 0.41 0.44 0.47 0.50 Advantages Duty Cycle VD1 Fixed frequency ZVS Constant power transfer (D and 1-D) reduces output ripple Power stage can be controlled using any active clamp PWM controller VD2 Disadvantages High voltage stress on secondary rectifier Poor transient response due to blocking capacitor, CB 37 LLC Resonant Half Bridge Converter Square wave generator: produces a square wave voltage, Vd by driving switches, Q1 and Q2 with alternating 50% duty cycle for each switch. Resonant network: consists of Llkp, Llks, Lm and Cr. The current lags the voltage (inductive) applied to the resonant network which allows the MOSFET’s to be turned on with zero voltage. Rectifier network: produces DC voltage by rectifying AC current Ip Im Square wave generator Ids2 resonant network Q1 Ip Vin Vd Q2 Llks Ro Im ID + VO Lm Ids2 Io ID n:1 Llkp Rectifier network Vd (Vds2) Vin Cr Vgs1 Vgs2 38 LLC Converter Characteristics fP = Two resonant frequencies (fo and fp) exist The gain is fixed at resonant frequency (fo) regardless of the load variation fO = 1 2π Lr Cr LLC Resonant Converter fp fo 1.8 Q= Q=0.2 1.6 M @ f = fo = 1 Lr / Cr Rac Q= 1 Q= 0.8 1.4 Q= 0.6 Q= 0.4 1.2 Gain Peak gain frequency exists between fo and fp As Q decreases (load current decreases), the peak gain frequency moves to fp and higher peak gain is obtained As Q increases (load current increases), peak gain frequency moves to fo and the peak gain drops 1 2π (LM + Lr )Cr Q= 0.2 1.0 Q=1 0.8 = M 1= when f s f o 0.6 M= 2nVO Vin 0.4 40 50 60 70 80 90 100 110 120 130 140 Freq (kHz) 39 LLC Topology Variations Primary Side Variation Lr Q1 Q1 Secondary Side Variation ½ Cr Lr Lm Ro Cr + Ro + VO VO - - Lm VIN VIN Q2 Q2 ½ Cr Transformer across the high side MOSFET Split resonant capacitor Q1 Q1 Full bridge rectifier with single winding 2 Rectifier diode with center tab winding Ro Ro Lr VO VO - - Lm Q2 Lm Cr Transformer across the low side MOSFET VIN + ½ Cr Lr VIN + Q2 ½ Cr Voltage doubler rectifier with single winding Synchronous rectifier with center tab winding Split resonant capacitor with clamping diode 40 LLC Resonant Half Bridge Converter Advantages of the LLC resonant converter Narrow frequency variation range over wide load range Zero voltage switching even at no load condition Reduced switching loss through ZVS Improved efficiency and EMI When the two magnetic components are implemented with a single core (use the leakage inductance as the resonant inductor), one component can be saved Disadvantages of the LLC resonant converter Can optimize performance at one operating point, but not with wide range of input voltage and load variations (too wide frequency range) Difficult to regulate the output at no load condition Significant current may circulate through the resonant network, even at the no load condition Quasi-sinusoidal waveforms exhibit higher peak values than equivalent rectangular waveforms High output current ripple 41 Double Ended (<500W) Push Pull Converter D1 NP NS NP NS L Advantages CO CIN Q2 Q1 D2 PWM, Q1 PWM, Q2 IQ1 IQ2 2VIN VDS(Q1) 2VIN VDS(Q2) ID1 Lower primary current compared to HB Best for lower VIN, such as telecom DCDC of US Line Voltage Simple low-side gate drive Low output current ripple Disadvantages High voltage (2xVIN) on primary MOSFETs Transformer flux walking (VMC only) Center tapped transformer structure Hard switching Transfer Function VO N = 2× S × D V IN NP ID2 IO IL 42 Double Ended (>500W) Full Bridge Converter (PWM) D1 Q1 L NS CO NP CIN NS Q2 Advantages Q3 Q4 D2 Gate, Q1 Gate, Q2 Gate, Q3 Gate, Q4 VIN -VIN VIN VDS(Q1, Q4) VIN VDS(Q2, Q3) VP MOSFET voltage stress limited to VIN Twice the power compared to half bridge Single winding primary Disadvantages Dual, totem pole primary gate drive Hard switching (Non-ZVT) Parasitics degrade circuit performance Circuit complexity Transfer Function VO N = 2× S × D VIN NP IP ID1 ID2 IO IL 43 Double Ended (>500W) Phase Shifted Full Bridge Converter D1 Q1 Advantages L Q3 NS CO NP CIN NS Q2 Q4 D2 Gate, Q1 Gate, Q2 Gate, Q3 Gate, Q4 VIN VP -VIN VIN VDS(Q1, Q4) VIN VDS(Q2, Q3) IP ID1 IO Power Freewheel Power Freewheel ID2 IL High Efficiency ZVS Highest single stage processing power MOSFET voltage stress limited to VIN Twice the power compared to half bridge Full wave rectified secondary Single winding primary Excellent choice for EU line voltage (PFC preregulator) with output power >1kW Disadvantages Dual, high side primary gate drive Circuit complexity High circulating primary current for ZVS Loss of ZVS at light load current Transfer Function VO N = 2× S × D VIN NP 44 Phase Shifted Full Bridge Converter ZVS Waveforms Q1 Q3 Q2 Q4 Q2 (P→A) VDS, VGS Q1 Q3 Q2 Q4 Q4 (A→P) VDS, VGS (a) IO = 100% (b) IO = 35% (c) IO = 0% A=“Active” or power phase P=“Passive” or freewheel phase 45 Current Doubler Rectifier What is it? - A full wave alternative rectification technique compatible with all double ended converter topologies Derivation of Current Doubler L D1 NS D1 NS VO CO L D1 V VO CO D2 D2 (b) D1 NP CO VO NP NS CO D1 D2 (c) Current Doubler L1 L1 I V D2 (a) NS VO CO I V I NS NS VO CO NP NP D1 L1 Q1 VO NP (d) VO CO NS Q2 D2 L2 L2 (f) OR L2 (g) D2 (e) 46 Phase Shifted Full Bridge with Current Doubler Gate, Q1 L1 Q1 Q3 Gate, Q2 CO D1 Gate, Q3 CIN D2 Q2 Gate, Q4 Q4 L2 t0 t1 VP L1 Q1 Q3 IP CO D1 CIN VL1 D2 Q2 IL1 Q4 L2 t1 t2 VL2 IL2 IO=IL1+IL2 L1 Q1 Q3 CO D1 CIN t0 t1 t2 t3 t4 D2 Q2 Current Doubler Timing Diagram (PSFB Application) Q4 L2 t2 t3 L1 Q1 Q3 CO D1 CIN D2 Q2 Q4 L2 t3 t4 Better thermal distribution for higher current outputs Each inductor carries half the load current at half the switching frequency Ripple currents cancel as a function of D Single winding secondary 47 High Power Topology Summary Topology Transformer Primary Switches VDS “Ideal” Application CCM Boost Inductor (non-isolated) 1 VOUT High power PFC > 300 W Interleaved PFC > Several kW BCM Boost Inductor (non-isolated) 1 VOUT PFC < 300 W Interleaved PFC < 1 kW Forward Single-end 1 2xVIN < 200 W, universal off-line or telecom Active Clamp Single-end 2 2-Switch Forward Single-end 2 VIN < 500 W, universal off-line, PFC preregulator Half Bridge Double-end 2 VIN < 500 W, EU off-line, Intermediate Bus Converters Push Pull Double-end 2 2xVIN < 500 W, telecom or low VIN (< 200 V) Full Bridge Double-end 4 VIN > 500 W, universal off-line Phase Shifted FB Double-end 4 VIN > 1 kW, universal off-line or telecom, highest efficiency required Current Doubler Double-end NA NA Any double-ended topology, low VOUT, high IOUT most benefit VIN × 1 1− D < 500 W, universal off-line or telecom, highest efficiency required 48 Summary Power Converter Topology Trends: Advanced control algorithms breathing new life into classic topologies… Buck → multiphase buck Boost → BCM boost Flyback → QR flyback Forward → active clamp forward Half bridge → LLC resonant Full bridge → PSFB The innovation trends are in new control methods that are pushing the limits of power processing, converter size, and operating frequencies. Better uses of zero-voltage switching and zero-current switching for lower stresses Better use of parasitic elements Digital techniques including non-linear and multi-variant control Better synchronous rectification timing control 49