* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download ee 586 (vlsi systems design)

Skin effect wikipedia , lookup

Single-wire earth return wikipedia , lookup

Alternating current wikipedia , lookup

Power electronics wikipedia , lookup

Power inverter wikipedia , lookup

Semiconductor device wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Power MOSFET wikipedia , lookup

Integrated circuit wikipedia , lookup

Telecommunications engineering wikipedia , lookup

Time-to-digital converter wikipedia , lookup

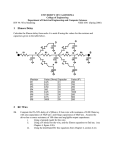

EE 586 (VLSI SYSTEMS DESIGN) 2nd Examination (Take Home) Due Monday November 26, 2007 PLEASE NOTE: Individual Effort is Required. Shared effort will result in the lowest score earned by one of the people determined to have shared work being divided by the number of individuals involved and assigned to all involved. Problem 1: Wire Delay Models [20 points] a) List three wire delay models and state explicitly the factors influencing the use of each model i.e. when is it appropriate to use one model over the other? b) For the following questions refer to the diagram below: i) ii) iii) iv) v) vi) vii) The wire lengths are each 5 mm, with capacitance to ground of 3.0 aF/m and fringing capacitance of 3.0 aF/m, Req of the inverter is 120.76 Ω Assume at first the wire is in isolation i.e. only one inverter drives the wire without any neighbor. Calculate the propagation delay of this path. Please use only the provided information to compute this delay in other words use the appropriate delay model from the three you listed in part (a). Also ignore the inverter’s internal/intrinsic capacitance. Req for the second wire driven by the nMOS is 120.74 Ω. The wires are switching in the same direction. What is the propagation delay of the path of the wire driven by the inverter? Now the first and second (middle) wires switch in opposite directions. Compute the path’s propagation delay. Based on your propagation delays computed above in (ii) and (iii), please propose at least three ways you can employ to reduce the contamination delay. The middle wire is quiet (at logic 0) with the first and third wires switching in opposite directions. Would this activity have an effect on the middle wire? Please justify your answer. Now the first and third wires switch in the same direction with the middle wire quiet. What effect does this activity have on the middle wire? Justify your answer. Is the suggested model for computing the path delay adequate? Please show mathematically why it is adequate or inadequate. (Essentially you are being asked to compare this model to the other realistic one of the three in part (a). Problem 2: Accounting for the intrinsic capacitance, wire capacitance and wire resistance and loading capacitance [20 points]. a) Our 5 mm wire contributes significantly to the path’s propagation delay. Your task is to provide an expression that accounts for all the parasitics that contribute to this delay. The wire is now driving another inverter of similar size. b) Assuming the two inverter stage circuit below was intended to drive a load of say 400 with the input stage capacitance of 4, how would you improve the path delay? Your solution must affect both the drivers’ strengths as well as the wire delay. Problem 3: Power Dissipation [20 Points] Given a power supply voltage of 1.2V for a 100 nm process with low Vt and high Vt devices (nMOS and pMOS). Your task is to make important decisions pertaining to the design of a static memory sub-system that has a total of 200 million transistors. 20 million of these transistors are for logic gates (for memory control and decoding) the remainder are within the memory array. The average width for the devices of the logic gates is 12 while the average width of the devices for the memory is 4 (where lambda is half the gate length i.e. for a 100 nm process = 50 nm). The low Vt devices when in their OFF states leak 20 nA/m while the high Vt devices leak 0.02 nA/m in their OFF state. The gate leakage for thin oxide devices is 3 nA/m and 0.02 nA/m for thick oxide devices. Logic has 20 % of its transistors in the critical path. All devices have gate leakage i.e. both devices with thick oxides and those with thin oxides have gate leakages. On average during operation half the devices are OFF contributing leakage currents. a) Assign the low Vt and high Vt transistors to the appropriate modules of this design i.e. what type of devices would you use for memory and the none critical path of the logic, etc? b) Estimate the static power consumption of this sub-system. How would the static power consumption change if there were no low leakage devices? c) Assume the activity factor of logic gates is 0.1, with the memory arrays divided into banks and only the necessary bank is activated leading to a memory activity factor of 0.05. The transistors have a gate capacitance of about 2 fF/m, neglecting wire capacitance please estimate the dynamic power consumption per MHz of the sub-system. Problem 4: Non Overlapping Clocks [20 points] Two phase clocking is an ideal clocking scheme particularly in the design of sequencing elements since the clock skew is unlikely to lead to problems with race condition etc. 1 2 T12 T34 a) Clocks 1 and 2 are provided your task is to design transistor level circuits that will generate signals T12 and T34 with 1, 2 and in some instances their inverses as inputs. The signals all have the same frequency and equal pulse widths even though that might not appear to be so on the diagram. b) What could be the benefit of generating and having the additional two clocks in a design? Problem 5: Clock distribution and Skew. [20 points] The circuit below shows an attempt at global clock distribution, the clock drivers are such that they provide equal delay so that clk1 through clk8 switch at the same time. Fig. 3 Clock distribution network a) What effect(s) does clock switching have on the power rails (VDD and Gnd)? b) How do these effects affect noise margins, clock skew and overall performance of the system being clocked? c) Propose some solutions to alleviate these problems.