* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Homework 5 - University of California, Berkeley

Resistive opto-isolator wikipedia , lookup

Opto-isolator wikipedia , lookup

Crystal radio wikipedia , lookup

Rectiverter wikipedia , lookup

Surface-mount technology wikipedia , lookup

Lumped element model wikipedia , lookup

Telecommunications engineering wikipedia , lookup

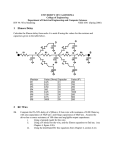

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on February15, 2002 by Josie Ammer ([email protected]) Jan M. Rabaey, Andrei Vlademirescu Homework #5 Due Friday 03/1/02 5pm, in 558 Cory EECS 141 Problem #1 A R1 R 5 R 2 Calculate the Elmore delay from node A to node B using the values for the resistors and capacitors given in the table below. C2 R3 R6 C1 C3 B R8 C6 C8 7 R 4 R C4 Resistor R1 R2 R3 R4 R5 R6 R7 R8 C5 Value (Ohms) 0.25 0.25 0.50 100 0.25 1.00 0.75 1000 C7 Capacitor C1 C2 C3 C4 C5 C6 C7 C8 Value (fF) 250 750 250 250 1000 250 500 250 Problem #2 a. Compute the 0%-50% delay of a 500um x 0.5um wire with resistance of 0.08 Ohms/sq, with area capacitance of 30aF/um2, and fringe capacitance of 40aF/um. Assume the driver has a source resistance of 100 ohms and negligible output capacitance. i. Using a lumped model for the wire. ii. Using a PI model for the wire, and the Elmore equations to find tau. (see Chapter 4, figure 4.26). iii. Using the distributed RC line equations from Chapter 4, section 4.4.4. b. Compare your results in part a. using spice (be sure to include the source resistance). For each simulation, measure the 0%-50% time for the output i. First, simulate a step input to a lumped R-C circuit. ii. Next, simulate a step input to your wire as a PI model. iii. Unfortunately, our version of spice does not support the distributed RC model as described in the book (Chapter 4, section 4.5.1). Instead, simulate a step input to your wire using a PI3 distributed RC model. Problem #3 A standard CMOS inverter drives an aluminum wire on the first metal layer. Assume Rn=4Kohms, Rp=6Kohms. Also, assume that the output capacitance of the unloaded gate is negligible compared to the wire we are driving. The wire is .5um wide, and the resistivity is 0.08 Ohms/sq. a. What is the "critical length" of the wire (see Chapter4)? b. What is the equivalent capacitance of a wire of this length? (For your capacitance calculations, use Chapter 4 Table 4.2, assume field underneath, nothing above, and nothing on either side of the wire.) Problem #4 A two-stage buffer is used to drive a metal wire of 1 cm. The first inverter is a minimum size with an input capacitance Ci=10 fF and a propagation delay tp=150 ps when loaded with an identical gate, and assume gamma =1. The width of the metal wire is 2.5 m. The sheet resistance of the metal is 0.08 /, the capacitance value is 0.03 fF/m2 and the fringing field capacitance is 0.04 fF/m. a. What is the propagation delay of the metal wire? b. Compute the optimal size of the second inverter. What is the minimum delay through the buffer (i.e. the sum of the delays through both inverters)?