* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

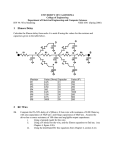

Download Design ~F = AB + AC + BC in static CMOS

Radio transmitter design wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Standing wave ratio wikipedia , lookup

Negative resistance wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power electronics wikipedia , lookup

Lumped element model wikipedia , lookup

Telecommunications engineering wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Current mirror wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on February 28, 2007 Andrei Vladimirescu Homework #6 Due 03/09/07, 5pm, in 240 Cory EECS 141 1. Wire Models a. Compute the 0%-50% delay of a 500um x 0.5um wire with resistance of 0.08 Ohms/sq, with area capacitance of 30aF/um2, and fringe capacitance of 40aF/um. Assume the driver has a source resistance of 100 ohms and negligible output capacitance. i. Using a lumped model for the wire. ii. Using a PI model for the wire, and the Elmore equations to find . (see Chapter 4, figure 4.26). iii. Using the distributed RC line equations from Chapter 4, section 4.4.4. b. Compare your results in part a. using Spice (be sure to include the source resistance). For each simulation, measure the 0%-50% time for the output i. First, simulate a step input to a lumped R-C circuit. ii. Next, simulate a step input to your wire as a PI model. Unfortunately, our version of spice does not support the distributed RC model as described in the book (Chapter 4, section 4.5.1). Instead, simulate a step input to your wire using a PI3 distributed RC model. 2. Wire Delay A standard CMOS inverter drives an aluminum wire on the first metal layer. Assume Rn=3.5Kohms, Rp=6.5Kohms. Also, assume that the output capacitance of the unloaded gate is negligible compared to the wire we are driving. The wire is .5um wide, and the resistivity is 0.1 Ohms/sq. a. What is the "critical length" of the wire (see Chapter4)? b. What is the equivalent capacitance of a wire of this length? (For your capacitance calculations, use Chapter 4 Table 4.2, assume field underneath, nothing above, and nothing on either side of the wire.) 3. Transmission Line A 10 cm long lossless transmission line on a PC board (relative dielectric constant = 9, relative permeability = 1) with characteristic impedance of 50 ohms is driven by a 2.5V pulse with a source resistance of 150 ohms. a. If the load resistance is infinite, determine the time it takes for a change at the source to appear at the destination (time of flight). Now a 200 ohms load is attached at the end of the transmission line. b. What is the voltage at the load at t = 3ns? c. Draw the lattice diagram and sketch the voltage at the load as a function of time. Determine how long does it take for the output to be within 1 percent of its final value. 4. CMOS Gate Design and Implementation a) Design F AB AC BC in static CMOS. Draw the schematics and size the transistors with respect to unit width NMOS and PMOS devices so that Worst case equivalent resistances are equal to those of a unit sized inverter (Runit). Assuming 2k’p = k’n. Which input pattern(s) would give you the worst and best equivalent pull-up or pulldown resistance. b) Draw the Logic Graphs corresponding to the circuit and Identify the Euler paths c) Using the Euler paths you found draw the stick diagram for the implementation. You don’t need to distinguish different widths in the stick diagram. But do use the appropriate colors. 5. Fan-in effects on the delay of static CMOS gates In this problem we will calculate the effective delays due to a single 6 input AND(Figure 1) vs. another 6-input AND that is composed of two 3-input NAND gates(Figure 2). Assume equivalent resistance of NMOS ReqNMOS = R and ReqPMOS = 2R, for minimum sized NMOS and PMOS devices. Also Assume Cdb = Csb = Cg = C, again for NMOS and PMOS minimum sized transistors. For any gate we are targeting to have worst-case equivalent resistance of R from output to VDD or GND A progressive sizing scheme is employed in designing both gates. For figure1 M1=M2=4x; M3=M4=6x; M5=M6=12x and the inverter is sized to have worst-case equivalent resistance of R, as well. For figure2 M1=2x, M2=3x,M3= 6x; the secondstage-NOR is sized such that worst-case equivalent resistances from output to VDD or GND is R as well. For figure1 Calculate the propagation delay from A6 to output, as A6 transitions L->H while all other inputs (A1…A5) are kept at High. For figure2 calculate the delay as A3 transitions L->H while other inputs stay High VDD M7 A1 M12 M8 A2 A6 A1 M1 A2 A6 CL M2 M6 Figure 1 AND gate with a 6-input NAND 1st stage 2nd stage A4 A5 A6 M15 M16 VDD M4 A1 M6 M5 A2 A3 A1 M1 A2 A3 CL M13 M14 M2 M3 Figure 2 AND gate with two 3-input NAND gates and on 2-input NOR gate