* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download A New Fully Balanced Differential OTA with Common

Phase-locked loop wikipedia , lookup

Negative resistance wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Integrated circuit wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Index of electronics articles wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Surge protector wikipedia , lookup

Power electronics wikipedia , lookup

Power MOSFET wikipedia , lookup

Radio transmitter design wikipedia , lookup

Schmitt trigger wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Wilson current mirror wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Regenerative circuit wikipedia , lookup

RLC circuit wikipedia , lookup

Current mirror wikipedia , lookup

Opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

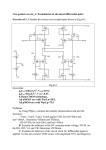

A New Fully Balanced Differential OTA with Common-Mode Feedback Detector Radu Gabriel Bozomitu, Vlad Cehan Department of Telecommunications, Faculty of Electronics and Telecommunications ”Gh. Asachi” Technical University Carol I No. 11 Av., 700506, Iaşi, Romania Phone, Fax: +40-232-213737, [email protected], [email protected] Abstract A new fully balanced differential CMOS operational transconductance amplifier (OTA) with common-mode feedback (CMFB) detection is proposed. The common-mode feedback circuit can be economically implemented. The common-mode tuning loop allows a constant d.c. level at both differential outputs for bias current, power supply and process variations. The proposed OTA power consumption is of 3.6mA from a 3.3V voltage supply and drives 0.5pF single ended capacitive loads. The proposed OTA achieves a 575 MHz gain-bandwidth product. The simulations made in 0.13 μm CMOS process confirm the theoretically obtained results. 1. INTRODUCTION The transconductor is a very important part of the design since it may limit the linearity, frequency response, and noise performance attainable from the system. Tunability may also be an important requirement in applications requiring a precise value of gm (e.g. filters), independent of process and temperature variations. The simplest and most widely used transconductor is the source-coupled differential pair. The differential pair offers a true differential input and can readily achieve both positive and negative transconductance values. With a slight increase in complexity to implement common-mode feedback, this enables the implementation of a fully-balanced architecture, thus improving the dynamic range, PSRR, and CMRR. Furthermore, the inherent symmetry of the differential amplifier tends to reduce offsets and drift. In general, a fully differential structure has an improved dynamic range over its single-ended counterpart. This is due to the proprieties of any differential structure, namely, better common-mode noise rejection, better distortion performance, and increased output voltage swing. An important problem of a fully differential structure is the need of an extra common-mode feedback (CMFB) circuit. The CMFB circuit goals are: 1) to fix the common-mode voltage at different high impedance nodes that are not stabilized by the negative differential feedback, and 2) to suppress the common-mode signal components on the whole band of differential operation. A CMFB circuit is classically performed by means of an additional loop. The output common-mode level VCM is sensed using a common-mode detector, ( + − VCM = vout + vout ) 2 . It is then compared with the reference voltage Vref, and an error-correcting signal is injected to the biasing circuitry of the OTA. The CMFB loop has to be designed carefully to avoid potential stability problems. This often increases the complexity of the design, the power consumption, and the silicon area used. The frequency response of the differential path is also degraded due to the added parasitic components involved in conventional CMFB schemes [1] – [3]. In this paper a new structure of a fully balanced differential OTA with common-mode feedback detector is presented. The advantage of the proposed structure consists in possibility of maintenance the d.c. level at both differential outputs to a prescribe value. One should notice the fact that CMFB loop allows a constant d.c. level at both differential outputs for bias current, power supply and process variations. By this tuning of the common-mode, the proposed structure can be used both in applications requiring d.c. coupling and also in those requiring a.c. coupling. 2. DIFFERENTIAL PAIR TRANSCONDUCTOR The basic source-coupled differential pair, shown in Fig. 1, can be described by the following equations: Gm 0 = μ C ox Vin1 M1 M2 Vin2 (11) 3. ELECTRICAL SCHEMATIC OF THE PROPOSED FULLY BALANCED DIFFERENTIAL OTA WITH CMFB DETECTOR The proposed circuit is formed by a fully balanced differential operational transconductance amplifier and a common-mode feedback detector stage, which will be presented in the following. Iss 3.1. Electrical schematic of the Fully Balanced Differential OTA Fig. 1. The basic source-coupled differential pair ⎧ 1 2 ⎛W ⎞ ⎪ i D1 = 2 μ Cox ⎜ L ⎟ (VGS 1 − VTH ) ⎝ ⎠1 ⎪ (1) ⎨ ⎪ i = 1 μ C ⎛ W ⎞ (V − V ) 2 ⎟ ox ⎜ GS 2 TH ⎪⎩ D 2 2 ⎝ L ⎠2 Considering that the transistor which form the input differential pair are perfectly matched, one can write: W ⎛W ⎞ ⎛W ⎞ (2) ⎜ L ⎟ =⎜ L ⎟ = L ⎝ ⎠1 ⎝ ⎠ 2 For the structure shown in Fig. 1, the following equations can be written: I SS = i D1 + i D 2 (3) Vin1 − Vin 2 = VGS 1 − VGS 2 (4) The output differential component is given by the difference between both currents described by (1): id = i D 1 − i D 2 (5) According to (1) – (4), from equation (5), after mathematical operation, results: 4 I SS 1 W id = μ Cox ΔVin − ΔVin2 (6) W 2 L μ Cox L unde ΔVin = Vin1 − Vin 2 (7) The transconductance of the stage illustrated in Fig. 1 can be calculated as: ∂id Gm = (8) ∂ΔVin V = const . DS By using equation (6) in (8), results: 4 I SS − 2ΔVin2 W μ Cox 1 W L Gm = μ C ox L 2 4 I SS − ΔVin2 W μ Cox L If we consider, ΔVin = 0 from equation (9) is obtain: W I SS L (9) (10) The electrical schematic of the fully balanced differential OTA is illustrated in Fig. 2.a). This relies on a differential pair, implemented by M1 and M2 transistors. The two currents of the differential pair are sensed to the both differential outputs by some cascoded current mirrors. So, the currents obtained at the both circuit’s differential outputs can be described by the following equations: ⎧ id 1 = i D1 − i D 2 (12) ⎨ ⎩ id 2 = i D 2 − i D1 After mathematical operation, results: ⎧ 4 I SS 1 W − ΔVin2 ΔVin ⎪ id 1 = μ Cox W 2 L ⎪ μ Cox ⎪ L (13) ⎨ 4 I SS 1 W ⎪ 2 − ΔVin ⎪ id 2 = − 2 μ Cox L ΔVin W μ Cox ⎪ L ⎩ 3.2. Electrical Schematic of the CMFB Detector The electrical schematic of CMFB detector is illustrated in Fig. 2.b). This is implemented by the stage realized by M3, M4, M5 and M6 transistors. The Vref input is connected to a fixed voltage which represents the prescribed d.c. level at both differential outputs of the proposed circuit. The two inputs (noted OUTP and OUTN) of the CMFB stage represent just the two differential outputs of the proposed circuit. If the two output common-mode voltages differ from Vref, the current of M3 and M6 transistors change, and this leads to increase or decrease of Vctr1 voltage. Then this voltage is applied to P15, P16 and P17, P18 transistors, whose currents can control output common voltages. For a correct operation of the common-mode loop, the CMFB controlled transistors (P15, P16 and P17, P18) and also those lying on XN and XP branches (P5, P6 and P9, P10) are sized so that their W/L ratio to be two fold smaller than that of the P1, P2 and P7, P8 transistors which transmit to the outputs the input differential pair currents. Thus, the following equations occur: VDD P11<1:32>P17<1:16> P9<1:16> PMOS PMOS PMOS Vctrl2 W = 6u W = 6u L = 400n L = 400n PMOS P7<1:32> PMOS W = 6u L = 400n PMOS W = 6u L = 400n W = 6u L = 700n VDD XP OUTP W = 2u L = 400n M7<1:8> NMOS M9<1:8> P2<1:32> P4<1:32> W = 6u L = 700n Vctrl1 W = 6u L = 700n W = 6u L = 700n OUTN M10<1:8> GND C2 500fF NMOS W = 6u L = 400n M17<1:8> NMOS W = 6u L = 700n M16<1:8> NMOS NMOS P16<1:16> PMOS PMOS XN NMOS W = 6u L = 700n NMOS W = 6u L = 400n M2<1:32> INN M15<1:8> NMOS M18<1:8> W = 6u L = 400n M21<1:8> P6<1:16> PMOS Vctrl2 W = 6u L = 400n W = 6u L = 700n Bias2 W = 6u L = 400n W = 6u L = 400n P15<1:16> PMOS PMOS W = 2u L = 400n Bias1 M8<1:8> NMOS NMOS GND P5<1:16> PMOS W = 6u L = 700n M1<1:32> NMOS INP W = 6u L = 700n C1 500fF PMOS W = 6u L = 700n Ibias 800uA P3<1:32> W = 6u L = 400n P12<1:32>P18<1:16> P10<1:16> P8<1:32> PMOS PMOS PMOS Vctrl1 W = 6u W = 6u L = 700n L = 700n P1<1:32> NMOS W = 6u L = 400n GND M19<1:8> W = 6u L = 700n W = 6u L = 700n M22<1:8> M20<1:8> W = 6u L = 400n W = 6u L = 400n GND NMOS NMOS a) VDD P13<1:16> PMOS Vctrl2 P19<1:16> PMOS W = 6u L = 400n P14<1:16> PMOS Vctrl1 W = 6u L = 400n P20<1:16> PMOS W = 6u L = 700n M3<1:12> OUTP NMOS GND W = 2u L = 400n M11<1:2> Bias1 W = 6u L = 700n M4<1:12> M5<1:12> NMOS NMOS Vref W = 2u L = 400n NMOS W = 2u L = 400n Vref M12<1:2> W = 6u L = 400n M13<1:2> 1.5V W = 6u L = 700n Bias2 GND NMOS M6<1:12> OUTN W = 2u L = 400n NMOS W = 6u L = 700n M14<1:2> NMOS GND W = 6u L = 400n NMOS b) Fig. 2. Electric schematic of the proposed circuit: a) Fully Balanced Differential OTA; b) CMFB circuit ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ ⎝ ⎠ P15 ⎝ ⎠ P16 ⎝ ⎠ P17 ⎝ ⎠ P18 ⎝ ⎠ CMFB ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ (14) ⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ ⎝ ⎠ P5 ⎝ ⎠ P6 ⎝ ⎠ P9 ⎝ ⎠ P10 ⎝ ⎠ OTA ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎛W ⎞ ⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ =⎜ L ⎟ ⎝ ⎠ P1 ⎝ ⎠ P2 ⎝ ⎠ P7 ⎝ ⎠ P8 ⎝ ⎠ et_diff According to the relations above, one can write: (W L )et_diff = 2 (W L )CMFB = 2 (W L )OTA (15) By using of this common-mode tuning, the d.c. level of both differential outputs can be kept constant for bias current, power supply and process variations, which represent an important improvement of the proposed circuit. 4. SIMULATIONS RESULTS For the beginning, the circuit from Fig. 2.a) is simulated in the absence of the CMFB stage, which provide the common-mode tuning. The proposed circuit uses a VDD=3.3V voltage supply and a Vbias=1.65V bias voltage. In this first case, the CMFB stage is not presented in the schematic shown in Fig. 2.a) and the P5, P6 and P9, P10 transistors have identical size with P1, P2 and P7, P8, respectively, which transmit to the outputs the input differential pair currents. So, in this case, one can write: (16) (W L )et_diff = (W L )OTA In Fig. 3 are presented the two differential voltage outputs waveforms of the fully balanced differential OTA without CMFB. It is noticed that both differential voltage outputs are axed on a d.c. level equal to 1.3 V. The main problem of this circuit is the fact that the d.c. level of both differential outputs cannot be kept at a wished value in the absence of a feedback or a common-mode tuning circuit. Another problem is given by the d.c. level’s variation at both differential outputs with bias current and voltage supply variations. This aspect is shown in Fig. 4, where the two differential outputs d.c. level variation depending on bias current variation between 20μA - 800μA, is plotted. In Fig. 5, the differential transconductance values of the fully balanced differential OTA without CMFB for different values of the bias current (between 100μA – 800μA) are shown. In Fig. 6, the small signal frequency response of the fully balanced differential OTA without CMFB for different values of the bias current, are presented. For a maximal value of the bias current (800μA) we can obtain a gain-bandwidth product of 600MHz. In the following, the fully balanced differential OTA with CMFB detector is analyzed. To illustrate the CMFB stage operation, a reference voltage, Vref = 1.5V, is chosen. So, in Fig. 7 the two differential voltage outputs waveforms of the fully balanced differential OTA with CMFB, are presented. It is noticed that the two differential voltage outputs are axed on a d.c. level equal to the prescribe reference value of 1.5 V. The common-mode tuning loop operation is shown in Fig. 8, where the two differential outputs d.c. level variation depending on bias current variation between 20μA - 800μA, is plotted. From Fig. 8 is noticed that in this case, the d.c. level of both differential outputs of the proposed circuit is kept constant at 1.5 V, imposed as reference. The advantage of this configuration is given by the possibility of using the proposed circuit in application requiring d.c. coupling and also in those requiring a.c. coupling. The main disadvantage of using the common-mode tuning loop (CMFB) is represented by the increased complexity of the circuit, which leads to diminish the frequency performances of the proposed circuit. For this reason, the circuit used as CMFB detector must be designed so that it gives low capacitance loads in the output nodes. This is achieved by choosing smaller sizes for M3 – M6 transistors of CMFB stage than those used for M1 and M2 transistors which form the input differential pair of the proposed circuit. So, we can write: (17) (W L )CMFB : (W L )et_diff = 3 : 8 In Fig. 9, the differential transconductance values of the proposed fully balanced differential OTA with CMFB for different values of the bias current (between 100μA – 800μA) are shown. In Fig. 10, the small signal frequency response of the proposed fully balanced differential OTA with CMFB for different values of the bias current, are Fig. 3. Two differential voltages outputs waveforms of the OTA without CMFB (f0 = 100 MHz) Fig. 4. DC response of the OTA without CMFB presented. Fig. 5. Gm value of the OTA without CMFB for different values of the bias current Fig. 6. Differential output frequency response of the OTA without CMFB for different values of the bias current Fig. 9. Gm value of the OTA with CMFB for different values of the bias current Fig. 10. Differential output frequency response of the OTA with CMFB for different values of the bias current 5. CONCLUDING REMARKS Fig. 7. Two differential voltages outputs waveforms of the OTA with CMFB (f0 = 100 MHz) In this paper a new fully balanced differential OTA with common-mode feedback detector has been proposed. The proposed circuit is formed of a fully balanced differential OTA, having a CMFB stage for the common-mode tuning. By using the common-mode tuning, the d.c. level on which the two differential voltage outputs of the proposed circuit are axed, can be kept at a prescribed value, and the two outputs can be both, d.c. and a.c. coupled. It is also shown that these d.c. levels are constant at the bias current and voltage supply variations. In the paper is shown that the proposed circuit’s performances are closed enough to that of the fully balanced differential OTA without CMFB. The simulations made in 0.13 μm CMOS process confirm the theoretically obtained results. REFERENCES Fig. 8. DC response of the OTA with CMFB For a maximal value of the bias current (800μA) we can obtain a gain-bandwidth product of 575MHz, smaller than for the previous case. This is due to the CMFB stage, which determines increasing the parasitic capacitance loads in the outputs nodes of the proposed circuit. [1] Ahmed Nader Mohieldin, Edgar Sánchez-Sinencio, “A Fully Balanced Pseudo-differential OTA With Common-Mode Feedforward and Inherent Common-Mode Feedback Detector”, IEEE Journal of Solid-State Circuits, VOL. 38, NO. 4, APRIL 2003, pp. 663 – 668; [2] F. Rezzi, A. Baschirotto, and R. Castello, “A 3-V 12-55-MHz BiCMOS Pseudo-differential Continuous-time Filter”, IEEE Trans. Circuits Syst. I, vol. 42, no. 11, Nov. 1995, pp. 896 – 903; [3] Z. Czarnul, T. Itakura, N. Dobaschi, T. Ueno, T. Iida, and H. Tanimoto, “Design of Fully Balanced Analog Systems Based on Ordinary and/or Modified Single-ended Opamps”, IEICE Trans. Fundam., vol. E82-A, no. 2, Feb. 1999, pp. 256 – 270.