* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download L10_Overview

Surge protector wikipedia , lookup

MIL-STD-1553 wikipedia , lookup

Cellular repeater wikipedia , lookup

Power electronics wikipedia , lookup

Oscilloscope history wikipedia , lookup

Regenerative circuit wikipedia , lookup

Crystal radio wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrated circuit wikipedia , lookup

Telecommunications engineering wikipedia , lookup

Electromigration wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Index of electronics articles wikipedia , lookup

Opto-isolator wikipedia , lookup

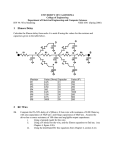

COEN6511 LECTURE 10 Interconnect RC distributed model for an interconnect was derived previously as:. rc 2 l , where RC is per unit delay 2 rc n(n 1) 2 Now for the circuit shown below What is the maximum practical length that can be used? Let us take an example Example A signal is propagated on a 6mm length metal 1 (M1) interconnect, using minimum wire width. Calculate the delay and comment on methods for reducing this delay. rc 2 l 2 Now the resistance and capacitance of CMOSIS5 are given as ( from the manual): r = 0.07 / c = 46 aF/mm2, c = 46*1 exp -18, (a = 1 exp -18), Delay of wire = If we normalize the resistance and capacitance to unit length ( assuming our unit length to be 0.6µ, r = 0.07 / unit length c = 46 * 0.36 aF / unit length 0.07 * 4.6 * 0.36 *1018 6000 2 ( ) *109 ns 2 0.6 0.057ns Is the time constant acceptable? It really depends on the design. If this results is not acceptable, then we have to solve this problem, by either widening the wire, thus decreasing the resistance, however that increases the capacitance as well. Page 1 of 10 Lecture#10 Overview A possible solution is to break down the long interconnect line into smaller segments. Let us assume, we insert a buffer in the middle of the line, rc Using the equation l 2 2 0.07 * 4.6 * 0.36 *1018 3000 2 ( ) *109 ns 2 0.6 0.014ns The overall delay of the two interconnects plus the new buffer is now: delay overall 2 * 0.014 buff if the buffer has a delay of buff 0.01ns 2 * 0.014 0.010 tot 0.038ns 0.057ns(original value) One solution is to insert buffers in the transmission line until the total delay of the line becomes much smaller than the delay of the buffer. Generally, the maximum length of the wire should be calculated according to the following criteria. buff 2 * buff rc 2 l or l ( ) 2 rc This formula has different values depending on the type of material being used, for example, the time constant for metal 1 is different from that of poly-silicon. In case of segmented and unequal interconnects, we usually break down the total length into multiple paths, each one with their own time constant. Page 2 of 10 Lecture#10 Overview Small Geometries When should the concept of transmission line theory be used? Whenever the rise time and fall time of a signal is comparable to an interconnect delay, then the line can be model as a transmission line. pd 33 r , with unit of ps/cm where r is the dielectric constant of the material. An empirical rule to obtain the critical path delay is: c 1/ 3 min( t r , t f ) pd ( ps / cm) , where pd is that of for the line and c is the critical path delay. What is the minimum size of a silicon chip? Various factors affect the physical size of an integrated chip mainly: Power dissipation Packaging Number of pins Technology The interconnect used Page 3 of 10 Lecture#10 Overview The maximum chip size is obtained by Achip 0.16 RoCo ln( RintCint CINT Area packaging Cl 2 ) Co Rint, Cint and CINT are resistance and capacitance / per unit length of the interconnect and the lower and upper case subscript refers to the chip and the package. A is the area of the die, Co and Ro are the input capacitance and output resistance of a minimum size inverter and CL is a typical off-chip load. Page 4 of 10 Lecture#10 Overview Inductances There exist two types of inductances: Die wires and on-chip inductances. 4h ln( ) 2 d Where h is the height of the wire above the substrate, d is the diameter of the wire and is the magnetic permeability of the material. For die wires, L For on-chip, L 8h w ln( ) 2 w 4h Example Determine values for x, y due to inductive and resistive losses when the output driver sources 10mA in 1.5ns in the following circuit. Also, assume width of interconnect, W to be 5um and h to be 12,000 Ao From the above circuit, there will be both ground bounce and VDD bounce. Page 5 of 10 Lecture#10 Overview 1) Calculate the inductance 8h w ln( ) in nH/mm, 2 w 4h 8 1.257 *10 9.6 5 L= ln( ) nH/mm = 13.9mH/mm 6.28 5 4.8 Using L 2) Calculate the total amount of wire inductance For a wire strip of 1cm, Ltot=13.9*10=139nH 3) Calculate the voltage drop across the wire i Voltage drop across wire = 139 *109 * t 10 *103 = 139 *109 * 1.5 *109 139 *10 mv = 1.5 = 0.926V = 926 mV Assuming that the power supply for the output buffer is 3.3V, we hence have the following circuit. Example of ground bounce Consider the following circuit Page 6 of 10 Lecture#10 Overview While the inverter is suppose to be off, it will turn on momentarily because of the spike. The same spike will propagate through the adjacent circuit. It is also particularly damaging to dynamic circuit. Page 7 of 10 Lecture#10 Overview How to avoid this problem? The 1cm length is not practical in today’s technology. We now also use tens or hundreds of VDD and GND pads. As a result, the distance of 1 cm is very impractical. More realistic distances are 1mm and less. How about when we drive several buffers at the same time? The current demand increases several folds and ground bounce and VDD bounce is also increased. Always calculate GND bounce and VDD bounce when distributing power lines! Example What will be the power line width if you drive a 10pF load at 1MHz P = fVDD2CL = 1*109 * (3.5)2 *10 *1012 = 0.1Watt P=I*V I = 0.1/3.3 I = 30mA If we use a conductor with current density J = 1mA / um, we will need a width of 30um At this point, we need to go back and re-do the calculation for the inductance with the new length parameter. Page 8 of 10 Lecture#10 Overview Charge Sharing Consider a bus circuit with the following structure Qb=CbVb, where Qb is charge on the bus, Cb is the bus capacitance and Vb is the voltage at the bus. Similarly, for the charge on the signal line, we have Qs=CsVs, where Qs is charge on the signal line, Cs is the signal line capacitance and Vs is the voltage present on the signal line. When the NMOS transistor goes on, charge sharing occurs between the bus and the signal line. The net charge of the two lines combine becomes QR=CRVR, VR = QR /CR VR CbVb CsVs Cs Cb Consider one scenario Let Vb = 3.3Volt representing logic ‘1’ and Vs = 0V representing logic ‘0’ CbVb CsVs Cs Cb 3.3Cb VR C s Cb 3.3 VR 1.7V 2 This is under the assumption that Cs and Cb are equal, and the resulting VR is unacceptable! According to charge sharing, VR Page 9 of 10 Lecture#10 Overview Hence we must have the bus capacitance Cb >> Cs Example Calculate the drop in voltage for 64 read lines each consisting of 0.1pF capacitances. Assume bus capacitance to be 10pF. VDD * Cb C s Cb 3.3 *10 pF VR 10 (64 * 0.1 pF ) 33 VR 16.4 VR VR 2V END OF LECTURE #10 Page 10 of 10 Lecture#10 Overview