* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download transparencies

Survey

Document related concepts

Transcript

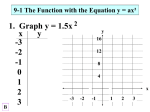

Deep sub-micron chip development Hirokazu Ikeda Institute of space and astronautical science Japan aerospace exploration agency Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 1 MV, ISAS HII-A, JAXA HII-A MV Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 2 Contents for Talk 1. 2. 3. 4. 5. 6. Introduction Multi-chip project available in Japan Open-IP 4096-channel pixel array TEG for FD-SOI CMOS Summary Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 3 1. Introduction Deep sub-micron CMOS: could be defined as CMOS whose feature size is smaller than 0.5 um and which no more sustains a power supply voltage of 5.0 V. Benefit of sub-micron CMOS are: 1) 2) 3) 4) 5) 6) Increase in number of transistors on a chip Improvement of functionality of LSI’s Increase in switching speed of MOSFET’s and circuits and, hence, improvement of operation speed of LSI’s Decrease in cost of LSI’s per performance Steep increase in radiation hardness (total doze) (enclosed structure assists to improve radiation hardness.) Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 4 Trend for TMC TMC-X 0.18 um CMOS 30 ps/bit TMC1004, 0.8 um CMOS, NTT Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 5 2. Multi-chip project available in Japan 1.2 um (ON SEMI.) 0.35 um (ROHM) VLSI Design & Education Center Academic institutes VDEC (operated by University of Tokyo) + direct submission to MOSIS + private multi-chip project 0.18 um (Hitachi) 0.15 um SOI (OKI) 0.09 um (ASPLA) MOSIS 0.25 um (TSMC) 0.18 um (TSMC) 0.5 um SiGe (IBM) Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 6 VDEC provides 1) LSI chip fabrication…… multi-chip project 2) Test and measurement support……logic tester, EB prober, FIB facility, and etc. 3) CAD software tool support……Cadence, Mentor, Synopsys, Silvaco, and etc. 4) Lecture course for LSI design Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 7 3. Open-IP KEK, ISAS Available for research use. Expanded by users’ effort. Even with these availability of design tools, there exists a big hurdle for beginners to design an integrated circuit from scratch. In order to lower the hurdle, a circuit library (IP) is extracted from existing designs, and constructed to show known circuit topologies together with more or less realistic W/L values. FB elements Amplifier elements Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 8 Employing OPEN-IP Tohoku, ISAS Tohoku university is developing a pair monitor system for ILC. The pair monitor employs a 3-D detector as a sensor. The readout chip is configured as a pixel chip. Each pixel circuit includes a preamplifier, shaping amplifier and comparator. The shaping amplifier has a peaking time of 100 ns and a decay time of 200 ns to be compatible with the micro-bunch structure with noise level better than 1000 e’s. The output of the comparator is fed into a Gray-coded 8-bit counter, whose counts are latched 16 times during the beam burst and, then, read out during intermittence of the beam burst. A prototype chip is designed in a 0.25-um rule to be submitted to TSMC. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 9 Employing OPEN-IP TMU, KEK etc. Tokyo metropolitan university is developing an aerogel Cherenkov detector system for Super B-factory experiment. The two-dimensionally segmented hybrid avalanche photo detector acquires a ring image emitted from the aerogel radiator when charged particles pass through. An analog chain is designed to achieve a noise level of 1500 e for a detector capacitance 80 pF of the avalanche diode. The peaking time of the analog signal is adjustable in a range of 0.5 us to 2 us. The output of the analog chain is fed in to a comparator, and, then, to a shift register chain to compensate for a trigger latency. The readout is only in binary. A prototype chip is designed in a 0.35-um rule to be submitted to ROHM. 0.5<p<4.0 GeV/c Silica aerogel (1~2cm) Injection gain: 1000 Avalanche gain: 10 Total: 10000 π or K Pixelized photo detector Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 10 Employing OPEN-IP Nagoya, KEK etc. Nagoya university is developing a TOF system for a TOP (Time of propagation) detector. The TOP detector is a sort of a Cherenkov detector to measure time differences and geometrical positions of photons at the end of a quartz bar to reconstruct a Cherenkov image in a space-time coordinate. The geometrical coordinate is measured by a position sensitive photo-multiplier or a micro-channel plate, whose outputs are fed into a TAC chip. The TAC chip includes a leading-edge and/or a constant-fraction comparator channels to be fed into TAC circuits. The TAC circuit is configured as a dual system to be operated with 10-MHz bi-phase gates with an overlap of 25 ns. The time resolution envisaged is 20-30 ps. The TAC chip is designed in a 0.35-um rule to be submitted to ROHM. Preliminary 10 ns Nov 7-11, 2005 20 ns 30 ns Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 11 Employing OPEN-IP Osaka, ISAS Osaka university is developing a CCD readout system for the X-ray astronomy. A CCD detector shows a superior nature in noise, but has a drawback in terms of A readout speed. In order to improve the resolving time, they plan to employ a parallel readout CCD together with a multi-channel readout VLSI. A test chip is designed to reproduce an existing performance with a discrete circuit. The noise level envisaged is an order of less than 10 electrons. The test chip includes two channels of a complete integrator, hold circuit, and 12-bit Graycoded Wilkinson A-to-D converter. A double-correlated subtraction is carried out in off-line. The test chip is design in a 0.25 um rule to be submitted to TSMC. Preliminary Preliminary CCD Buffer V-I/Integration/HOLD 12-b*2 output ADC Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 12 3. 4096-channel pixel array ISAS Institute of space and astronautical science is developing a two-dimensional analog VLSI for readout of pixel sensors based on silicon (Si) or cadmium telluride (CdTe) for a future use of spectroscopic imaging observations in X-ray and gamma-ray region. The chip consists of four 8 mm-by -8 mm sub-chips .The entire chip can be operated either sequentially or independently for each sub-chip, depending on the readout speed requirement.. In the upper left corner of the pixel layout there is an octagonal bonding pad with a diameter of 50 um. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 13 4096-channel pixel array: signal processing The amplifier array consists of a charge sensitive preamplifier, shaping amplifier (FAST and SLOW), peak-hold circuit, and analog multiplexor circuit together with a test-pulse circuit, analog-monitor circuit and digital-control circuit. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 14 In order to maintain low-noise characteristics 1) One is the insertion of capacitors between the gate and drain nodes of a current mirror to slow down the frequency band-width of the bias voltage generation circuit. 2) Another is the employment of an RC filter for the gate of the current source of the CSA circuit. The RC filter consists of an offtransistor for R, and a MOS capacitor for C. 3) The third measure is related to a digital-to-analog interference. We employed a deep N-well process to electrically isolate the analog circuit from the nearby digital circuits. Eventually the electronic noise is suppressed down to 100 electrons (rms) or less for a CdTe pixel X-ray detector. In order to cope with low power rail voltage 1) Base lines of amplifiers are raised or lowered by 400 mV, which assumes that the preamplifier is only dedicated to a positive charge. 2) In a similar context, medium VT transistors are employed almost everywhere except for in logic gates, switches and constant current sources. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 15 5. SOI TEG Fabrication KEK, ISAS etc. PROS 1) 2) 3) 4) 5) 6) Latchup immunity Higher packing density Higher speed performance Lower power consumption Lower leakage current Reduced short-channel effects 7) Wide voltage /temperature operation range 9) Lower processing cost Nov 7-11, 2005 CONS 1) 2) 3) 4) Floationg body phenomena Parasitic effects Degraded heat dissipation Availability and cost of the substrate 5) Processing difficulties on the thin film substrates Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 16 Entering into late 1990's, the trend curve of a bulk CMOS process tends to go behind the Moore's law, and, hence, the manufactures are eager to find a way to recover development speed. SOI CMOS is then revisited to reveal its performance over an existing bulk CMOS; the SOI CMOS eventually shows up as a successor of the CMOS process inheriting well-matured fabrication technologies for a bulk CMOS. SOI of OKI Depleted region The fabrication process for our TEG design is a 0.15 um FD-SOI CMOS process from Oki electric industry Co., Ltd. In comparison with a PD (partially depleted) SOI, the FD (fully depleted) SOI employs a thinner silicon layer, and , then, the silicon layer underneath the gate electrode is completely depleted. The kink effect, which is revealed for the PD SOI, is moderated for the FD SOI. An improvement for the threshold slope parameter assists for us to employ a low VT transistor for an analog circuit design. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA FD(fully depleted)-SOI Thickness: less than 50 nm 17 Feedback Amplifier CHAIN1 Small current Large current 16 fC I fC Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 18 CHAIN2 Nov 7-11, 2005 CHAIN3 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 19 CHAIN4 Nov 7-11, 2005 The TEG circuit includes a buffer amplifier for a monitoring purpose, AC-coupling circuit, differential amplifier(slow/fast/medium) and comparator. Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 20 LAYOUT of the TEG design 2.4 mm Bias circuit CHAIN1 CHAIN2 CHAIN3 CHAIN4 2.4 mm Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 21 6. Summary 1) Deep sub-micron CMOS processes have been widely employed for high energy physics, astrophysics, and other use. 2)Japanese activities for the deep sub-micron CMOS integrated circuits are discussed, one of which is a 4096-channel pixel array that is designed and fabricated for future use in the area of astrophysics. The noise level better than 100 e's is envisaged with incorporating experiences/ideas obtained so far. 3) In order to go beyond existing technologies for an FE circuit design, we initiate a design work with an FD SOI process from Oki electric industry Co., Ltd. 4) We have submitted a TEG design to identify if we can still employ design practices for a deep sub-micron CMOS, or need to incorporate technologies exploited/devised in other research fields. Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 22 高速時間計測回路の実現へ向けて (ROHM 0.35-um CMOS) Nov 7-11, 2005 TAC Duplex Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA Constant-fraction discriminator 23 Introduction TOP (Time-of-Propagation) Counter ・New type of ring-imaging Chrenkov counter ・Possible next-generation particle-identification device at the KEKB-factory Belle experiment ・Measure time difference and geometrical positions of photons at the end of a quarts bar to reconstruct a Cherenkov ring image in a space-time coordinate ・Geometrical coordinate is measured by a micro-channel plate (MCP) Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 24 IC Design • TAC(Time-to-Amplitude Converter) ・Dual system to be operated with 10MHz bi-phase gates with an overlap of 25ns • Time-walk correction ・Leading Edge(LE) comparator IN AMP AMP AMP AMP AMP AMP LVR OUT TH ・Amplitude and Risetime Compensated (ARC) comparator IN AMP AMP AMP AMP AMP AMP LVR OUT AMP • Designed in a 0.35 μm rule submitted to ROHM by a multi-chip project provided by VDEC (VLSI design and education center) Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 25 High-Speed Timing Circuit CLOCK信号 • SYNC signal check by changing CLOCK frequency and duty ratio ・Operation is possible at 50 MHz ・At 40MHz : duty ratio 56-60% SYNC信号 Preliminary Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 26 Linearity and Time Resolution • Correlation between TAC output and delay ・Measure TAC output by 2 channel to cancel out same jitter ・Clean linearity is observed Time resolution as a function of delay ・30-50 ps is achieved by the current chip Preliminary Nov 7-11, 2005 Preliminary Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 27 マルチポートCCD読出し回路の開発 完全積分回路+ホールド回路+Willkinson 型A/D (Gray code) 12 bit , 167 MHz 完全積分 回路 Binary Gray Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 28 M01チップ COBにパッケージング M01チップの仕様 CCDの信号処理を目的として開発 -チップサイズ2.5 mm × 8 mm -CCDからの入力信号を積分する積分回路 -12ビットのAD変換回路(ウェルキンソン方式) -2ch分の処理回路を実装 M01チップレイアウト図 評価基板との組み合わせ M01チップの回路ブロック(1ch分) チップ内 CCD 2重相関 ADC amp評価基板との組み合わせ サンプリング Nov 7-11, 2005 出力 12ビット Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 29 動作確認 取得イメージ 入力電圧 ランプ信号用 ゲート信号 積分回路用 ゲート信号 得られたスペクトル 積分回路信号 counts ランプ信号 Preliminary WIDTH信号 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 30 channel Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 31 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 32 HIGH GAIN Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 33 LOW GAIN Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 34 0 1 Nov 7-11, 2005 2 3 4 5 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 35 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 36 CHAIN1 Output buffer 160 mV 3 us Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 37 CHAIN2 AC-coupling comparator 200 mV 3 us Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 38 CHAIN3 Differntal amplifier(slow) Threshold circuit 閾値設定回路 230 mV Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 39 1 us CHAIN4 Differntial amplifier(meduim) Differntil amplifier(fast) 62 mV 1 us Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 40 More about CHAIN4 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 41 差動増幅回路 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 42 コンパレータ回路 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 43 E/43 Nov 7-11, 2005 Vertex 2005 @Nikko, H.Ikeda ISAS, JAXA 44