* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Second-order intermodulation mechanisms in CMOS downconverters

Analog television wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Oscilloscope history wikipedia , lookup

Integrating ADC wikipedia , lookup

Phase-locked loop wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Index of electronics articles wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Surge protector wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage regulator wikipedia , lookup

Current source wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Schmitt trigger wikipedia , lookup

Wilson current mirror wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Power electronics wikipedia , lookup

Operational amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Radio transmitter design wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

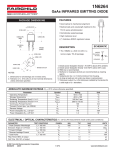

394 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 Second-Order Intermodulation Mechanisms in CMOS Downconverters Danilo Manstretta, Member, IEEE, Massimo Brandolini, Student Member, IEEE, and Francesco Svelto, Member, IEEE Abstract—An in-depth analysis of the mechanisms responsible for second-order intermodulation distortion in CMOS active downconverters is proposed in this paper. The achievable second-order input intercept point (IIP2) has a fundamental limit due to nonlinearity and mismatches in the switching stage and improves with technology scaling. Second-order intermodulation products generated by the input transconductor or due to self-mixing usually contribute to determine the IIP2 even though they can, at least in principle, be eliminated. The parasitic capacitance loading the switching-stage common source plays a key role in the intermodulation mechanisms. Moreover, the paper shows that, besides direct conversion and low intermediate frequency (IF), even superheterodyne receivers can suffer from second-order intermodulation if the IF is not carefully chosen. The test vehicle to validate the proposed analysis is a highly linear 0.18- m direct-conversion CMOS mixer, embedded in a fully integrated receiver, realized for Universal Mobile Telecommunications System applications. Index Terms—Active mixers, CMOS analog integrated circuits, dc offset, direct conversion, IIP2, low IF, mismatch, radio receivers, second-order distortion, self-mixing, UMTS. I. INTRODUCTION D IRECT conversion and low-intermediate-frequency (IF) architectures have gained increasing attention for the realization of fully integrated wireless receivers. The main reason is that they lead to potentially low-cost solutions. Depending on the application and on the specific standard, either of the two can be better suited. Direct conversion suffers from drawnoise [1], [2], while low-IF backs such as dc offset and does not. In fact, a low-IF solution downconverts the signal at a near-zero-IF frequency, in such a way that the offset can be noise has less impact on receiver seneasily removed and sitivity. On the other hand, in a direct-conversion solution, the image-rejection requirements are not demanding because the image is the signal itself. Conversely, to keep the image-rejection requirement within affordable levels, the intermediate frequency of a low-IF architecture is usually chosen in such a way that the image channel is the adjacent channel, in which the maximum allowed signal power is kept much lower than in the other channels. As a consequence, second-order intermodulation products, whose bandwidth is twice the bandwidth of the interferer, can impair the sensitivity of a low-IF solution. When Manuscript received July 25, 2002; revised October 25, 2002. This work was supported by the Italian National Program Pope. D. Manstretta is with Agere Systems, Berkeley Heights, NJ 07922 USA (e-mail: [email protected]). M. Brandolini and F. Svelto are with the Department of Electronics, University of Pavia, 27100 Pavia, Italy. Digital Object Identifier 10.1109/JSSC.2002.808310 second-order intermodulation constitutes a major problem, such as in frequency-division-duplexing systems, neither of the two architectures is intrinsically advantageous. In such cases, the realization of a highly integrated low-cost solution might even be prevented. Even more, a superheterodyne architecture can suffer from second-order intermodulation, if the IF frequency is not carefully chosen. In fact, as it will be shown, a modulated blocker at a frequency halfway between received-signal and local-oscillator (LO) frequencies would translate at IF, becoming indistinguishable from the signal. This paper addresses the problem of second-order intermodulation distortion in highly integrated CMOS receivers. Usually, the downconverter determines the achievable second-order input intercept point (IIP2) of the receiver. The focus is, then, on the physical mechanisms of second-order intermodulation in CMOS active mixers. In fact, only some of the mechanisms are well known and no quantitative analysis exists. Experimental results from a 0.18- m CMOS mixer, embedded in a fully integrated receiver for the Universal Mobile Telecommunications System (UMTS), are discussed. The paper is organized as follows. Section II is a review of second-order intermodulation distortion mechanisms, Section III is focused on self-mixing, and Sections IV and V discuss the intrinsic phenomena, i.e., active devices nonlinearity and mismatches. Section VI presents the design and experimental results of the highly linear UMTS downconverter, and Section VII presents the conclusions. II. MECHANISMS OF SECOND-ORDER INTERMODULATION DISTORTION One mechanism responsible for second-order intermodulation distortion is known as self-mixing [3]. It is due to parasitic coupling of the radio-frequency (RF) signal into the LO port and to a non-hard-switching – characteristic of the commutating stage. As a result, the mixer behaves as a multiplier and a signal proportional to the square of the input signal is produced at mixer output, resulting in base-band content. A second mechanism is due to second-order nonlinearity in the active devices of the transconductor [3]–[5]. The low-frequency intermodulation current at the output of the transconductor leaks to the output of the mixer without frequency conversion due to a duty-cycle distortion of the LO. As described in [5], this effect is to first-order cancelled using a double-balanced topology. However, a more important source of leakage exists that is not cancelled in double-balanced mixers. This is due to mismatches between the current switching stage devices. The combined effect of nonlinearity in the transconductor and mismatches in the current switching stage will be discussed in Section IV. 0018-9200/03$17.00 © 2003 IEEE MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS Fig. 1. Single balanced mixer used to model self-mixing. 395 (a) Finally, second-order intermodulation products are generated by nonlinearity in the switching stage. In this case, intermodulation products generation and leakage are processes which are intimately related, because leakage at mixer output is due to mismatches in the same devices. At low frequencies, the main nonlinear effect of the switching pair is a nonlinear partition of the current between the two active devices during the switching transients [6]. Nonetheless, the achievable IIP2 is still very high. On the other hand, at high frequencies, due to the presence of a parasitic capacitance at the common source, the linearity drops dramatically. This mechanism determines the ultimate limit to the intrinsic mixer IIP2 and will be described in Section V. (b) III. SELF-MIXING Let us consider the single balanced mixer, shown in Fig. 1. In the ideal case of hard-switching behavior, the – characteristic of the pair is shown in Fig. 2(a) and, assuming a square-wave voltage applied at the switching pair, the differential output curfor one half of the period and rent is equal to for the other half. In this case, even if the input voltage is coupled to the switching-stage LO input, the drain current of the input transistor MRF is steered by either device of the pair for exactly 50% of the period and no second-order product arises at mixer output. In actuality, the – characteristic is not stepwise and the applied LO signal is not a square wave. To gain an intuitive insight into the self-mixing mechanism, we will assume a soft-switching – characteristic [shown in Fig. 2(b)] and a sinusoidal LO signal. The mixer differential output current is given by (1) where (2) , depends on the input device current only. For , depends on the product of the input deFor vice current times the actual voltage signal at the switching-pair input. As a result, when both switching-pair devices are simultaneously on, the output current contains a term proportional to the input signal square. Fig. 2. I –V characteristic of the switching pair: (a) hard-switching and (b) soft-switching models. The second-order intermodulation product in the differential can be expressed as output current (3) If we assume a large amplitude sinusoidal LO, i.e., with , the switching time in, i.e., the interval during which , is terval . Hence, is obtained given by times a square-wave as the product of toggling between 1 and 0 with a duty cycle equal function . , , and are to plotted in Fig. 3. Let us consider the case where a strong out-of-band modulated blocker is received together with the desired signal. To gain insight in the analysis, the modulated blocker is represented by a double sideband suppressed carrier (DSB-SC) signal, i.e., . , Recognizing that , can be evaluated as for (4) 396 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 Fig. 5. IIP2 due to self-mixing versus LO power, with 2 mA biasing current and device width as a parameter. Theoretical (solid line) and simulated (dots) results. Fig. 3. Time-domain waveforms in a soft-switching single balanced mixer: = I I , and self-mixing applied sinusoidal LO V , output current I function sw(t). 0 that all the mechanisms described in this paper also affect superheterodyne architectures. Recalling the definition of IIP2 for DSB-SC signals, i.e., the input power for which the second-order intermodulation products and the linear terms are equal and the mixer transconduc, the following extance conversion gain is given by pression results: IIP2 (dBm) Fig. 4. Effect of self-mixing in a superheterodyne architecture, assuming a modulated blocker (represented by a DSB-SC signal) halfway between RF and LO frequencies. where spectral components at higher frequencies, not of interest in this analysis, have been neglected. Equation (4) tells that, as far as direct or low-IF conversions are concerned, the second term is responsible for intermodulation, while the first one is a dc offset, and the other spectral components can be easily filtered out. Moreover, the last three terms tell us that even a superheterodyne architecture suffers from second-order intermodulation. In fact, if a strong blocker is at a frequency halfway between the received-signal and LO frequencies, both the received-signal and second-order intermodulation products are at IF at mixer output. This undesirable situation is illustrated in Fig. 4, where the output spectrum shows the received signal downconverted at IF, together with all the low-frequency second-order intermodulation products. In the following, we concentrate on direct-conversion and low-IF architectures, where the problem of second-order intermodulation cannot be circumvented. However, it can be shown (dBm). (5) The IIP2 due to self-mixing depends only on LO amplitude and coupling, while it is, at least to first-order, independent of any design parameter. To maximize the IIP2, the RF-to-LO coupling has to be minimized, as expected, and the LO amplitude has to be maximized. Equation (5) has been verified through simulation of the single balanced mixer of Fig. 1. A DSB-SC signal is injected into the RF input port, while a 40-dB attenuated differential replica, representing RF-to-LO coupling, is injected into the LO port. Fig. 5 reports IIP2 versus LO power, for mA. Fig. 6 reports IIP2 versus LO various widths and m. In both power, for various biasing currents and W cases, a very good agreement between simulated and theoretical values is evident for LO powers higher than about 2 dBm. For lower LO powers, the mixer behaves more like a linear multiand the simulations plier. The conversion gain is lower than start to deviate from the calculated values. IV. TRANSCONDUCTOR NONLINEARITY SWITCHING-PAIR MISMATCHES AND Even if the RF and LO ports were perfectly de-coupled, a mixer would present second-order intermodulation distortion. Besides the desired RF signal, low-frequency second-order intermodulation products appear in the transconductor output current spectrum. After the current-switching stage, the signal is downconverted. The low-frequency intermodulation products are upconverted around the LO frequency. However, mismatches in the current switches cause part of the low-frequency current leaking at mixer output still around the baseband. The combination of second-order nonlinearity in the MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS 397 where and are the differential and common-mode second-order intermodulation currents at transconductor output, respectively, and is the rms value of the low-frequency leakage gain. and produce second-order intermoduBoth is lation in the differential output current. Moreover, converted into a differential voltage signal by mismatches in the mixer load. Therefore, the rms differential output voltage is given by (8) Fig. 6. IIP2 due to self-mixing versus LO power, with 300 m device width and pair biasing current as a parameter. Theoretical (solid line) and simulated (dots) results. where is the mixer-load differential resistance and resistance standard deviation. To calculate , , and need to be determined. is the in (8), A. Transconductor Nonlinearity Let us consider the Volterra series expansion of and , common-mode and differential currents ( respectively) versus differential input voltage of the transconductor (9) From (9), low-frequency second-order common-mode and differential output currents are given by and , respectively. If the two devices is zero. On the other are perfectly matched, hand, taking into account mismatches in the two devices, due or C variations, to threshold voltage is a random process and its standard deviation is given by Fig. 7. Double balanced mixer schematic. transconductor and mismatches in the current switches gives rise to second-order intermodulation products at mixer output. This mechanism will be discussed referring to the double balanced mixer, reported in Fig. 7. The inherent second-order nonlinear terms in the MOS – characteristic give rise to secondorder intermodulation components in the current of each branch ) at transconductor output. Assuming low frequency ( and for the switching pairs M3–M4 and M5–M6, leakage respectively, the following intermodulation in the mixer output results: current (6) Considering that the two switching pairs have the same nominal design values but mismatches and, as a consequence, are random processes, statistically independent, the root-mean) of is given by square (rms) value ( (7) (10) and are the where and , second-order transconductance sensitivities to is the standard deviation of and is the respectively. standard deviation of . The derivation of the second-order nonlinear transconductances for three different implementations of the input stage (fully differential, pseudodifferential, and LC degenerated is given pairs) is reported in Appendix A. The admittance (taking into account the finite output by , impedance of the current source), , and respectively. A summary of the results is reported in Table I, where is the second-order transconductance of the single de. The following interesting conclusions vice and can be drawn. 1) Given the typical matching parameters of a deep-submicron technology, threshold voltage mismatches determine . 398 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 G , @G TABLE I =dV , AND @G =d FOR FULLY DIFFERENTIAL, PSEUDODIFFERENTIAL, AND LC-DEGENERATED INPUT TRANSCONDUCTORS Fig. 9. Second-order nonlinearity in pseudodifferential and LC degenerated transconductors. Theoretical (solid line) and simulated (dots) G =G versus biasing current, for various device widths. the common-mode second-order transconductance , as a function of the biasing current and for different device widths, for a pseudodifferential transconductor. Both simulated results and theoretical analysis results are reported together, showing a very good agreement. The linearity improves with increasing overdrive voltages, but it is significantly smaller than in the fully differential topology case (by about 30 dB). As a result, a fully differential topology is best suited to achieve higher second-order linearity, ultimately limited by mismatches in the threshold voltage of the devices. Fig. 8. Second-order nonlinearity in a fully differential transconductor. versus biasing current, Theoretical (solid line) and simulated (dots) G =G for various device widths. 2) In a fully differential solution, the second-order differential transconductance is typically higher than the mV common-mode one. In fact, assuming value, . On the other and 1-mV hand, with a typical 4-mA biasing current and 5-k current-source output resistance, . 3) In pseudodifferential and LC-degenerated topologies, the common-mode second-order transconductance is much is the larger than the differential one. Moreover, same for the two topologies. 4) The total second-order transconductance of a pseudodifferential topology is larger than that of a fully differential one. The results of the analysis have been verified through simulations. The MOS model proposed in [7] has been used for calculations. Fig. 8 plots the linear transconductance over as differential second-order transconductance ratio a function of the biasing current and for different device widths, for a fully differential transconductor. The two sets of curves refer to mismatches in the beta coefficient and in the threshold voltage at 3 . In both cases, the agreement between theory and simulation is very good. The results in Fig. 8 confirm that threshold voltage mismatch actually determines second-order differential nonlinearity in a fully differential transconductor. Linearity improves with increasing biasing currents and decreasing device widths, i.e., for larger device overdrive voltages. Fig. 9 plots the ratio between the linear transconductance and B. Switching-Pair Low-Frequency Leakage Gain In a mixer with perfectly matched switching-pair devices, no second-order intermodulation product is transferred at the is upconverted while remains output because a common-mode signal. Threshold voltage and variations determine a mismatch in the two devices, giving rise to a low-frequency leakage gain. The circuit shown in Fig. 10(a), showing one single switching pair of the double balanced mixer, is used to quantify , the leakage gain rms value. The device mismatch is taken into account by means of an equivalent offset voltage , in series with the switching-stage LO input. source Two distinct mechanisms have been identified. The first is due to duty-cycle distortion in the output current waveform, and the second is induced by the parasitic capacitance loading the switching pair. The former will be referred to as direct (with the direct leakage gain), the latter as indirect (with the indirect leakage gain), by analogy with the mechanisms of noise in a mixer [8]. Neglecting the parasitic capacitance in the single balanced mixer of Fig. 10(a), the output current, normalized to the input one, with an applied sinusoidal LO signal, is shown in Fig. 10(b). The offset voltage is responsible for duty-cycle distortion and the output current has a nonzero average value. The output current waveform can be looked at as the input current modulated by a square-wave toggling between 1 with 50% duty cycle plus a train of pulses with height equal to 2, . is the average value of the width , and period train of pulses (11) MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS Fig. 11. LO. (a) 399 Equivalent model of the mixer in Fig. 10(a), assuming a square-wave where is the time constant when the biasing current is . to the time constant is a time-varying The sensitivity of function, while the sensitivity of the time constant to the biasing current is assumed to be constant. To gain insight in this intermodulation mechanism, the analysis is carried on in the frequency domain. The source voltage is found by inspection of the circuit. Its derivative with respect to is given by (14) (b) Fig. 10. (a) Single balanced mixer with offset voltage modeled in series with the gate. (b) Waveforms versus time: applied LO (V ), actual output current decomposed in output current without offset plus a train of pulses due to offset. The offset voltage is a random variable, and its standard deviais given by tion From (13) and (14), the current signal produces two sidein the source voltage spectrum. Corbands around respondingly, two sidebands are generated in the capacitor current spectrum and finally downconverted at a low frequency . This means that a low-frequency second-order intermodulation product at transconductor output is transmitted at mixer output at the same frequency, even if the applied LO is a square-wave signal. The resulting mixer second-order intermodulation lowis given by frequency output current at (12) and are the variance of and , respectively. where Using a large LO amplitude reduces the direct leakage gain and as a consequence second-order intermodulation products at mixer output. Ultimately, a square-wave input LO with in. Nonetheless, finite slope at zero crossing makes second-order products at mixer output are still present due to another low-frequency gain mechanism. When a square-wave LO signal is applied at the switching stage, the two devices are alternately on during each half period. The effect of the offset voltage can be analyzed exactly in the same way as the effect of the equivalent noise of the switching-pair devices [8]. This means that the pair can be looked at as a single source follower, with an applied gate-voltage signal toggling between 0 and (Fig. 11). The tail capacitor charges and discharges exponen, between 0 and . tially, with a time constant Let us consider the effect of the low-frequency intermodulation coming from the transconductor, represented by a small current . Because the current modulates the signal device biasing current, the charging-discharging time constant will also be modulated. The source voltage can be expressed as (13) (15) has been introduced. where the relation , As expected, assuming no parasitic capacitance, i.e., . Actually, in a direct-conversion mixer, noise considerations call for large-area devices, biased at low currents, leading to a relatively long time constant . Even assuming a square-wave LO (i.e., no direct leakage), second-order intermodulation is produced and the indirect mechanism determines the achievable IIP2. Before deriving quantitative conclusions, we still have to complete the analysis, and consider the case of an applied sine-wave LO. The theory developed so far is still valid, though we need to consider that the source voltage varies in response to an applied large sinusoid. In order to simplify the nonlinear analysis, we furthermore assume the following. 1) Each device of the switching pair is on for half of the period, i.e., when the corresponding voltage is positive. 2) The switching time is negligible with respect to the LO period. 3) The operating point of the active transistors is constant during each LO semiperiod. 400 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 Assuming, as in the former case, a low-frequency tone , the output low-frequency second-order intermoduis found to be lation current (19) Fig. 12. Equivalent model of the mixer in Fig. 10(a), taking into account the effect of an applied sinusoidal LO. This is reasonable, at least for . However, we can expect some deviation from this very simple model. In fact, when the LO peak amplitude is small, the switching time is not negligible with respect to the LO period. On the other hand, when the LO peak amplitude is large, a high common-mode current is injected into the common-source parasitic capacitance at twice the LO frequency. This is likely to substantially modify the operating point of the active transistor during the LO semiperiod. Nonetheless, this simple model is able to capture all the essential mechanisms involved in the intermodulation process, giving acceptable quantitative accuracy. The key advantage with respect to more complicated approaches is, then, a much easier understanding of the underlying mechanisms. The overall gate voltage is given by the superposition of the rectified LO plus the periodic square-wave offset. The effect of the applied sinusoidal LO will be studied referring to Fig. 12. The rectified sinusoid can be expressed by means of its Fourier series expansion (16) is found by inspection of the circuit. The source voltage The following source voltage sensitivity to the time constant ) results: ( (17) Again, a low-frequency current signal, due to second-order nonlinearity in the input transconductor, modulates the source voltage via time constant modulation. The time constant has content at dc and at all of the even harmonics of the LO frequency. The dc term has no effect because the corresponding current in the capacitor is null. The terms at frequencies are indeed important. In fact, referring to the mixer output versus input current relation, reported in Fig. 10(b), we realize that the train of pulses originating the direct leakage is also responsible . The train of pulses can for a finite transmission at be expressed as (18) From (15) and (19), the output second-order intermodulation currents, due to source-voltage sidebands around even as well as odd harmonics of the LO fundamental frequency, are both important. This is not surprising even though they are originated by intermodulation of the low-frequency current tone with impressed signals, having magnitudes that are largely different. In fact, the large LO sinusoid determines sidebands around proportional to the peak amplitude , while the switching-pair . On the other hand, the sideleakage is proportional to are directly proportional to the offset bands around and downconverted by the switching stage (i.e., voltage with maximum conversion gain). By means of (11), (15), and (19), the overall leakage gain is found to be (20) From (20), the direct and the two indirect gains can add , i.e., the overall or subtract depending on the value of leakage gain magnitude can be lower than the leakage gain magnitude due to each single term. As a consequence, de, i.e., the biasing conditions at a given LO pending on frequency, the IIP2 can be higher than due to each separate mechanism. To validate the analysis, the circuit in Fig. 10(a) has been simulated, injecting a low-frequency tone, at the switching-stage is 1.5 mA, the offset common source. The biasing current is 2 mV, the LO frequency is 2.1 GHz, and the simvoltage ulation has been repeated for various LO oscillation amplitudes and parasitic capacitance at the common source. Fig. 13 reports the simulation results together with (20) versus the parasitic capacitance. The maximum capacitance shown corresponds to , i.e., a value where the assumptions leading to (20) are still reasonable. Finally, notice that the series in (20) is trun. The agreement between simulations and calcucated for lations is good, especially for moderate LO amplitudes, where the model is expected to be more accurate. More remarkably, Fig. 13 shows, in the entire considered range, a monotonic decrease of the leakage gain, due to canceling between the dif- MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS Fig. 13. Theoretical and simulated leakage gain versus parasitic capacitance at common source, for various LO powers. ferent mechanisms. In particular, for small capacitance, the direct leakage gain dominates. Increasing the capacitance value determines a reduction of the leakage because the indirect mechanisms subtract. A reduction of 7 dB, with respect to the direct leakage value, is predicted with 0.6-pF source capacitance for 6-dBm LO power. Based on the above analysis, an estimate of the achievable IIP2 due to transconductor nonlinearity and switching pair mismatches can be done. From (8), the input intercept second-order ) is given by rms voltage point ( 401 to the mixing operation, and determines a fundamental limit to the achievable IIP2. In Section IV, it has been shown that a low-frequency current tone modulating the switching-stage transconductance determines sidebands around and all its multiples, in the source voltage spectrum. The corresponding sidebands in the capacitor current spectrum are downconverted at the baseband by the switching stage. To describe the intermodulation distortion mechanisms associated with the switching stage, the model assumed in Section IV-B (Fig. 12) can still be used, provided higher order transconductances of active devices, responsible for further intermodulation products generation, are taken into account. A DSB-SC RF current signal injected into the switching stage gives rise to source voltage spectral components at and , due to the transconductance modulation. More, , and over, components at linear combinations of are expected, due to higher order transconductance components with modulation. The most important are those at , because they result in base-band content at mixer output. The detailed circuit solution leading to the IIP2 analytical expression is reported in Appendix B. The output second-order intermodulation currents due to side bands around and , odd and even harmonics of the LO ( respectively) are given by (21) Even considering a mixer with a pseudodifferential transconductor, i.e., the worst-case topology for second-order nonlinearity performances, IIP2 values in excess of 65 dBm can be m m achieved. In fact, let us consider, as an example, transconductor devices, biased at about 5 mA. From (21), dBV (i.e., IIP2 dBm) can be Figs. 9 and 13, IIV2 obtained, provided the LO amplitude is in the order of 6 dBm, and the mismatch between the load resistors is kept below . The use of a fully differential transconductor potentially allows achieving much higher IIP2 values. In this case, the output resistances matching requirement is more relaxed because the second-order common-mode current is lower. V. SWITCHING-PAIR NONLINEARITY AND MISMATCHES Self-mixing and transconductor nonlinearity, together with switching-pair mismatches, can limit the achievable IIP2 of a mixer. Nonetheless, the two phenomena are not intrinsic to the mixer operation, i.e., both can be eliminated, at least in principle. Self-mixing depends on coupling from RF to LO ports and its effect can be eliminated via isolation techniques. AC coupling between the transconductor and the switching stage allows filtering out the transconductor low-frequency current, which originates second-order intermodulation products. Still another source of second-order intermodulation distortion exists. This is associated with the switching pair, is intrinsic (22) and (23) where and are the second-order and third-order transconductance, respectively. , no From (22) and (23), we conclude that for second-order product is generated. This means that at low frequency, for small parasitic capacitance and large biasing currents, the switching stage gives rise to negligible second-order intermodulation products at mixer output. This is not the case when the transconductor is responsible for second-order intermodulation components generation. In fact, the low-frequency second-order intermodulation current at transconductor output is transmitted at the same frequency due to switching-pair duty- 402 Fig. 14. Theoretical and simulated IIP2 due to the switching stage. A typical 20-mS input transconductance is assumed. The series in equations (22) and (23) are truncated for k = 2. cycle distortion even for . This leads to the interesting conclusion that while the achievable IIP2 due to the transconductor will not improve with technology scaling, that due to the switching stage will. Because the latter sets the actual intrinsic limit to the mixer IIP2, technology scaling will allow larger achievable IIP2. To verify (22) and (23), the output second-order intermodulation current in the circuit of Fig. 10(a) has been simulated, injecting a DSB-SC current signal at the switching-stage source. The simulation is repeated for various biasing currents. The corresponding mixer IIP2, assuming 20 mS input stage transconductance, is estimated. Fig. 14 shows both simulations and theoretical calculations versus biasing current. Notice that in the theoretical plot of Fig. 14, the series in (22) and (23) are trun. The agreement is reasonably good in the entire cated for current range. The discrepancy is mainly attributed to the inaccuracy of the model, where, for example, the linear and higher orders transconductances have been assumed constant during the entire period. On the other hand, taking into account that all the parameters are actually periodically time variant would not allow arriving at an analytical solution in explicit form [6]. From Fig. 14, we observe that the IIP2 achieves a local maximum value at low currents, where the distinct mechanisms tend to cancel. Notice that taking into account terms of order higher in the series leads to a worse agreement with simulathan tions. The reason is that higher order terms in the series are actually overestimated, because the assumption of instantaneous switching between the pair devices is less and less valid at higher frequencies. Finally, Fig. 15 shows the simulated IIP2 for different pair device widths. The effect is a slightly different current value where canceling between different mechanisms takes place. From the analysis carried on in the previous two sections, we conclude that while second-order products generated by the input transconductor can be made negligible, by using a fully differential topology or by means of filtering, the intrinsic limit to the achievable IIP2 is determined by the switching stage. When a pseudodifferential topology is used for the transconductor, both the switching pair and the input stage concur to determine the IIP2, and the achievable value depends on the details of the design. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 Fig. 15. Simulated IIP2 due to the switching stage versus biasing current for different device widths. The input stage transconductance is assumed to be 20 mS. VI. MIXER DESIGN AND EXPERIMENTAL RESULTS The test vehicle for the proposed analysis is a direct-conversion 0.18- m CMOS mixer designed for UMTS applications [9]. Because UMTS is a frequency division duplexing system, it requires a highly linear receiver to reject the transmitter leakage, which constitutes a huge interfering signal 130 MHz away from the receiver band. When direct-conversion architecture is adopted, both IIP2 and IIP3 requirements are very stringent. Moreover, to meet the sensitivity requirement, UMTS is also demanding in terms of noise figure. The mixer design noise and high is then particularly tough because low linearity are usually contrasting requirements. In particular, the noise in switching-pair devices are an important source of a direct-conversion CMOS mixer in the gigahertz range [8]. Their contribution to the noise figure is reduced using relatively large areas and low biasing currents [10]. On the other hand, low noise (i.e., large transconductance) and high linearity in the input transconductor are simultaneously achieved only at the expense of current consumption. To reflect these requirements, the input-stage and switching-stage currents are set independently. Fig. 16 shows the diagram of the mixer chosen in this design. The input transconductor is made of a pMOS fully differential input stage shunting an LC-degenerated nMOS stage. In this way, the switching-stage biasing current is the difference between the nMOS and the pMOS currents. To maximize the input-stage IIP2, fully differential transconductors actually offer the best performance. Nonetheless, we have chosen an LC-degenerated nMOS stage for the following reasons. 1) Still in a 0.18- m CMOS technology, the switching-stage nonlinearity constitutes the most important limitation to the achievable IIP2. 2) The low supply voltage of 1.8 V is not sufficient to efficiently realize two shunt fully differential transconductors. Moreover, an LC-degenerated stage has a higher IIP3 for given biasing current. To reduce third-order nonlinearity due to the switching stage, an LC filter resonating at twice the LO frequency has been introduced between the common source and ground. The filter determines low common-mode impedance at twice the LO frequency, i.e., reduces the common-mode oscillation at the MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS Fig. 16. Fig. 17. UMTS receiver block diagram. Fig. 18. Chip photograph. 403 Schematic of the mixer for UMTS. switching-pair common source, increasing IIP3 [6]. Moreover, it allows using larger LO amplitudes with a beneficial effect on IIP2, due to the direct mechanism. Although the results reported in Sections IV and V do not automatically apply to the mixer in Fig. 16, it can be shown that the mechanisms originating IIP2 are exactly the same, the results are qualitatively the same, and analytical expressions can be found in a quite straightforward way. The impact of the filter on gain and noise performances is limited because, for differential signals, it is equivalent to a small capacitance. As mentioned above, the proposed mixer has been embedded in a receiver front-end for UMTS applications. The front-end block diagram, comprising a low-noise amplifier (LNA), a quadrature mixer, and a variable-gain amplifier (VGA), is shown in Fig. 17. A classical inductively degenerated LC-loaded LNA provides 16-dB gain. After the mixers, VGAs further amplify the signal by 19 dB. A low-frequency loop around the VGA cancels any dc offset and creates a high-pass transfer function with a cutoff frequency of 3 kHz. The chip was fabricated in a 0.18- m six-metal-layers CMOS technology, from STMicroelectronics. Fig. 18 shows the chip photograph. Particular care was taken to have highly symmetric quadrature signal paths. It was also very important to have a cross symmetry between the RF and LO lines so that differential RF-to-LO and LO-to-RF couplings were minimized. The LO is externally supplied. For testing purposes, the available test pins are RF input, mixer LO inputs (terminated externally with 50- differential resistors), mixer outputs, and VGA outputs. Notice that this prototype is appropriate to prove the analysis of IIP2 in mixers, presented in this paper, because low-frequency second-order products generated by the LNA are completely rejected at mixer input, due to the LNA resonant load. All the measurements have been performed while the circuit is supplied by a 1.8-V source. The RF-to-LO isolation is 65 dB. Equation (5) suggests that the receiver IIP2 due to self-mixing is around 70–75 dBm for LO powers ranging from 1 to 4 dBm. This means that, given 16 dB of LNA gain, the IIP2 at mixer input is in the range of 86–91 dBm. Of course, this is not the only mechanism determining the mixer IIP2. To prove the validity of the theory proposed in Section III, a fraction of the RF signal has been purposely injected into the LO input and the output IM2 measured as a function of the LO power. The two tones, representative of the transmitter leakage, are at 1980 and 1980.5 MHz, resulting in an output second-order intermodulation at 0.5 MHz. The received signal is at 2111 MHz and the LO is at 2110 MHz, with an output signal at 1 MHz. Fig. 19 shows measured and theoretical IIP2 versus LO power, with 28 dB RF-to-LO signal ratio. For high LO powers, a very good agreement is evident. For low LO powers, a small difference is observed, as expected from circuit simulations. Prior to the characterization of the mixer IIP2, due to the intrinsic mechanisms, the load resistances have been measured. At the time of the design, not all the mechanisms determining the IIP2 and described in this paper were completely understood. In particular, the impact of the resistor accuracy on IIP2 was not quantitatively clear. The measured relative accuracy of 1/600 is in good agreement with the design, but does not allow IIP2 values higher than about 66 dBm. Because higher peak values are expected, perfect load match has been achieved by shunting 404 Fig. 19. Measured and theoretical IIP2 versus LO power with RF-to-LO coupling. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 028-dB Fig. 21. Measured IIP2 versus switching-stage biasing current for various LO powers. To complete the receiver characterization, noise figure and IIP3 measurements have been performed. The receiver out-of-band IIP3, which is mainly determined by the mixer, measured as specified by UMTS, is 2 dBm. Finally, the receiver noise figure (integrated from 10 kHz to 1.92 MHz) is 6.2 dB. The receiver front-end performances meet the requirement specified by UMTS. VII. CONCLUSION AND DISCUSSION Fig. 20. Measured and simulated mixer IIP2 versus switching-stage biasing current. The LO power is 6 dBm. external resistors. The same frequency plan used for self-mixing characterization has been used to characterize the intrinsic IIP2. Fig. 20 shows the measured and simulated mixer IIP2 versus the switching-pair biasing current with 5-dBm LO power. The standing current in the pMOS transconductor is kept constant and equal to 1.8 mA. Notice that the simulations at large currents were performed using very low-load resistors. As expected, at low current values, the switching pairs’ indirect mechanisms determine the IIP2, while at high currents, the IIP2 is limited by the nonlinearity in the transconductor. The agreement between measurements and simulations is very good in the entire range, even though measured values peak in a slightly narrower current range. Values higher than 65 dBm are measured in the range 1.1–1.6 mA, with a maximum value as high as 75 dBm. Considering that the LNA gain is 16 dB, the mixer satisfies, in the above current range, the IIP2 requirement of a UMTS system, specified as about 48 dBm at antenna. Fig. 21 shows the measured IIP2 versus current for different LO powers. Values higher than 60 dBm are measured in the range 1–1.7 mA. The systematic approach in the analysis of second-order products generations in mixers, proposed in this paper, has disclosed interesting insights into the underlying mechanisms. Quantitative results for self-mixing as well as for the intrinsic mechanisms have been derived. In particular, the paramount importance of the parasitic capacitance loading the switching stage has been discussed in depth, for the first time. The paper employs a simple equivalent circuit for the current-switching stage, first proposed in [8], even though more accurate device modeling is required to capture the intermodulation phenomena responsible for second-order intermodulation products than is required for noise analysis. Both self-mixing and second-order products generated in the input transconductor are not intrinsic to the mixer operation and can be eliminated, at least in principle. On the other hand, second-order products generated by the switching stage are intrinsic and determine the maximum achievable IIP2. From (22) and (23), the switching-stage nonlinearity determines the second-order products at mixer output only in the presence of parasitic capacitance loading the stage. This means not only that at lower frequency this effect is less important, but also that the intrinsic IIP2 is expected to increase at the given frequency in more scaled technologies. APPENDIX A Let us consider the input-stage differential pair of the double balanced mixer, reported in Fig. 7. The Taylor series expansion of the – characteristic of device M is expressed as (A.1) where and are, respectively, the gate and source voltages. MANSTRETTA et al.: SECOND-ORDER INTERMODULATION MECHANISMS IN CMOS DOWNCONVERTERS The source voltage is related to the input voltage by the following Volterra series expansion: H H (A.2) 405 sinusoid . The RF DSB-SC input current signal . is The – characteristic of device M is expressed by means of its Taylor series expansion is the linear transfer function. H is found where H by applying the Kirchoff law at the source node, i.e., Y (A.3) and , as defined in (9), By means of (A.1)–(A.3), can be derived. After some simplifications (B.1) The solution is found by applying the Kirchoff law (with ) and expressing versus the applied input signals by means of a Volterra series expansion H Y (B.2) Y (A.4) (A.5) Y Y . with Assuming no mismatches, the small-signal coefficients are and ) and is equal ( null. Low-frequency output intermodulation products are found . As a consequence, in the for . Moreover, if the LC LC-degenerated topology, Y , tank resonates approximately at the input frequencies Y . Under these assumptions Y , the third-order nonlinear transfer function with linear input voltage and input current square, is only . In particular, responsible for sidebands around determines two sidebands in the source , all voltage spectrum. To determine the transfer functions in (B.2) need to be determined. After calculations and simplifications (B.3) pseudodifferential and LC degenerated Y fully differential. (A.6) is null, its sensitivity to mismatches is not. Although , In presence of mismatches, , , and , variable is either or . Taking the where the generic derivative of (A.5) with respect to gives pseudodifferential LC degenerated fully differential Let us first consider the sidebands in the source voltage around odd harmonics of the LO frequency, due to the square-wave offset signal. Expanding the square-wave offset in a Fourier series and by means of (B.3), the sidebands in the source voltage spectrum are found. The corresponding sidebands in the capacitor current spectrum are given by (B.4) . where The current is downconverted at baseband by the switching stage with a transfer function well approximated by a square wave toggling between 1 and 1, in phase with the gate voltage. The upper and lower sidebands add to each other after downconversion. The resulting output intermodulation current is given by (A.7) Assuming the devices working in strong inversion, Table I follows. APPENDIX B Referring to the circuit in Fig. 12, we look for second-order , due intermodulation components in the output current , with . We conto sidebands generated around : a square wave, toggling sider two applied input signals with period , and a large rectified between 0 and Cv (B.5) From (B.3) and (B.5), assuming , (22) follows. The sidebands around even harmonics of the LO frequency are due to the equivalent rectified sinusoid at the gate. The Fourier series expansion of the gate voltage is reported in (16). 406 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 (B.6) Again, from (B.3), the source voltage is found. The current induced in the tail capacitor is given by (B.6), shown at the top of the page. Multiplying (B.6) times (19) gives the output intermodulation current [9] D. Manstretta, R. Castello, F. Gatta, P. Rossi, and F. Svelto, “A 0.18-m CMOS direct conversion receiver front-end for UMTS,” in IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers, Feb. 2002, pp. 240–241. [10] D. Manstretta, R. Castello, and F. Svelto, “Low 1/f noise CMOS active mixers for direct conversion,” IEEE Trans. Circuits Syst. II, vol. 48, pp. 846–850, Sept. 2001. (B.7) Danilo Manstretta (M’98) was born in Broni, Italy, in 1973. He received the Laurea degree (summa cum laude) and the Ph.D. degree in electrical engineering and computer science from the University of Pavia, Pavia, Italy, in 1998 and 2002, respectively. During his studies, he worked on CMOS RF front-end circuits for wireless applications. In 2001, he joined Agere Systems, Berkeley Heights, NJ, as a Member of Technical Staff. His current research interests are in the field of highly integrated transceivers for WLANs. From (B.3) and (B.7), assuming and , (23) follows. ACKNOWLEDGMENT The authors wish to thank M. Paparo and M. Bonaventura of STMicroelectronics for technology access, and R. Castello, F. Gatta, and P. Rossi, who worked on the UMTS receiver realization. REFERENCES [1] A. A. Abidi, “Direct conversion radio transceivers for digital communications,” IEEE J. Solid-State Circuits, vol. 30, pp. 1399–1410, Dec. 1995. [2] B. Razavi, “Design considerations for direct-conversion receivers,” IEEE Trans. Circuits Syst. II, vol. 44, pp. 428–435, June 1997. [3] S. Laursen, “Second-order distortion in CMOS direct conversion receivers for GSM,” in Proc. Eur. Solid State Circuits Conf. (ESSCIRC), Sept. 1999, pp. 342–345. [4] L. Sheng, J. C. Jensen, and L. E. Larson, “A wide-bandwidth Si/SiGe HBT direct conversion sub-harmonic/downconverter,” IEEE J. SolidState Circuits, vol. 35, pp. 1329–1337, Sept. 2000. [5] K. Kivekas, A. Parssinen, and K. A. I. Halonen, “Characterization of IIP2 and dc offsets in transconductance mixers,” IEEE Trans. Circuits Syst. II, vol. 48, pp. 1028–1038, Nov. 2001. [6] M. T. Terrovitis and R. G. Meyer, “Intermodulation distortion in currentcommutating CMOS mixers,” IEEE J. Solid-State Circuits, vol. 35, pp. 1461–1473, Oct. 2000. [7] Y. Tsividis, Operation and Modeling of the MOS Transistor, 2nd ed. New York: McGraw-Hill, 1999. [8] H. Darabi and A. A. Abidi, “Noise in RF-CMOS mixers: A simple physical model,” IEEE J. Solid-State Circuits, vol. 35, pp. 15–25, Jan. 2000. Massimo Brandolini (S’03) was born in Broni, Italy, in 1977. He received the Masters degree in electronics engineering from the University of Pavia, Pavia, Italy, in 2002. He is currently working toward the Ph.D. degree in the area of CMOS RF transceivers design in the Microelectronics Laboratory, University of Pavia. His current research activity is focused on RF front-end design for multistandard applications. Francesco Svelto (S’94–M’98) received the Ph.D. degree in electronics and computer science from the University of Pavia, Pavia, Italy, in 1995. His Ph.D. dissertation focused on low-noise design for instrumentation. In 1997, he joined the University of Bergamo, Bergamo, Italy, as an Assistant Professor and, in 2000, he was appointed an Associate Professor at the University of Pavia. His current research interests are in the field of CMOS RF design and high-frequency integrated circuits for telecommunications. Dr. Svelto has been a Member of the Technical Committee of the IEEE Custom Integrated Circuits Conference (CICC) since 2000. He was a Member of the Technical Committee of the European Solid State Circuits Conference (ESSCIRC) in 2002.