* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Power Electronic Devices - University of Washington

Three-phase electric power wikipedia , lookup

Cavity magnetron wikipedia , lookup

Electric power system wikipedia , lookup

Stray voltage wikipedia , lookup

Electrical ballast wikipedia , lookup

Power inverter wikipedia , lookup

Power over Ethernet wikipedia , lookup

History of electric power transmission wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Power engineering wikipedia , lookup

Current source wikipedia , lookup

Integrated circuit wikipedia , lookup

Electrical substation wikipedia , lookup

Mains electricity wikipedia , lookup

Earthing system wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Power electronics wikipedia , lookup

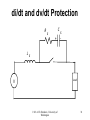

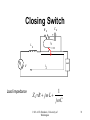

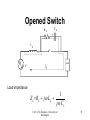

Chapter 2 Power Electronic Devices Bi-polar Transistor (BJT) (C) (C) (C) IC Collector Base (B) VCB N IB (B) P N VCE (B) VBE Emitter IE (E) (E) IC I B I E I B IC (E) VCE VCB VBE (C) Characteristics of Bi-polar Transistor IC VCB IB VCE (B) VBE IE IB Saturation Region IC (E) IB1 IB2< IB1 Linear Region IB= 0 V 0.6 BE Base Characteristics Cut Off Region VCE Collector Characteristics IC IB max IC RL VCC RL IB (1) V CE V CC (2) IB = 0 VCC VCE RL IC At point (1) VCE is very small VCC IC RL Closed switch Open switch VCC At point (2) IC is very small VCE VCC VCE Main Features of BJT • Current controlled device – Base current must be present during the closing period – High base losses • Low current gain in the saturation region • Can operate at high frequencies Field Effect Transistor (FET) ID (D) V GS1 ID VGS2 < V GS1 (G) VDS VGS3 < V GS2 VGS 0 < VGS4 < V GS3 (S) VDS Main Features of FET • Voltage controlled device • Low gate losses Thyristors (Four Layer Diode) Anode (A) Anode (A) IA Anode (A) IA IA P N P N P N P VRB Q1 Q2 N PIh N Ic2 Q1 Ic1 Q2 VBO IA Cathode (K) Cathode (K) Cathode (K) VAK Thyristors [Silicon Controlled Rectifier (SCR)] Anode (A) I A Ig = max Ig > 0 Gate (G) VRB Ig = 0 Ih V AK Cathode (K) V TO VBO Closing Conditions of SCR 1. Positive anode to cathode voltage (VAK) 2. Maximum triggering pulse is applied (Ig) Anode (A) Gate (G) Cathode (K) Closing angle is a Opening Conditions of SCR 1. Anode current is below the holding value (Ih) VRB I A Ig = 0 Ih V AK Opening angle is Ratings of Power Electronic Devices • Steady State Circuit ratings: • The current and voltage of the circuit should always be less than the device ratings. Ratings of Power Electronic Devices • Junction temperature: Losses inside solid-state devices are due to impurities of their material as well as the operating conditions of their circuits. Ratings of Power Electronic Devices • During the conduction period, the voltage drop across the solid-state device is about one volt. This voltage drop multiplied by the current inside the device produces losses. • When the device is in the blocking mode (open), a small amount of leakage current flows inside the device which also produces losses. • The gate circuits of the SCRs and FETs, and the base circuits of the transistors, produce losses due to their triggering signals. • Every time the solid state device is turned on or off, switching losses are produced. These losses are usually higher for faster devices, and for devices operating in high frequency modes. Ratings of Power Electronic Devices • Surge current: It is the absolute maximum of the non-repetitive impulse current Ratings of Power Electronic Devices • Switching time: • Turn-on time is the interval between applying the triggering signal and the turn-on of the device. • The turn-off time is the interval from the onstate to the off-state. • The larger the switching time the smaller is the operating frequency of the circuit. Ratings of Power Electronic Devices • Critical rate of rise of current (or maximum di/dt): A solid-state device can be damaged if the di/dt of the circuit exceeds the maximum allowable value of the device. di/dt damage can occur even if the current is below the surge limit of the device. To protect the device from this damage, a snubbing circuit for di/dt must be used. Ratings of Power Electronic Devices • Critical rate of rise of voltage (or maximum dv/dt): When dv/dt across a device exceeds its allowable limit, the device is forced to close. This is a form of false triggering. It may lead to excessive current or excessive di/dt. To protect the device against excessive dv/dt, a snubbing circuit for dv/dt must be used. di/dt and dv/dt Protection R s Cs + - Ls Load V © M. A. El-Sharkawi, University of Washington 32 Closing Switch Cs + - Rs I2 Ls V Load impedance I Load 1 Z L R j L 1 j C © M. A. El-Sharkawi, University of Washington 33 Closing Switch: Analysis of I1 Ls V I1 ( S ) I Load 1 LL, RL, CL V (S ) 1 R SL CS © M. A. El-Sharkawi, University of Washington L Ls LL 34 Closing Switch: Analysis of I1 Ls V i1 (t ) I C V n (1 ) 2 Load 1 e n t sin n (1 2 ) t 1 R C n ; LC 2 L © M. A. El-Sharkawi, University of Washington 35 Snubbing Circuit: Ls di1 CV n2 n t e sin [n (1 2 ) t ]CV n2 e n t cos[n (1 2 ) t ] dt (1 2 ) Worst Scenario for Maximum di/dt: When the load capacitor is not charged at t=0 di1 dt max CV 2 n V di1 dt max L 1 n LC V Ls LL di1 dt max VBO Ls LL di 0.1 dt rating © M. A. El-Sharkawi, University of Washington 36 Closing Switch: Analysis of I2 The fully charged cap discharges after the switch is closed Ls V Vo i2 e Rs Cs + - Rs I2 t Rs C s Load Vo di2 e 2 dt Rs C s © M. A. El-Sharkawi, University of Washington t Rs C s 37 Closing Switch: Analysis of I2 Cs + - Rs Ls V Vo di2 e dt Rs2 C s t Rs C s At t = 0 I2 Load Vo di2 dt R 2 C max s s di2 di Let 0.1 dt max dt rating © M. A. El-Sharkawi, University of Washington 38 Opened Switch Rs Cs + - Ls V I Load 3 Load impedance 1 Z L RL j LL j C L © M. A. El-Sharkawi, University of Washington 39 Opened Switch Cs + - Rs Ls R Rs RL V I I3 (S ) 3 V (S ) Load L Ls LL Cs C L C Cs C L 1 R SL CS © M. A. El-Sharkawi, University of Washington 40 Opened Switch Assume the caps are initially discharged Cs + - Rs Vsw Rs i3 Ls dVsw di3 Rs dt dt V I 3 Load dVsw V Rs dt L © M. A. El-Sharkawi, University of Washington 41 Selection of the Snubbing Circuit Parameters Step 1: Compute snubbing inductance VBO Ls LL di 0.1 dt rating Step 2: Compute snubbing Resistance dVsw V Rs dt L Step 3: Compute snubbing Capacitance Vo di 0.1 2 dt rating Rs Cs © M. A. El-Sharkawi, University of Washington 42