* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Single-Channel, 12-/16-Bit Programmable Current Output and

Nanogenerator wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Power MOSFET wikipedia , lookup

Radio transmitter design wikipedia , lookup

Surge protector wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Integrating ADC wikipedia , lookup

Current source wikipedia , lookup

Two-port network wikipedia , lookup

Wilson current mirror wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Power electronics wikipedia , lookup

Operational amplifier wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Current mirror wikipedia , lookup

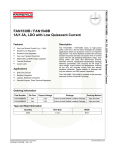

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

Single-Channel, 12- and 16-Bit Programmable Current Output and Voltage Output

Digital-to-Analog Converters for 4-mA to 20-mA Current Loop Applications

Check for Samples: DAC7760, DAC8760

FEATURES

DESCRIPTION

• Current Output: 4 mA to 20 mA;

0 mA to 20 mA; 0 mA to 24 mA

• Voltage Output:

– 0 V to 5 V; 0 V to 10 V; ±5 V; ±10 V

– 0 V to 5.5 V; 0 V to 11 V; ±5.5 V; ±11 V

(10% Overrange)

• ±0.1% FSR Total Unadjusted Error (TUE) Max

• DNL: ±1 LSB Max

• Simultaneous Voltage and Current Output

• Internal 5-V Reference (10 ppm/°C, max)

• Internal 4.6-V Power-Supply Output

• Reliability Features:

– CRC Check and Watchdog Timer

– Thermal Alarm

– Open Alarm, Short Current Limit

• Wide Temperature Range: –40°C to +125°C

• 6-mm × 6-mm QFN-40; TSSOP-24 Packages

The DAC7760 and DAC8760 are low-cost, precision,

fully-integrated, 12-bit and 16-bit digital-to-analog

converters

(DACs)

designed

to

meet

the

requirements

of

industrial

process-control

applications. These devices can be programmed as a

current output with a range of 4 mA to 20 mA, 0 mA

to 20 mA, or 0 mA to 24 mA; or as a voltage output

with a range of 0 V to 5 V, 0 V to 10 V, ±5 V, or ±10

V, with a 10% overrange (0 V to 5.5 V, 0 V to 11 V,

±5.5 V, or ±11 V). Both current and voltage outputs

can be simultaneously enabled while being controlled

by a single data register.

1

234

These devices include a power-on-reset function to

ensure powering up in a known state (both IOUT and

VOUT are disabled and in a Hi-Z state). The CLR

and CLR-SEL pins set the voltage outputs to zeroscale or midscale, and the current output to the low

end of the range, if the output is enabled. Zero and

gain registers can be programmed to digitally

calibrate the device in the end system. The output

slew rate is also programmable by register. These

devices can superimpose an external HART® signal

on the current output and can operate with either a

single +10-V to +36-V supply, or dual supplies of up

to ±18 V. All versions are available in both 6-mm × 6mm QFN-40 and TSSOP-24 packages.

APPLICATIONS

•

•

•

•

•

•

4-mA to 20-mA Current Loops

Analog Output Modules

Building Automation

Environment Monitoring

Programmable Logic Controllers (PLCs)

Field Sensors and Process Transmitters

DVDD

REFOUT

DVDD-EN

DACx760

RELATED DEVICES

REFIN

Internal

Reference

RESOLUTION

(BITS)

CURRENT AND

VOLTAGE OUTPUT

CURRENT

OUTPUT

12

DAC7760

DAC7750

16

DAC8760

DAC8750

AVSS

HART-IN

AVDD

Current Output Stage

DIN

SDO

CLR

CLR-SEL

Control Logic

SCLK

SPI Shift Register

Input Control Logic

BOOST

LATCH

DAC Input

Register

Thermal

Alarm

User Calibration

Gain/Offset

Register

DAC

PreConditioning

IGAIN

IOUT

Current

Source

ALARM

IENABLE

ISET-R

Voltage Output Stage

+VSENSE

Slew Rate

Control

VOUT

VGAIN

–VSENSE

Watchdog

Timer

VENABLE

CMP

GND

1

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

HART is a registered trademark of HART Communication Foundation.

SPI, QSPI are trademarks of Motorola, Inc.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2013, Texas Instruments Incorporated

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

PACKAGE/ORDERING INFORMATION (1)

(1)

PRODUCT

RESOLUTION

TUE (%FSR)

DIFFERENTIAL

NONLINEARITY (LSB)

SPECIFIED TEMPERATURE

RANGE

DAC8760

16

0.2% (IOUT), 0.07% (VOUT)

±1

–40°C to +125°C

DAC7760

12

0.2% (IOUT), 0.07% (VOUT)

±1

–40°C to +125°C

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the

device product folder at www.ti.com.

ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature range (unless otherwise noted). (1)

VALUE

UNIT

AVDD to AVSS

–0.3 to 40

V

AVDD to GND

–0.3 to 40

V

AVSS to GND

–20 to 0.3

V

DVDD to GND

–0.3 to 6

V

VOUT to AVSS

AVSS to AVDD

V

VOUT to GND

(2)

AVSS to AVDD

V

IOUT to AVSS

AVSS to AVDD

V

IOUT to GND (2)

AVSS to AVDD

V

REFIN to GND

–0.3 to 6

V

REFOUT to GND

–0.3 to 6

V

10

mA

Digital input voltage to GND

–0.3 to DVDD + 0.3

V

SDO to GND

–0.3 to DVDD + 0.3

V

Current into REFOUT

ALARM to GND

–0.3 to 6

V

Operating temperature range

–40 to +125

°C

Storage temperature range

–65 to +150

°C

+150

°C

(TJmax – TA)/θJA

W

Human body model (HBM)

1500

V

Charged device model (CDM)

1000

V

Junction temperature range (TJ max)

Power dissipation

Electrostatic discharge (ESD)

ratings

(1)

(2)

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute

maximum conditions for extended periods may affect device reliability.

AVSS tied to GND.

THERMAL INFORMATION

DAC7760, DAC8760

THERMAL METRIC

(1)

RHA (QFN)

PWP (TSSOP)

40 PINS

24 PINS

θJA

Junction-to-ambient thermal resistance

32.9

32.3

θJCtop

Junction-to-case (top) thermal resistance

17.2

14.1

θJB

Junction-to-board thermal resistance

7.5

12.2

ψJT

Junction-to-top characterization parameter

0.2

0.3

ψJB

Junction-to-board characterization parameter

7.5

12.0

θJCbot

Junction-to-case (bottom) thermal resistance

1.4

0.63

(1)

2

UNITS

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

ELECTRICAL CHARACTERISTICS

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN = +5-V external, and DVDD =

+2.7 V to +5.5 V. For VOUT: RL = 1 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications are from –40°C to +125°C,

unless otherwise noted. Typical specifications are at +25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VOLTAGE OUTPUT

Voltage output ranges (normal mode)

AVDD ≥ 10 V

0

5

V

AVDD ≥ 10.5 V

0

10

V

–5

5

V

–10

10

V

AVDD ≥ 10 V

0

5.5

V

AVDD ≥ 11.5 V

0

11

V

AVSS ≤ –6 V, AVDD ≥ 10 V

–5.5

5.5

V

AVSS ≤ –11.5 V, AVDD ≥ 11.5 V

–11

11

AVSS ≤ –5.5 V, AVDD ≥ 10 V

AVSS ≤ –10.5 V, AVDD ≥ 10.5 V

Voltage output range (overrange mode)

Resolution

V

DAC8760

16

Bits

DAC7760

12

Bits

Accuracy (1)

Total unadjusted error, TUE

Differential nonlinearity, DNL

TA = –40°C to +125°C

–0.07

+0.07

%FSR

TA = –40°C to +85°C

–0.06

+0.06

%FSR

TA = +25°C

–0.04

+0.04

%FSR

Monotonic

±1

TA = –40°C to +125°C

Relative accuracy, INL

TA = –40°C to +85°C

Bipolar zero error

Unipolar range (0-5 V,

0-5.5 V, 0-10 V, 0-11

V)

Bipolar range (±5 V,

±5.5 V, ±10 V, ±11 V)

mV

–6

+6

mV

mV

TA = +25°C, ±5 V and ±5.5 V

–1.5

±0.5

+1.5

TA = +25°C, ±10 V and ±11 V

–3

±1

+3

±1

–4

+4

mV

TA = –40°C to +85°C

–2

+2

mV

+0.6

mV

+10

mV

TA = +25°C

–0.6

TA = –40°C to +125°C

–10

TA = +25°C

–3.5

±0.1

±1

+3.5

±2

mV

ppm FSR/°C

TA = –40°C to +125°C, unipolar range

–4

+4

mV

TA = –40°C to +85°C, unipolar range

–2

+2

mV

–0.6

±0.1

+0.6

±1

mV

ppm FSR/°C

TA = –40°C to +125°C

–0.07

+0.07

%FSR

TA = –40°C to +85°C

–0.06

+0.06

%FSR

TA = +25°C

–0.04

±0.01

+0.04

±3

%FSR

ppm FSR/°C

TA = –40°C to +125°C

–0.07

+0.07

%FSR

TA = –40°C to +85°C

–0.06

+0.06

%FSR

TA = +25°C

–0.04

+0.04

%FSR

Full-scale error temperature coefficient

(2)

mV

ppm FSR/°C

TA = –40°C to +125°C

Gain error temperature coefficient

(1)

%FSR

TA = –40°C to +85°C

Offset error temperature coefficient

Full-scale error

±0.022

+7

TA = +25°C, unipolar range

Gain error

%FSR

–7

Zero-scale error temperature coefficient

Offset error

LSB

±0.040

TA = –40°C to +125°C

Bipolar zero error temperature coefficient

Zero-scale error (2)

±0.015

±0.01

±1

ppm FSR/°C

When powered with AVSS = 0 V, INL and offset error for the 0-V to 5-V and 0-V to 10-V ranges are calculated beginning from code

0x0100 for DAC8760 and from code 0x0010 for DAC7760.

Assumes a footroom of 0.5 V.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

3

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN = +5-V external, and DVDD =

+2.7 V to +5.5 V. For VOUT: RL = 1 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications are from –40°C to +125°C,

unless otherwise noted. Typical specifications are at +25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VOLTAGE OUTPUT (for Unipolar and Bipolar Modes)

Headroom

AVDD with respect to VOUT full scale

0.5

Footroom

AVSS with respect to VOUT zero scale

–0.5

Output voltage drift vs time

TA = +125°C, 1000 hrs

Short-circuit current

Load

For specified performance

V

V

±15

ppm FSR

30

mA

1

kΩ

RL = ∞

Capacitive load stability

(3)

20

nF

RL = 1 kΩ

5

nF

RL = 1 kΩ, external compensation capacitor (4 nF)

connected

1

μF

10

μV/V

0

24

mA

0

20

mA

4

20

DC output impedance

Code = 0x8000

DC PSRR (3)

No output load

Ω

0.3

3

CURRENT OUTPUT

Output current ranges

Resolution

mA

DAC8760

16

Bits

DAC7760

12

Bits

Accuracy (for 0-mA to 20-mA and 0-mA to 24-mA range settings) (4)

Total unadjusted error, TUE

Differential nonlinearity, DNL

Relative accuracy, INL

TA = –40°C to +125°C

–0.2

+0.2

%FSR

TA = –40°C to +85°C

–0.16

+0.16

%FSR

TA = +25°C

–0.08

+0.08

%FSR

±1

TA = –40°C to +125°C

(5)

TA = –40°C to +85°C

Offset error

±0.024

%FSR

+0.17

%FSR

TA = –40°C to +85°C

–0.1

+0.1

%FSR

–0.07

External RSET

+0.07

%FSR

ppm FSR/°C

TA = –40°C to +125°C

–0.2

+0.2

%FSR

TA = –40°C to +85°C

–0.16

+0.16

%FSR

TA = +25°C

–0.08

±0.015

+0.08

±5

External RSET

Gain error

±0.01

±5

Internal RSET

Internal RSET

%FSR

–0.17

Offset error temperature coefficient

Full-scale error

LSB

±0.080

TA = –40°C to +125°C

TA = +25°C

Full-scale error

temperature coefficient

±0.02

Monotonic

%FSR

ppm FSR/°C

±10

ppm FSR/°C

–40°C to +125°C

–0.2

+0.2

%FSR

–40°C to +85°C

–0.15

+0.15

%FSR

TA = +25°C

–0.08

+0.08

%FSR

–40°C to +125°C

–0.17

+0.17

%FSR

–40°C to +85°C

–0.12

+0.12

%FSR

TA = +25°C

–0.05

±0.01

±0.01

+0.05

%FSR

Gain error temperature

coefficient

Internal RSET

External RSET

±8

ppm FSR/°C

Output current drift vs

time

Internal RSET

±50

ppm FSR

±25

ppm FSR

(3)

(4)

(5)

4

External RSET

TA = +125°C, 1000 hrs

±3

ppm FSR/°C

Specified by design and characterization; not production tested.

DAC8760 and DAC7760 current output range is set by writing to RANGE bits in control register at address 0x55.

For 0-mA to 20-mA and 0-mA to 24-mA ranges, INL is calculated beginning from code 0x0100 for DAC8760 and from code 0x0010 for

DAC7760.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

ELECTRICAL CHARACTERISTICS (continued)

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN = +5-V external, and DVDD =

+2.7 V to +5.5 V. For VOUT: RL = 1 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications are from –40°C to +125°C,

unless otherwise noted. Typical specifications are at +25°C.

PARAMETER

Accuracy (for 4-mA to 20-mA range setting)

TEST CONDITIONS

Internal RSET

Total unadjusted error,

TUE

External RSET

Differential nonlinearity, DNL

Internal RSET

External RSET

Internal and External

RSET

Internal RSET

Full-scale error

External RSET

%FSR

+0.08

%FSR

TA = –40°C to +125°C

–0.29

+0.29

%FSR

TA = –40°C to +85°C

–0.25

+0.25

%FSR

+0.1

%FSR

–0.1

±0.02

±0.02

Monotonic

±1

±0.024

%FSR

+0.22

%FSR

TA = –40°C to +85°C

–0.2

+0.2

%FSR

TA = –40°C to +125°C

–0.2

+0.2

%FSR

TA = –40°C to +85°C

–0.18

+0.18

%FSR

TA = +25°C

–0.07

+0.07

%FSR

TA = –40°C to +125°C

–0.25

TA = +25°C

–0 .08

TA = –40°C to +125°C

±0.01

±3

%FSR

+0.08

%FSR

–0.29

+0.29

%FSR

TA = –40°C to +85°C

–0.25

+0.25

%FSR

TA = +25°C

–0 .1

+0.1

%FSR

±0.015

±0.015

±5

External RSET

ppm FSR/°C

+0.25

±10

Gain error

%FSR

–0.22

External RSET

Internal RSET

LSB

±0.080

TA = –40°C to +125°C

Internal RSET

Output current drift vs

time

+0.25

–0.08

Offset error temperature coefficient

Internal RSET

UNIT

–0.25

TA = –40°C to +85°C

Gain error temperature

coefficient

MAX

TA = +25°C

TA = –40°C to +125°C

Relative accuracy, INL (7)

Full-scale error

temperature coefficient

TYP

TA = –40°C to +125°C

TA = +25°C

Offset error

MIN

(6)

ppm FSR/°C

ppm FSR/°C

TA = –40°C to +125°C

–0.2

+0.2

%FSR

TA = –40°C to +85°C

–0.15

+0.15

%FSR

TA = +25°C

–0.08

+0.08

%FSR

TA = –40°C to +125°C

–0.16

+0.16

%FSR

TA = –40°C to +85°C

–0.12

+0.12

%FSR

TA = +25°C

–0.05

±0.01

±0.01

+0.05

%FSR

±3

ppm FSR/°C

External RSET

±8

ppm FSR/°C

Internal RSET

±50

ppm FSR

±75

ppm FSR

External RSET

TA = +125°C, 1000 hrs

CURRENT OUTPUT CHARACTERISTICS (8)

Loop compliance voltage (9)

Output = 24 mA

AVDD – 2

Inductive load

50

DC PSRR

Output impedance

1

Code = 0x8000

V

mH

50

μA/V

MΩ

EXTERNAL REFERENCE INPUT

Reference input voltage

External reference current

4.95

REFIN = 5.0 V, outputs off or IOUT enabled

Reference input capacitance

(6)

(7)

(8)

(9)

5

5.05

V

30

μA

10

pF

DAC8760 and DAC7760 current output range is set by writing to RANGE bits in control register at address 0x55.

For 0-mA to 20-mA and 0-mA to 24-mA ranges, INL is calculated beginning from code 0x0100 for DAC8760 and from code 0x0010 for

DAC7760.

Specified by design and characterization; not production tested.

Loop compliance voltage is defined as the voltage at the IOUT pin.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

5

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN = +5-V external, and DVDD =

+2.7 V to +5.5 V. For VOUT: RL = 1 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications are from –40°C to +125°C,

unless otherwise noted. Typical specifications are at +25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

INTERNAL REFERENCE OUTPUT

Reference output

TA = +25°C

Reference temperature coefficient (10)

TA = –40°C to +85°C

Output noise (0.1 Hz to 10 Hz)

TA = +25°C

Noise spectral density

TA = +25°C, 10 kHz

4.995

±10

Capacitive load

Load current

Short-circuit current (REFOUT shorted to GND)

AVDD = 24 V, AVSS = 0 V, TA = +25°C, sourcing

Load regulation

5.005

AVDD = 24 V, AVSS = 0 V, TA = +25°C, sinking

Line regulation

V

ppm/°C

14

μVPP

185

nV/√Hz

600

nF

±5

mA

25

mA

55

μV/mA

120

μV/mA

±1.2

μV/V

DVDD INTERNAL REGULATOR

Output voltage

AVDD = 24 V

4.6

Output load current (10)

V

10

Load regulation

3.5

Line regulation

mV/mA

1

Short-circuit current

AVDD = 24 V, to GND

mV/V

35

Capacitive load stability (10)

mA

mA

2.5

μF

DIGITAL INPUTS

VIH, input high voltage

2

VIL, input low voltage

V

3.6 V < AVDD < 5.5 V

0.8

V

2.7 V < AVDD < 3.6 V

0.6

V

Hysteresis voltage

0.4

DVDD-EN, VIN ≤ 5 V

Input current

All pins other than DVDD-EN

Pin capacitance

V

μA

–2.7

±1

Per pin

10

μA

pF

DIGITAL OUTPUTS

VOL, output low voltage

SDO

VOH, output high

voltage

Sinking 200 μA

Sourcing 200 μA

0.4

DVDD –

0.5

V

High-impedance

leakage

ALARM

V

±1

μA

VOL, output low voltage

10-kΩ pull-up resistor to DVDD

0.4

V

VOL, output low voltage

2.5 mA

0.6

V

±1

μA

High-impedance

leakage

High-impedance output capacitance

10

pF

(10) Specified by design and characterization; not production tested.

6

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

ELECTRICAL CHARACTERISTICS (continued)

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN = +5-V external, and DVDD =

+2.7 V to +5.5 V. For VOUT: RL = 1 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications are from –40°C to +125°C,

unless otherwise noted. Typical specifications are at +25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

POWER REQUIREMENTS

AVDD

AVDD + |AVSS| ≤ 36 V

10

36

V

AVSS

AVDD + |AVSS| ≤ 36 V

–18

0

V

DVDD

Internal regulator disabled

2.7

5.5

V

Outputs disabled, external DVDD

3

Outputs disabled, internal DVDD

AIDD

4

Code = 0x8000, VOUT enabled, unloaded

4.6

Code = 0x0000, IOUT enabled

AISS

DIDD

Power dissipation

mA

3

Code = 0x0000, both outputs enabled, VOUT

unloaded

4.6

Outputs disabled

0.6

Outputs disabled, Internal DVDD

0.6

Code = 0x8000, VOUT enabled, unloaded

2.6

Code = 0x0000, IOUT enabled

0.6

Code = 0x0000, both outputs enabled, VOUT

unloaded

2.6

VIH = DVDD, VIL = GND, interface idle

1

AVDD = 36 V, AVSS = GND, VOUT enabled,

unloaded, DVDD = 5 V

140

mA

mA

170

mW

AVDD = 18 V, AVSS = –18 V, VOUT enabled,

unloaded, DVDD = 5 V

135

TEMPERATURE

Specified performance range

–40

Thermal alarm

Thermal alarm hysteresis

+125

°C

18

°C

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

°C

142

7

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

ELECTRICAL CHARACTERISTICS: AC

At AVDD = +10 V to +36 V, AVSS = –18 V to 0 V, AVDD + |AVSS| ≤ 36 V, GND = 0 V, REFIN= +5-V external; and DVDD =

+4.5 V to +5.5 V. For VOUT: RL = 2 kΩ, CL = 200 pF; for IOUT: RL = 300 Ω. All specifications –40°C to +125°C, unless

otherwise noted. Typical specifications are at +25°C.

PARAMETER (1)

TEST CONDITIONS

MIN

TYP

MAX

UNIT

DYNAMIC PERFORMANCE

CURRENT OUTPUT

16-mA step, to 0.1% FSR, no L (inductance)

10

μs

16-mA step, to 0.1% FSR, L < 1 mH

25

μs

–75

dB

0 V to 10 V, to ±0.03% FSR

22

μs

0 V to 5 V, to ±0.03% FSR

13

μs

Slew rate

0.5

V/μs

Power-on glitch energy

2.5

µV-s

Digital-to-analog glitch energy

0.4

µV-s

Glitch impulse peak amplitude

200

mV

2

nV-s

Output current settling time

AC PSRR

200-mV, 50-Hz or 60-Hz sine wave

superimposed on power-supply voltage

VOLTAGE OUTPUT

Output voltage settling time

Digital feedthrough

Output noise (0.1-Hz to 10-Hz bandwidth)

0.1

1 / f corner frequency

100

LSBPP

Hz

Output noise spectral density

Measured at 10 kHz

180

nV/√Hz

AC PSRR

200-mV, 50-Hz or 60-Hz sine wave

superimposed on power-supply voltage

–75

dB

(1)

8

Specified by characterization, not production tested.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

PIN CONFIGURATIONS

NC

DVDD

NC

AVSS

AVDD

NC

–VSENSE

+VSENSE

VOUT

NC

40

39

38

37

36

35

34

33

32

31

RHA PACKAGE

QFN-40

(TOP VIEW)

NC

1

30

NC

ALARM

2

29

CAP2

GND

3

28

CAP1

CLR-SEL

4

27

BOOST

CLR

5

26

IOUT

25

HART-IN

Thermal Pad

(1)

19

20

NC

NC

NC

21

18

10

REFIN

NC

17

NC

REFOUT

22

16

9

ISET-R

SDO

15

DVDD-EN

GND

23

14

8

AVSS

DIN

13

CMP

GND

24

12

7

GND

SCLK

11

6

NC

LATCH

PWP PACKAGE

TSSOP-24

(TOP VIEW)

1

24

AVDD

2

23

–VSENSE

3

22

+VSENSE

4

21

VOUT

5

20

BOOST

6

19

IOUT

18

HART-IN

8

17

CMP

DIN

9

16

DVDD-EN

SDO

10

15

REFIN

11

14

REFOUT

12

13

ISET-R

AVSS

DVDD

ALARM

GND

CLR-SEL

CLR

LATCH

SCLK

GND

GND

(1)

7

Thermal Pad

(1)

Thermal pad connected to AVSS.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

9

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

PIN DESCRIPTIONS

NAME

QFN

NO.

TSSOP

NO.

DESCRIPTION

ALARM

2

3

Alarm pin. Open drain output. External pullup resistor required (10 kΩ). The pin goes

low (active) when the ALARM condition is detected (open circuit, over temperature,

timeout and so forth).

AVDD

36

24

Positive analog power supply.

AVSS

14, 37

1

Negative analog power supply in dual power-supply operation. Connects to GND in

single power-supply operation.

BOOST

27

20

Boost pin. External transistor connection (optional).

CAP1

28

—

Connection for current output filtering capacitor (optional).

CAP2

29

—

Connection for current output filtering capacitor (optional).

CLR

5

6

Clear input. Logic high on this pin causes the part to enter CLEAR state. Active high.

CLR-SEL

4

5

Selects the VOUT value in CLEAR state, after power-on and reset.

CMP

24

17

External compensation capacitor connection pin (optional). Addition of the external

capacitor (connected between VOUT and this pin) improves the stability with high

capacitive loads at the VOUT pin by reducing the bandwidth of the output amplifier,

thus increasing the settling time.

DIN

8

9

Serial data input. Data are clocked into the 24-bit input shift register on the rising

edge of the serial clock input. Schmitt-Trigger logic input.

DVDD

39

2

Digital power supply. Can be input or output, depending on DVDD-EN pin.

DVDD-EN

23

16

Internal power-supply enable pin. Connect this pin to GND to disable the internal

supply, or leave this pin unconnected to enable the internal supply. When this pin is

connected to GND, an external supply must be connected to the DVDD pin.

Ground reference point for all digital circuitry of the device. Connects to 0 V.

GND

3

4

GND

12, 13, 15

11, 12

HART-IN

25

18

Input pin for HART modulation.

IOUT

26

19

Current output pin

ISET-R

16

13

Connection pin for external precision resistor (15 kΩ). See the THEORY OF

OPERATION section of this data sheet.

LATCH

6

7

Load DAC registers input. A rising edge on this pin loads the input shift register data

into the DAC data and control registers and updates the DAC outputs.

1, 10, 11, 19,

20, 21, 22, 30,

31, 35, 38, 40

—

No connection.

REFOUT

17

14

Internal reference output. Connects to REFIN when using internal reference.

REFIN

18

15

Reference input

SCLK

7

8

Serial clock input of serial peripheral interface ( SPI™). Data can be transferred at

rates up to 30 MHz. Schmitt-Trigger logic input.

SDO

9

10

Serial data output. Data are valid on the rising edge of SCLK.

NC

Ground reference point for all analog circuitry of the device.

THERMAL PAD

—

—

The thermal pad is internally connected to the AVSS supply. It is recommended that

the pad be thermally connected to a copper plane for enhanced thermal performance.

The pad can be electrically connected to the same potential as the AVSS pin (either

negative supply voltage or GND) or left electrically unconnected provided a supply

connection is made at the AVSS pin. The AVSS pin must always be connected to

either the negative supply voltage or GND, independent of the thermal pad

connection.

VOUT

32

21

Voltage output pin. This is a buffered analog voltage output.

+VSENSE

33

22

Sense pin for the positive voltage output load connection.

–VSENSE

34

23

Sense pin for the negative voltage output load connection.

10

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TIMING CHARACTERISTICS

t1

1

SCLK

2

24

t2

t3

t4

t5

LATCH

DIN

t8

t7

t6

DB23

DB0

t9

CLR

t10

IOUT/VOUT

Figure 1. Write Mode Timing

TIMING REQUIREMENTS: Write Mode

At TA = –40°C to +125°C and DVDD = +2.7 V to +5.5 V, unless otherwise noted.

PARAMETER (1)

MIN

MAX

UNIT

t1

SCLK cycle time

33

ns

t2

SCLK low time

13

ns

t3

SCLK high time

13

ns

t4

LATCH delay time

13

ns

t5

LATCH high time (2)

40

ns

t6

Data setup time

5

ns

t7

Data hold time

7

ns

t8

LATCH low time

40

ns

t9

CLR pulse width

20

t10

CLR activation time

(1)

(2)

ns

5

μs

Specified by design, not production tested.

Based on digital interface circuitry only.

When writing to DAC control and config registers, consider the analog output specifications in ELECTRICAL CHARACTERISTICS: AC.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

11

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

t11

t13

1

SCLK

2

24

2

8

9

22

23

24

t14

t12

t15

LATCH

t18

t17

t16

DIN

1

DB23

DB0

NOP condition

DB23

DB0

t20

Input word specifies

register to be read

t19

X

SDO

X

X

X

DB16

DB0

Undefined data

First eight bits are

don’t care bits

Selected register

data clocked out

Figure 2. Readback Mode Timing

TIMING REQUIREMENTS: Readback Mode

At TA = –40°C to +125°C and DVDD = +2.7 V to +5.5 V, unless otherwise noted.

PARAMETER (1)

MIN

MAX

UNIT

t11

SCLK cycle time

60

ns

t12

SCLK low time

25

ns

t13

SCLK high time

25

ns

t14

LATCH delay time

13

ns

t15

LATCH high time

40

ns

t16

Data setup time

5

ns

t17

Data hold time

7

ns

t18

LATCH low time

t19

Serial output delay time (CL, SDO = 15 pF)

35

ns

t20

LATCH rising edge to SDO 3-state (CL, SDO = 15 pF)

35

ns

(1)

12

40

ns

Specified by design, not production tested.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

t21

t23

1

SCLK

2

25

24

26

48

t24

t22

t25

LATCH

DIN

DB23

DB0

Input word for DAC-N

SDO

DB23

Undefined

DB23

t29

DB0

t28

t27

t26

DB0

Input word for DAC-N - 1

DB23

t20

DB0

Input word for DAC-N

Figure 3. Daisy-Chain Mode Timing

TIMING REQUIREMENTS: Daisy-Chain Mode

At TA = –40°C to +125°C and DVDD = 2.7 V to 5.5 V, unless otherwise noted.

PARAMETER (1)

MIN

MAX

UNIT

t21

SCLK cycle time

60

ns

t22

SCLK low time

25

ns

t23

SCLK high time

25

ns

t24

LATCH delay time

13

ns

t25

LATCH high time

40

ns

t26

Data setup time

5

ns

t27

Data hold time

7

ns

t28

LATCH low time

t29

Serial output delay time (CL, SDO = 15 pF)

(1)

40

ns

35

ns

Specified by design, not production tested.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

13

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS

At TA = +25°C, unless otherwise noted.

5.005

25

30 units shown

AVDD = 24 V

AVSS = 0 V

Reference Output Voltage (V)

5.004

5.003

20

Population (%)

5.002

5.001

5.000

4.999

15

10

4.998

4.997

5

4.995

0

-40

-25

-10

5

20

35

50

Temperature

65

80

95

110

(oC)

125

0.0

1.0

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

4.996

Temperature Drift (ppm/oC)

C003

C002

Figure 4. REFOUT vs TEMPERATURE

Figure 5. INTERNAL REFERENCE TEMPERATURE DRIFT

HISTOGRAM

5.005

5.004

5.003

TA = 25oC

AVSS = 0 V

5.004

AVDD = 24 V

AVSS = 0 V

5.003

5.002

REFOUT (V)

REFOUT (V)

5.002

5.001

5.000

4.999

5.001

5.000

4.999

4.998

4.998

4.997

4.997

4.996

4.996

4.995

-10

-8

-6

-4

-2

0

2

4

6

8

Load Current (mA)

10

10

14

18

22

26

30

AVDD (V)

C001

Figure 6. REFOUT vs LOAD CURRENT

34

38

C002

Figure 7. REFOUT vs AVDD

1000

AVDD = +24 V

AVSS = -12 V

AVDD = 24 V

AVSS = 0 V

800

REFOUT Noise (2 µV/div)

VREF Noise PSD (nV/ rt-Hz)

900

700

600

C = 700 nF

500

C = 0 nF

400

300

200

100

0

10

100

1k

10k

Frequency (Hz)

C006

Figure 8. REFOUT NOISE PSD vs FREQUENCY

14

Time (2 s/div)

100k

C001

Figure 9. INTERNAL REFERENCE, PEAK-TO-PEAK NOISE

(0.1 Hz to 10 Hz)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

5

AVDD = 10 V

AVSS = 0 V

4

AIDD/ AISS (mA)

3

AVDD (4 V/div)

AVDD = |AVSS|

External DVDD

VOUT = 0 V

IOUT disabled

Output unloaded

2

1

AIDD

0

AISS

-1

REFOUT (2 V/div)

-2

-3

Time (200 µs/div)

10

11

12

13

Figure 10. REFOUT TRANSIENT vs TIME

15

16

17

18

C003

Figure 11. AIDD or AISS vs AVDD or AVSS

1.0

3.0

TA = 250C

External DVDD

0.9

2.5

0.8

0.7

DIDD (mA)

2.0

AIDD (mA)

14

AVDD/ |AVSS| (V)

C002

External DVDD

VOUT disabled

IOUT = 0 mA

1.5

1.0

0.6

0.5

0.4

0.3

0.2

0.5

0.1

0.0

0.0

10

13

16

19

22

25

28

31

34

AVDD (V)

37

2.7

3.5

3.9

4.3

4.7

5.1

External DVDD (V)

Figure 12. AIDD vs AVDD

5.5

C001

Figure 13. DIDD vs EXTERNAL DVDD

8

0

TA = 250C

Internal DVDD

7

-10

Internal DVDD PSRR (dB)

6

Internal DVDD (V)

3.1

C004

5

4

3

2

1

0

AVDD = 18 V

AVSS = -18 V

CLOAD = 100 nF

-20

-30

-40

-50

-60

-70

-80

-1

-90

-40

-35

-30

-25

-20

-15

-10

-5

0

Load Current (mA)

5

10

Figure 14. INTERNAL DVDD vs LOAD CURRENT

100

1k

10k

100k

Frequency (Hz)

C002

1M

C001

Figure 15. INTERNAL DVDD PSRR vs FREQUENCY

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

15

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.020

AVDD = +24 V

AVSS = 0 V

Output unloaded

0.03

0.02

0.01

0.00

-0.01

-0.02

+10 V range

+5 V range

-0.03

AVDD = +24 V

AVSS = -12 V

Output unloaded

0.015

Total Unadjusted Error (%FSR)

Total Unadjusted Error (%FSR)

0.04

0.010

0.005

0.000

-0.005

-0.010

-0.015

-0.04

8192

16384

24576

32768

40960

49152

57344

65536

Code

0

8192

16384

24576

32768

40960

49152

57344

65536

Code

C003

Figure 17. VOUT TUE vs CODE

0.030

0.04

0.027

AVDD = |AVSS|

±10 V range

Output unloaded

0.03

0.024

+5 V range

0.021

5 V range

Total Unadjusted Error (%FSR)

Total Unadjusted Error (%FSR)

+5 V range

C003

Figure 16. VOUT TUE vs CODE (Unipolar Outputs)

+10 V range

0.018

10 V range

0.015

0.012

0.009

AVDD = +24 V

AVSS = -12 V

Output unloaded

0.006

0.003

Max Total Unadjusted Error

0.02

0.01

0.00

-0.01

-0.02

Min Total Unadjusted Error

-0.03

0.000

-0.04

-40

-25

-10

5

20

35

50

Temperature

65

80

95

110

125

(0C)

10

11

12

13

14

15

16

17

AVDD/ |AVSS| (V)

C002

Figure 18. VOUT TUE vs TEMPERATURE

18

C002

Figure 19. VOUT TUE vs SUPPLY

0.010

0.010

AVDD = +24 V

AVSS = 0 V

0.008

AVDD = +24 V

AVSS = -12 V

0.008

0.006

0.006

0.004

0.004

INL Error (%FSR)

INL Error (%FSR)

5 V range

+10 V range

-0.020

0

0.002

0.000

-0.002

-0.004

-0.006

0.002

0.000

-0.002

-0.004

Output unloaded

All VOUT ranges

-0.006

+5 V/ +10 V range

Output unloaded

-0.008

-0.008

-0.010

-0.010

0

8192

16384

24576

32768

40960

49152

57344

65536

Code

0

8192

C001

Figure 20. VOUT INL vs CODE (Unipolar Outputs)

16

10 V range

Submit Documentation Feedback

16384

24576

32768

40960

49152

Code

57344

65536

C001

Figure 21. VOUT INL vs CODE

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.010

0.010

0.008

AVDD = +24 V

AVSS = -12 V

Max INL

0.008

INL Error (%FSR)

INL Error (%FSR)

Max INL

0.006

0.006

0.004

0.002

0.000

Output unloaded

All VOUT ranges

-0.002

-0.004

0.004

0.002

±10 V range

AVDD = |AVSS|

Output unloaded

0.000

-0.002

-0.004

Min INL

-0.006

Min INL

-0.006

-0.008

-0.008

-0.010

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (0C)

10

125

11

14

15

16

17

18

C001

Figure 23. VOUT INL vs SUPPLY

1.0

1.0

AVDD = 24 V

AVSS = 0 V

0.8

AVDD = +24 V

AVSS = -12 V

0.8

0.6

DNL Error (LSB)

0.6

DNL Error (LSB)

13

AVDD/ |AVSS| (V)

Figure 22. VOUT INL vs TEMPERATURE

0.4

0.2

0.0

-0.2

-0.4

0.4

0.2

0.0

-0.2

Output unloaded

All VOUT ranges

-0.4

+5 V/ +10 V range

Output unloaded

-0.6

-0.6

-0.8

-0.8

-1.0

-1.0

0

8192

16384

24576

32768

40960

49152

57344

Code

65536

0

8192

16384

24576

32768

40960

49152

57344

Code

C002

Figure 24. VOUT DNL vs CODE (Unipolar Outputs)

65536

C002

Figure 25. VOUT DNL vs CODE

1.0

1.0

0.8

0.6

DNL Error (LSB)

0.4

Max DNL

0.2

0.0

-0.2

-0.4

Output unloaded

All VOUT ranges

-0.6

±10 V range

AVDD = |AVSS|

Output unloaded

0.8

AVDD = +24 V

AVSS = -12 V

0.6

DNL Error (LSB)

12

C002

Min DNL

0.4

Max DNL

0.2

0.0

-0.2

-0.4

Min DNL

-0.6

-0.8

-0.8

-1.0

-1.0

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (0C)

125

10

11

Figure 26. VOUT DNL vs TEMPERATURE

12

13

14

15

16

17

AVDD/ |AVSS| (V)

C003

18

C009

Figure 27. VOUT DNL vs SUPPLY

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

17

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.004

1.0

10 V range

5 V range

+10 V range

+5 V range

AVDD = +24 V

AVSS = -12 V

Output unloaded

0.8

0.6

0.000

0.4

Offset Error (mV)

Full Scale Error (%FSR)

0.002

-0.002

-0.004

AVDD = +24 V

AVSS = -12 V

Output unloaded

-0.006

-0.008

0.2

0.0

-0.2

+10 V range

-0.4

+5 V range

-0.6

-0.010

-0.8

-0.012

-1.0

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (0C)

125

-40

20

35

50

65

80

95

110

125

C005

0.008

AVDD = +24 V

AVSS = -12 V

Output unloaded

AVDD = +24 V

AVSS = -12 V

Output unloaded

0.004

Gain Error (%FSR)

0.8

Bipolar Zero Error (mV)

5

Figure 29. OFFSET ERROR vs TEMPERATURE

1.0

0.6

10 V range

0.4

5 V range

0.2

0.0

0.000

-0.004

-0.008

-0.012

-0.016

10 V range

5 V range

+10 V range

+5 V range

-0.020

-0.2

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (0C)

-40

125

-25

-10

5

20

35

50

65

80

95

110

Temperature (0C)

C006

Figure 30. BIPOLAR ZERO ERROR vs TEMPERATURE

125

C007

Figure 31. GAIN ERROR vs TEMPERATURE

0.010

2.0

AVDD = +24 V

AVSS = -12 V

Output unloaded

0.008

Change in VOUTT (V)

1.6

Zero Scale Error (mV)

-10

Temperature (0C)

Figure 28. VOUT FULL-SCALE ERROR vs TEMPERATURE

1.2

0.8

0.4

0.0

-0.4

0.006

AVDD = +12 V

AVSS = -12 V

±10 V range

0.004

0.002

0.000

-0.002

-0.004

10 V range

5 V range

-0.006

+10 V range

+5 V range

-0.008

-0.010

-0.8

-40

-25

-10

5

20

35

50

65

Temperature (0C)

80

95

110

125

-30 -25 -20 -15 -10

-5

0

5

10

Source / Sink Current (mA)

C008

Figure 32. ZERO-SCALE ERROR vs TEMPERATURE

18

-25

C004

15

20

25

30

C010

Figure 33. VOUT (Full-Scale) vs LOAD CURRENT (Source or

Sink)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.010

VOUT

AVDD = +24 V

AVSS = -12 V

AVDD = +12 V

AVSS = -12 V

±10 V range

0.006

Output Voltage (5 V/div)

Change in VOUTT (V)

0.008

0.004

0.002

0.000

-0.002

-0.004

LATCH

10 V range

CLOAD = 200 pF

-0.006

From code: 0000h

To code: FFFFh

-0.008

-0.010

-25

-20

-15

-10

-5

0

5

10

15

20

Source / Sink Current (mA)

Time (20 µs/div)

25

C001

C009

Figure 34. VOUT (Zero-Scale) vs LOAD CURRENT (Source

or Sink)

Figure 35. BP10V RISING

60

VOUT

AVDD = +24 V

AVSS = -12 V

AVDD = +18 V

AVSS = -18 V

50

Settling Time for 5 V Step (µs)

Output Voltage (5 V/div)

LATCH

10 V range

CLOAD = 200 pF

From code: FFFFh

To code: 0000h

40

CMP = 0 pF

30

20

10

0

Time (20 µs/div)

0

5

Figure 36. BP10V FALLING

15

20

25

C001

Figure 37. VOUT SETTLING TIME vs LOAD (No

Compensation Capacitor)

250

Settling Time for 5 V Step (µs)

70

Settling Time for 5 V Step (µs)

10

Load Capacitor (nF)

C001

AVDD = +18 V

AVSS = -18 V

60

50

CMP = 100 pF

40

30

20

AVDD = +18 V

AVSS = -18 V

200

150

CMP = 470 pF

100

50

0

0

20

40

60

Load Capacitor (nF)

80

100

0

Figure 38. VOUT SETTLING TIME vs LOAD (100 pF Between

VOUT and CMP Pins)

200

400

600

800

Load Capacitor (nF)

C002

1000

C003

Figure 39. VOUT SETTLING TIME vs LOAD (470 pF Between

VOUT and CMP Pins)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

19

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

LOAD = 1 k // 200 pF

VOUT (50 mV/div)

VOUT (50 mV/div)

8000h to 7FFFh

7FFFh to 8000h

Time (20 µs/div)

Time (3 µs/div)

C001

C001

Figure 40. VOUT POWER-ON GLITCH

Figure 41. VOUT DIGITAL-TO-ANALOG GLITCH

900

AVDD = +24V

AVSS = -12V

Output unloaded

700

AVDD = +24 V

AVSS = -12 V

VOUT Noise (1 µV/div)

VOUT Noise PSD (nV/ rt-Hz)

800

600

500

10 V range

400

+5 V range

300

5 V range/ +10 V range

200

100

DAC = midscale

0

10

100

1k

10k

100k

Frequency (Hz)

Time (2 s/div)

C007

Figure 42. VOUT NOISE PSD vs FREQUENCY

C002

Figure 43. VOUT, PEAK-TO-PEAK NOISE (0.1 Hz to 10 Hz)

50

1.2

0.8

Short Circuit Current (mA)

Leakage Current (nA)

1.0

0.6

0.4

0.2

40

35

30

25

20

15

VOUT = 0 V, short circuit to AVDD

10

VOUT = 11 V, short circuit to AVSS

0.0

-0.2

5

-0.4

0

-12

-8

-4

0

4

8

12

VOUT Pin Voltage (V)

16

20

24

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (oC)

C003

Figure 44. VOUT Hi-Z LEAKAGE CURRENT vs VOLTAGE

20

AVDD = 24 V

AVSS = -12 V

45

AVDD = +24 V

AVSS = -12 V

Output disabled

125

C001

Figure 45. VOUT SHORT-CIRCUIT CURRENT vs

TEMPERATURE

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.05

0

VOUT PSRR (dB)

-20

Total Unadjusted Error (%FSR)

AVDD = +18 V

AVSS = -18 V

Output unloaded

-10

-30

-40

-50

-60

+5 V range

-70

10 V range

-80

0.00

-0.10

0 mA - 24 mA Internal RSET

-0.15

0 mA - 24 mA Internal RSET, BOOST

0 mA - 24 mA External RSET

-0.20

0 mA - 24 mA External RSET, BOOST

+10 V Range/ 5 V range

-90

-0.25

10

100

1k

10k

100k

0

1M

Frequency (Hz)

8192

16384

24576

32768

40960

49152

57344

65536

Code

C001

Figure 46. AVDD PSRR FOR VOUT

C009

Figure 47. IOUT TUE vs CODE (0 mA to 24 mA)

0.05

0.05

0.00

Total Unadjusted Error (%FSR)

Total Unadjusted Error (%FSR)

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.05

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.05

-0.10

0 mA - 20 mA Internal RSET

0 mA - 20 mA Internal RSET, BOOST

-0.15

0 mA - 20 mA External RSET

0 mA - 20 mA External RSET, BOOST

-0.20

0.00

-0.05

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.10

-0.15

4 mA - 20 mA Internal RSET

4 mA - 20 mA Internal RSET, BOOST

-0.20

4 mA - 20 mA External RSET

4 mA - 20 mA External RSET, BOOST

-0.25

-0.25

0

8192

16384

24576

32768

40960

49152

57344

Code

65536

0

16384

24576

32768

40960

49152

57344

65536

Code

C006

Figure 48. IOUT TUE vs CODE (0 mA to 20 mA)

C003

Figure 49. IOUT TUE vs CODE (4 mA to 20 mA)

0.12

0.08

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

0.07

Total Unadjuated Error (%FSR)

Total Unadjusted Error (%FSR)

8192

0.06

0.05

0.04

0.03

0 mA to 20 mA

0.02

0 mA to 24 mA

0.01

4 mA to 20 mA

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

0.10

0.08

0.06

0.04

0 mA to 20 mA

0.02

0 mA to 24 mA

4 mA to 20 mA

0.00

0.00

-40

-25

-10

5

20

35

50

65

Temperature (oC)

80

95

110

125

-40

-25

Figure 50. IOUT TUE vs TEMPERATURE (Internal RSET)

-10

5

20

35

50

65

80

95

110

Temperature (oC)

C008

125

C009

Figure 51. IOUT TUE vs TEMPERATURE (External RSET)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

21

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.05

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

Max Total Unadjusted Error

0.04

Total Unadjusted Error (%FSR)

Total Unadjusted Error (%FSR)

0.05

0.03

0.02

0.01

Min Total Unadjusted Error

0.00

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

0.04

Max Total Unadjusted Error

0.03

0.02

0.01

Min Total Unadjusted Error

-0.01

0

10

14

18

22

26

30

34

38

AVDD (V)

10

14

18

22

Figure 52. IOUT TUE vs SUPPLY (Internal RSET)

34

38

C005

0.016

0 mA - 20 mA Internal RSET

0 mA - 24 mA Internal RSET

0.012

0.012

0 mA - 24 mA Internal RSET, BOOST

0 mA - 20 mA Internal RSET, BOOST

0 mA - 20 mA External RSET

0 mA - 24 mA External RSET

0.008

0.008

0 mA - 24 mA External RSET, BOOST

INL Error (%FSR)

INL Error (%FSR)

30

Figure 53. IOUT TUE vs SUPPLY (External RSET)

0.016

0.004

0.000

-0.004

-0.008

0 mA - 20 mA External RSET, BOOST

0.004

0.000

-0.004

-0.008

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.012

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.012

-0.016

-0.016

0

8192

16384

24576

32768

40960

49152

57344

Code

65536

0

8192

16384

24576

32768

40960

49152

57344

Code

C007

Figure 54. IOUT INL vs CODE (0 mA to 24 mA)

65536

C004

Figure 55. IOUT INL vs CODE (0 mA to 20 mA)

0.004

0.016

Max INL

4 mA - 20 mA Internal RSET

0.012

0.002

4 mA - 20 mA Internal RSET, BOOST

4 mA - 20 mA External RSET

0.008

4 mA - 20 mA External RSET, BOOST

INL Error (%FSR)

INL Error (%FSR)

26

AVDD (V)

C006

0.004

0.000

-0.004

0.000

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

All IOUT ranges

-0.002

-0.004

-0.008

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

-0.012

-0.006

Min INL

-0.016

-0.008

0

8192

16384

24576

32768

40960

49152

57344

Code

-40

-25

-10

5

20

35

50

65

Temperature (oC)

C001

Figure 56. IOUT INL vs CODE (4 mA to 20 mA)

22

65536

80

95

110

125

C002

Figure 57. IOUT INL vs TEMPERATURE (Internal RSET)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

0.004

0.015

Max INL

0.000

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

All IOUT ranges

-0.002

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

0.010

INL Error (%FSR)

INL Error (%FSR)

0.002

-0.004

Max INL

0.005

0.000

-0.005

Min INL

-0.006

-0.010

Min INL

-0.015

-0.008

-40

-25

-10

5

20

35

50

65

80

95

110

10

125

Temperature (oC)

22

26

30

34

38

C004

Figure 59. IOUT INL vs SUPPLY (Internal RSET)

0.015

1.0

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

0.010

AVDD = 24 V

AVSS = 0 V

0.8

0.6

Max INL

0.005

DNL Error (LSB)

INL Error (% FSR)

18

AVDD (V)

Figure 58. IOUT INL vs TEMPERATURE (External RSET)

0.000

-0.005

0.4

0.2

0.0

-0.2

-0.4

-0.6

-0.010

0 mA to 24 mA range

RLOAD = 300

-0.8

Min INL

-0.015

-1.0

10

14

18

22

26

30

34

38

AVDD (V)

0

8192

16384

24576

32768

40960

49152

57344

65536

Code

C003

Figure 60. IOUT INL vs SUPPLY (External RSET)

C008

Figure 61. IOUT DNL vs CODE (0 mA to 24 mA)

1.0

1.0

AVDD = 24 V

AVSS = 0 V

0.8

AVDD = 24 V

AVSS = 0 V

0.8

0.6

0.6

0.4

0.4

DNL Error (LSB)

DNL Error (LSB)

14

C001

0.2

0.0

-0.2

-0.4

-0.6

0.2

0.0

-0.2

-0.4

-0.6

0 mA to 20 mA range

RLOAD = 300

-0.8

4 mA to 20 mA range

RLOAD = 300

-0.8

-1.0

-1.0

0

8192

16384

24576

32768

40960

49152

57344

65536

Code

0

8192

Figure 62. IOUT DNL vs CODE (0 mA to 20 mA)

16384

24576

32768

40960

49152

57344

65536

Code

C005

C002

Figure 63. IOUT DNL vs CODE (4 mA to 20 mA)

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

23

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

1.0

1.0

0.8

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

All IOUT ranges

Max DNL

0.6

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

All IOUT ranges

Max DNL

0.6

DNL Error (LSB)

DNL Error (LSB)

0.4

0.8

0.2

0.0

-0.2

-0.4

-0.6

0.4

0.2

0.0

-0.2

-0.4

-0.6

-0.8

Min DNL

-0.8

Min DNL

-1.0

-1.0

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (oC)

125

-40

-25

-10

5

20

35

50

65

80

Figure 64. IOUT DNL vs TEMPERATURE (Internal RSET)

C011

0.8

Max DNL

Max DNL

0.6

0.6

0.4

0.2

DNL Error (LSB)

DNL Error (LSB)

125

1.0

0.8

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

0.0

-0.2

-0.4

-0.6

0.4

AVSS = 0 V

RLOAD = 300

0 mA to 24 mA range

0.2

0.0

-0.2

-0.4

-0.6

Min DNL

-0.8

Min DNL

-0.8

-1.0

-1.0

10

14

18

22

26

30

34

38

AVDD (V)

10

14

18

22

26

30

34

38

AVDD (V)

C008

Figure 66. IOUT DNL vs SUPPLY (Internal RSET)

C007

Figure 67. IOUT DNL vs SUPPLY (External RSET)

0.18

0.12

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

0.09

Offset Error (%FSR)

0.12

Full Scale Error (%FSR)

110

Figure 65. IOUT DNL vs TEMPERATURE (External RSET)

1.0

0.06

0.00

0 mA to 20 mA Internal RSET

0 mA to 24 mA Internal RSET

-0.06

4 mA to 20 mA Internal RSET

0.06

0.03

0.00

0 mA to 20 mA Internal RSET

0 mA to 24 mA Internal RSET

4 mA to 20 mA Internal RSET

0 mA to 20 mA External RSET

0 mA to 24 mA External RSET

4 mA to 20 mA External RSET

-0.03

-0.06

0 mA to 20 mA External RSET

-0.12

0 mA to 24 mA External RSET

-0.09

4 mA to 20 mA External RSET

-0.12

-0.18

-40

-25

-10

5

20

35

50

65

Temperature (oC)

80

95

110

125

-40

-25

-10

5

20

35

50

65

Temperature (oC)

C006

Figure 68. IOUT FULL-SCALE ERROR vs TEMPERATURE

24

95

Temperature (oC)

C010

80

95

110

125

C003

Figure 69. IOUT OFFSET ERROR vs TEMPERATURE

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

2.00

AVDD = 10 V

AVSS = 0 V

RLOAD = 300

0.09

0.06

Gain Error (%FSR)

Compliance Headroom Voltage (V)

0.12

0.03

0.00

-0.03

0 mA to 20 mA Internal RSET

0 mA to 24 mA Internal RSET

4 mA to 20 mA Internal RSET

0 mA to 20 mA External RSET

0 mA to 24 mA External RSET

4 mA to 20 mA External RSET

-0.06

-0.09

-0.12

1.75

1.50

1.25

1.00

0.75

AVDD = 36 V

AVSS = 0 V

IOUT = 24 mA

RLOAD = 300

0.50

0.25

0.00

-40

-25

-10

5

20

35

50

65

80

95

110

Temperature (oC)

125

-40

-25

-10

5

Figure 70. IOUT GAIN ERROR vs TEMPERATURE

20

35

50

65

80

95

110

Temperature (oC)

C007

125

C004

Figure 71. COMPLIANCE HEADROOM VOLTAGE(1) vs

TEMPERATURE

30

DAC configured to deliver 24 mA

IOUT (4 mA/div)

AVDD = +24 V

AVSS = 0 V

25

LATCH (5 V/div)

IOUT (mA)

20

15

4 mA to 20 mA range

RLOAD = 300

10

AVDD = 36 V

AVSS = 0 V

RLOAD = 300

5

From code: 0000h

To code: FFFFh

0

0

1

2

3

4

5

Headroom Voltage (V)

Time (5 µs/div)

6

C001

C005

Figure 73. 4 mA to 20 mA RISING

Figure 72. IOUT vs COMPLIANCE HEADROOM VOLTAGE(1)

IOUT (4 mA/div)

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

AVDD = +24 V

AVSS = 0 V

IOUT (2 µA/div)

LATCH (5 V/div)

4 mA to 20 mA range

RLOAD = 300

From code:FFFFh

To code: 0000h

Time (5 µs/div)

Time (60 µs/div)

C001

Figure 74. 4 mA to 20 mA FALLING

(1)

C001

Figure 75. IOUT POWER-ON GLITCH

Compliance voltage headroom is defined as the drop from AVDD pin to the IOUT pin.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

25

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

At TA = +25°C, unless otherwise noted.

1.0

AVDD = 24 V

AVSS = 0 V

RLOAD = 250

AVDD = 24 V

AVSS = 0 V

RLOAD = 300

0.6

IOUT (mA)

8000h - 7FFFh

7FFFh - 8000h

IOUT (200 µA/div)

0.8

0.4

0.2

0.0

-0.2

Time (2 µs/div)

Time (2 µs/div)

C002

C001

Figure 76. IOUT OUTPUT ENABLE GLITCH

Figure 77. IOUT DIGITAL-TO-ANALOG GLITCH

AVDD = 24 V

AVSS = 0 V

AVDD = 24 V

AVSS = 0 V

1000

IOUT Noise (20 nA/div)

IOUT Noise PSD (nV/ sqrt-Hz)

1200

800

600

RLOAD = 300

All IOUT ranges

400

200

0 mA to 20 mA range

DAC = midscale

0

10

100

1k

10k

Time (4 s/div)

100k

Frequency (Hz)

C003

Figure 78. IOUT NOISE PSD vs FREQUENCY

C002

Figure 79. IOUT PEAK-TO-PEAK NOISE vs TIME (0.1 Hz to

10 Hz)

3.5

0

-20

IOUT PSRR (dB)

Leakage Current (nA)

2.5

2.0

1.5

1.0

0.5

-30

-40

RLOAD = 250

All IOUT ranges

-50

-60

-70

0.0

-80

-0.5

-90

0

4

8

12

16

20

24

IOUT Pin Voltage (V)

28

32

36

10

100

1k

10k

100k

Frequency (Hz)

C001

Figure 80. IOUT Hi-Z LEAKAGE CURRENT vs VOLTAGE

26

AVDD = 24 V

AVSS = 0 V

-10

AVDD = 36 V

AVSS = 0 V

Output disabled

3.0

1M

C002

Figure 81. IOUT PSRR vs FREQUENCY

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

THEORY OF OPERATION

DAC ARCHITECTURE

The DAC8760 and DAC7760 (DACx760) consist of a resistor-string digital-to-analog converter (DAC) followed by

a buffer amplifier. The output of the buffer drives the current output and the voltage output. The resistor-string

section is simply a string of resistors, each of value R, from REF to GND, as Figure 82 illustrates. This type of

architecture makes sure the DAC is monotonic. The 16-bit binary digital code (DAC8760) loaded to the DAC

register determines at which node on the string the voltage is tapped off before it is fed into the output amplifier.

To Current Output

To Voltage Output

Figure 82. DAC Structure: Resistor String

The current-output stage converts the voltage output from the string to current. The voltage output provides a

buffered output of the programmed range to the external load. When the current output or the voltage output is

disabled, it is in a high impedance (Hi-Z) state. After power-on, both output stages are disabled. Refer to the

CONTROLLING THE VOUT AND IOUT PINS section for different options to configure the current and voltage

output pins.

VOLTAGE OUTPUT STAGE

The voltage output stage as conceptualized in Figure 83 provides the voltage output according to the DAC code

and the output range setting. The output range can be programmed as 0 V to +5 V or 0 V to +10 V for unipolar

output mode, and ±5 V or ±10 V for bipolar output mode. In addition, an option is available to increase the output

voltage range by 10%. The output current drive can be up to 10 mA. The output stage has short-circuit current

protection that limits the output current to 30 mA. To maintain proper performance, a minimum 0.5-V powersupply headroom is required. The voltage output is able to drive a capacitive load up to 1 μF. For loads greater

than 20 nF, an external compensation capacitor can be connected between CMP and VOUT to keep the output

voltage stable at the expense of reduced bandwidth and increased settling time.

DACx760

12-/16-Bit

DAC

+

VOUT

í

RFB

+VSENSE

Range

Scaling

íVSENSE

Figure 83. Voltage Output

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

27

DAC7760

DAC8760

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

www.ti.com

The +VSENSE pin is provided to enable sensing of the load by connecting to points electrically closer to the

load. This configuration allows the internal output amplifier to make sure that the correct voltage is applied across

the load, as long as headroom is available on the power supply. Ideally, this pin is used to correct for resistive

drops on the system board and is connected to VOUT at the terminals. In some cases, both VOUT and

+VSENSE are brought out as terminals and, through seperate lines, connected remotely together at the load. In

such cases, if the +VSENSE line is cut, the amplifier loop is broken; use an optional 5-kΩ resistor between

VOUT and +VSENSE to prevent this from occurring. The –VSENSE pin, on the other hand, is provided as a

GND sense reference output from the internal VOUT amplifier. The output swing of the VOUT amplifier is relative

to the voltage seen at this pin. The actual voltage difference between the –VSENSE pin and the device GND

pins is not expected to be more than a few 100 µV. The internal resistor shown in Figure 83 between the device

internal GND and the –VSENSE pin is typically 2 kΩ.

After power on, the power-on-reset circuit makes sure that all registers are at their default values. Therefore, the

voltage output buffer is in a Hi-Z state; however, the +VSENSE pin connects to the amplifier inputs through an

internal 60-kΩ feedback resistor (RFB in Figure 83). If the VOUT and +VSENSE pins are connected together, the

VOUT pin is also connected to the same node through the feedback resistor. This node is protected by internal

circuitry and settles to a value between GND and the reference input.

The output voltage (VOUT) can be expressed as Equation 1 and Equation 2.

For unipolar output mode:

VOUT = VREF • GAIN •

CODE

2N

(1)

For bipolar output mode:

VOUT = VREF • GAIN •

CODE

N

2

- GAIN •

VREF

2

where

•

•

•

•

CODE is the decimal equivalent of the code loaded to the DAC.

N is the bits of resolution; 16 for DAC8760 and 12 for DAC7760.

VREF is the reference voltage; for internal reference, VREF = +5.0 V.

GAIN is automatically selected for a desired voltage output range as shown in Table 1.

(2)

Table 1. Voltage Output Range vs Gain Setting (1)

(1)

VOLTAGE OUTPUT RANGE

GAIN

0 V to +5 V

1

0 V to +10 V

2

±5 V

2

±10 V

4

VREF = +5.0 V

The voltage range is set according to the value of the RANGE bits and the OVR bit in the Control Register. The

OVR bit makes the gain value in Table 1 increase by 10%, thereby increasing the voltage output range, as

shown in Table 15. Refer to the SETTING VOLTAGE AND CURRENT OUTPUT RANGES section for more

details.

28

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: DAC7760 DAC8760

DAC7760

DAC8760

www.ti.com

SBAS528A – JUNE 2013 – REVISED DECEMBER 2013

CURRENT OUTPUT STAGE

The current output stage consists of a preconditioner and a current source as conceptualized in Figure 84. This

stage provides a current output according to the DAC code. The output range can be programmed as 0 mA to 20

mA, 0 mA to 24 mA, or 4 mA to 20 mA. An external boost transistor can be used to reduce the power dissipation

of the device. The maximum compliance voltage on pin IOUT equals (AVDD – 2 V). In single power-supply