* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download ECE1250F14_Lab6_Gates CMF

Oscilloscope history wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Index of electronics articles wikipedia , lookup

Electronic engineering wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power MOSFET wikipedia , lookup

Charlieplexing wikipedia , lookup

Integrated circuit wikipedia , lookup

Rectiverter wikipedia , lookup

Opto-isolator wikipedia , lookup

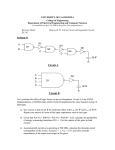

ECE 3300 Lab 2 ECE 1250 Lab 6 Name ________________________ Lab Section ___ Student Folder # ____ Digital Logic Gate Circuits Overview: In this Lab you will simulate and measure basic logic gates (NAND, XOR, NOT, OR) and design a control circuit for a 7-segment display display. This lab introduces digital logic gates that are the basis for computer circuits. You will learn about basic types of gates, and you will design a simple circuit for summing onedigit binary numbers. Logic gates will also be useful in your final project if you need to turn on an LED or motor when a certain combination of sensor inputs occurs, such as "the output of sensor 1 is low AND the output of sensor 2 is high." Equipment List: MyDAQ board with cables. (You can hook them to the lab computers if you don’t want to bring your laptop.) Multisim software. From previous labs: o Protoboard & wire kit o Resistor (1kΩ) o Red LED Additional parts: o Resistors: 1kΩ (2total), 1MΩ (two) o Red LED o Logic gate chips NAND 74HC00 and XOR 74HC86 For extra credit (c’mon, try them … these are fun and could be useful for your final project ….) o 7-segment display (common cathode or anode, but ask which it is) o 4- or 8- DIP switch o Additional NAND 74HC00 (2 total) o Resistors: 1kΩ (7 total) Safety Precautions: 1) Logic gate power supplies: The logic gates we will use (74HC00 and 74HC86) need a single +5 V power supply (available on the myDAQ). Using the wrong power supply voltage, reversing its polarity (such as plugging the chip in backwards) may burn out the logic gate chip and may also cause it to become extremely hot, smoke, or shatter. Make sure the notch or dot on the chip is at the top as shown in the circuit diagrams. Connect +5 V to pin 14 and 0V (dgnd) to pin 7. 2) Shorting gate outputs: One logic gate output can safely drive multiple logic gate inputs, which is known as fan-out. Logic gate outputs cannot be connected to other logic gate outputs. The latter situation would cause the logic gate outputs to fight one another. A logic gate may or may not survive having its outputs shorted together. 1 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Instructions & Reference Material: MyDAQ as voltmeter https://utah.instructure.com/courses/266578/assignments/1347122 Data Sheets: 74HC00 NAND gate: http://www.semicon.toshiba.co.jp/info/docget.jsp?type=datasheet&lang=en&pid=TC 74HC00AF 74HC86 XOR gate: http://www.toshiba.com/taec/components2/Datasheet_Sync/201206/DST_TC74HC86 AP-TDE_EN_421.pdf Prelab: Videos and Multisim 1. Review the videos and written material (see videos on website). 2. (Optional) You will be faster if you do the Multisim simulations before you come to lab. WRITE-UP: Take notes during the videos and record key information from reading assignments so you don’t have to go back and watch or review them again. Experiment 1: NAND gate operation (25 points) About the AGND and DGND grounds: The MyDAQ puts out +5 V and dgnd for powering digital circuits. These are on the opposite end from the ±15 V analog supplies. The only difference between the +5 V and the ±15 V supplies is the voltage. Note that the digital gnd is isolated from the analog gnd, however, so you would need to connect the gnd's together (connect them to the same rail on your breadboard, for instance) if you wanted to use the digital and analog supplies in the same circuit. Digital Voltages: For digital circuits, 0 V or dgnd represents a logical 0 (or FALSE/Low), and +5 V represents a logical 1 (or TRUE/High). Measure the +5V output from the MyDAQ to be sure it is working properly. Note: ‘digital’ and ‘logical’ are two equivalent words both describing this set of binary voltages. Digital NAND gate: We will start with a 74HC00 NAND chip. "NAND" stands for "not and." This means the gate outputs a 5V = digital “1” (or TRUE/High) if and only if it is not the case that both input A is a 1 (TRUE/High) and input B is a 1 (TRUE/High). Otherwise it outputs 0V = digital “0” (FALSE/Low). See the truth table in Figure 1. Each 74HC00 chip contains four NAND gates with various input (A,B) and output (Y) pins. 2 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Figure 1 74HC00 NAND logic gate pin out, truth table, and circuit diagram of a single NAND gate. A and B are inputs, Y is output. It is powered by Vcc=5V and Gnd. Fig. 2. Breadboard connections for NAND gate circuit. Note the red rail is +5V and blue is DGND. 3 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Simulate, Build, and Test the NAND gate circuit in Fig. 2: a) Simulate the circuit. Run the Multisim file for Fig. 2, available for download on the course website. Click on the switches to change the NAND gate inputs from 0 V to 5 V or vice versa. Switch the A and B inputs to either 0 V (gnd) or +5 V in all four possible combinations to verify the "truth table" by filling in the outputs you observe in Table I. Note that 0 V = logical (digital) “0” and +5 V = logical (digital) “1”. Observe the output voltage of the gate and translate it into 0 or 1. Table 1: NAND GATE TRUTH TABLE Input A (“0”=0V “1”=5V) 0 0 1 1 Input B Digital Output Y 0 1 0 1 1 1 1 0 Simulated Output Y (voltage) Measured Output Y (voltage) LED On/Off Note how VCC and Gnd for the NAND gate chip are specified behind the scenes in Multisim. When adding logic gate chips in Multisim, be careful to avoid redefining VCC, which might confuse Multisim. b) Power the Chip: Place the 74HC00 NAND chip on your breadboard as shown in Fig. 2. Note that the notch or dot should be at the top of the chip. Attach +5V from the MyDAQ to the red rail of the right of the breadboard, and DGND to the blue rail on he left, as shown. Then connect the +5V (red) rail to pin 14 of the chip and the DGND (blue) rail to pin 7. This power is required for the chip to function, so leave these two pins connected throughout the lab. c) Connect one of the NAND gates as shown in Fig. 2 and the right side of Figure 1. Verify the truth table in Table 1. Do this by manually connecting the A (pin1) and B (pin2) inputs to either 0 V (gnd) or +5 V in all four possible combinations in the table and measuring the output voltage (Y is on pin 3) with the MyDAQ voltmeter. Remember 0V=digital 0 and 5V= digital 1. d) Turn on an LED if TRUE: Connect a 1 kΩ resistor and LED in series from the NAND gate output (pin 3) to Gnd as shown in Figure 4. Note the polarity of the LED shown in Figure 3. The LED should be on when the output is “1” and off when it is “0” . Verify and record this in Table 1. Note for future reference. Digital circuits are not meant to drive large currents. This LED indicator requires only a few mA, but if you wanted to turn something on that required more current (such as a motor or fan), you would need to insert a buffer (which you will learn about in Lab 7) to isolate the digital circuit and also provide the current to drive the device. 4 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Figure 3 LED polarity. The anode (+) should be connected to the positive voltage, and cathode (-) to the ground. The cathode (-) is the shorter leg, and it also has a flat spot on the plastic cover of the LED. 1kΩ Figure 4 LED indicator for digital circuit. WRITEUP: Record your results in Table 1. Note any anomalous results. Experiment 2: XOR gate truth table (10 points) Repeat the experiment with a 74HC86 XOR gate. An XOR gate outputs a 1 (or TRUE) if input A is a 1 (or TRUE) or input B is a 1 (or TRUE) but not both (exclusivity). Figure 5 Pin diagram, truth table, and circuit diagram for the 74HC86 XOR gate Simulate, Build and Test the XOR gate circuit in Figure 5 and Fig. 6. Fill in the truth table below for the XOR gate by trying all possible combinations of input values (0 or 1) for inputs A and B. 5 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Table 2 XOR GATE TRUTH TABLE Input A Input B 0 0 1 1 0 1 0 1 Expected Output Y (digital 0/1) Simulated Measured LED Output Y Output Y On/Off (voltage) (voltage) Fig. 6. Breadboard connections for XOR gate circuit. Note the red rail is +5V and blue is DGND. WRITEUP: Record your results in 6 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Table 2. Note any anomalous results. Experiment 3: NOT gate and NAND gate (10 points) Digital gates are typically combined in order to control circuits in a myriad of ways such as in Fig. 7. Note that the first NAND gates acts like a NOT gate that simply inverts its input: 0 in gives 1 out, and vice versa. (So, is a NOT-NAND an AND?) Fig. 7. Not gate (made from a NAND with inputs tied together) and NAND gate combination circuit. Analyze (on paper) the circuit to figure out what the output at Y will be given the A and B input values. Fill in the expected column in Table 3. Build and test the circuit. Table 3 LOGIC CIRCUIT TRUTH TABLE Input A Input B 0 0 1 1 0 1 0 1 Expected Output Y (digital 0/1) Measured Output Y (voltage) WRITEUP: Record your results in Table 3. Note any anomalous results. Explain (1 sentence) what an AND gate does. Explain (1 sentence and a circuit diagram) what a NOT gate does and how to build one from a NAND gate. Why might you choose to build a NOT gate from a NAND rather than buying a NOT chip and using that? 7 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Experiment 4: DeMorgan's theorem (25 points) Build an OR gate from three NAND gates. An OR gate outputs a 1 when input A or input B is a 1. To do this, create two NOT gates from NANDS with their inputs tied together (as in Experiment 3). Use the NOT outputs as the inputs to yet another NAND gate. Show (on paper and in measurement) that you get an OR gate. Use one 74HC00 NAND chip for the three gates needed. Record the circuit schematic including pin numbers and truth table. Table 4 OR Gate TRUTH TABLE Input A Input B 0 0 1 1 0 1 0 1 Expected Output Y (digital 0/1) Measured Output Y (voltage) WRITEUP: Record your results in Table 4. Note any anomalous results. Explain (1 sentence) what an OR gate does. Show the circuit diagram for an OR gate made from 3 NAND gates (include pin numbers). 8 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Experiment 5: LED decoder (30 points) A 7-segment LED display is shown in Fig. 4. Logic gates are used to make display decoders (and everything else in a computer). The 74HCxx series of logic chips can directly drive an LED, so we can use the 74HC00 (or 74HC86) chips to build a decoder. The first step in the decoder design process is to make a truth table showing which segments should light up when displaying a given number. We consider a circuit, with three buttons, that displays a 0, 1, or 2, depending on which button is pressed. Table 5 shows the truth table for the circuit. Fig. 8 shows the logic for segments a, d, e, f, and g. Using only NAND gates, complete the design of the decoder. That is, design the circuitry to drive segments b, and c to match the truth table in Table 5. Fig. 8. 7-segment LED display segment labels. Table 5 LED DECODER TRUTH TABLE A 1 0 0 Inputs B 0 1 0 Display C 0 0 1 a 1 0 1 b 1 1 1 c 1 1 0 Outputs d 1 0 1 e 1 0 1 f 1 0 0 g 0 0 1 9 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Figure 9 7-segment LED display decoder partial schematic. WRITEUP: Fill in the schematic in Figure 9 so that it will give the 7-segment LED output in Table 5. 10 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu ECE 1250 LAB 3 Extra Credit: Build the complete 7-segment display circuit (15 points) Use your design from Experiment 5 to connect three (DIP) switches to a 7-segment display. You can get a 7-segment LED display from the stockroom. You can use either a common anode or common cathode display, but the pin outs are different, so be sure you know (or experiment to find out) which one you have. Figure 10 7-segment display pin outs and 8-DIP switch For the switches, you may purchase a DIP switch from the stockroom (see Figure 10). These typically come in 4- or 8-switch packages. You will only need 3 switches, so either of these will be fine. The switch acts like an open or a wire when closed. When the switch is closed, the input (A, B, or C) is connected to 5 V and is a “1”. When the switch is open, the input (A, B, or C) is pulled down to gnd by a 1MΩ resistor internal to the switch package and is a “0”. Experiment with your switch before connecting it to the 7-segment display. Note: If you might like to customize an output like the 7-segment display in the future, you can buy an amazing array of different color/shaped LEDs. See the stockroom and online. WRITEUP: Fill in the schematic in Figure 9 including pin numbers. If possible (optional) attach a photo of your circuit on the breadboard. Demonstrate that your circuit works (TA initials __________) Extra Credit: How to make a NOT gate (inverter) out of an XOR gate (5 points) Figure out how to use an XOR gate as a NOT gate. Hint: connect one input to a 0 or 1 (gnd or 5 V) power supply permanently. Draw, build, and test the circuit. Make a truth table. WRITEUP: Explain how to create a NOT gate from an XOR gate. Show the circuit diagram and truth table, including your measured results. Extra Credit: How to make an XOR gate from four NAND gates (10 points) Use four NAND gates to make an XOR gate. You can find the answer online, but this is a great puzzle to figure out on your own! Build the circuit and verify its truth table. WRITEUP: Show the circuit diagram and truth table, including your measured results. 11 UNIVERSITY OF UTAH DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 50 S. Central Campus Dr | Salt Lake City, UT 84112-9206 | Phone: (801) 581-6941 | Fax: (801) 581-5281 | www.ece.utah.edu