* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Homework 5 ECE 520.491 CAD VLSI Design of Digital Circuits

Survey

Document related concepts

Transcript

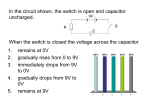

Homework 5 ECE 520.491 CAD VLSI Design of Digital Circuits P1. For a 2-input NOR gate, use the following device parameters for 0.5um process, calculate VLT, Tr, Tf for all output changing transitions (you can set λ=0). P2. Design a 2-input NOR gate in 180nm process. (a) Use the 180nm process, simulate the schematic of a 2-input NOR gate. Modify the W/L of the transistors in order to equalize the worst case rise and fall time. (b) Write a behavioral model for this gate. Include the worst case rise and fall times. Simulate this gate in Verilog. (c) Draw the layout of this gate. DRC and LVS your design. (d) Design the circuit to implement the following function: F = (A’B+C’D)E’. You can use any type of logic family. Simulate the design in SPICE, showing that the function is realized. Measure the worst case rise and fall times. What is the size of the circuit? What is the peak power consumption of the circuit.