* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download UNIT-III COMBINATIONAL AND SEQUENTIAL CIRCUIT DESIGN 1

Nanofluidic circuitry wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Invention of the integrated circuit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Flexible electronics wikipedia , lookup

Index of electronics articles wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Two-port network wikipedia , lookup

Radio transmitter design wikipedia , lookup

Power electronics wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

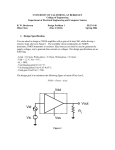

Valve RF amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power MOSFET wikipedia , lookup

Current mirror wikipedia , lookup

Opto-isolator wikipedia , lookup

Integrated circuit wikipedia , lookup

Rectiverter wikipedia , lookup

Digital electronics wikipedia , lookup

COMBINATIONAL AND SEQUENTIAL CIRCUIT DESIGN UNIT-III 1. What are most commonly used circuit families? The most commonly used circuit families are Static circuits Ratioed circuits Cascade voltage switch logic Dynamic circuits Pass transistor circuits. 2. What is bubble pushing? Normally AND and OR functions are expressed in terms of NAND and NOR. In manual circuit design, this is done through bubble pushing. A NAND gate is equivalent to an OR of inverted inputs. A NOR gate is equivalent to an AND of inverted inputs. Switching between these representations is easy to do on a whiteboard and is called bubble pushing. 3. What is outer input and inner input? The outer input is the input, closer to the supply rail. The inner input is the input, closer to the output. 4. what are asymmetric gates? When one input is far less critical than other, even nominal symmetric gates can be made asymmetric to support the late input at the expense of the early one. 5.what are normal, hi-skewed and lo skewed inverter? If βp/βn=1 then the inverter is called normal or unskewed inverter. If βp/βn>1 then the inverter is called hi-skewed inverter. All hi-skewed gates favour the rising output transition. If βp/βn<1 then the inverter is called lo-skewed inverter. All lo-skewed gates favour the falling output transition. 6. What is P/N ratios? The P/N ratios for logic gates i.e the ratio of pMOS to nMOS transistor width is equal to mobility ratio µp/µn. 7. What is the effect of reducing the pMOS size from 2 to 1.414? Delay improvement is 2%. This reduces the pMOS transient area. It also reduces input capacitance, which in turn reduces power consumption. Reduces noise margin. 8. What is multiple threshold voltages? Some CMOS process offer two or more threshold voltages. Transistors with lower threshold voltages produce more ON current,but increases leakage current. The low- threshold gates can be used to reduce the delay of critical paths. Skewed gates can use low-threshold devices on only the critical network of transistors. 9. What is ratioed circuits? If the transfer function of the circuit depends on the ratio of strength of the pulldown transistor to the pullup device then circuit is said to be ratioed. They use weak pull-up and strong pull-down devices. If pull-up is too strong,VOLMAX, may be too high. 10. what is Pseudo-nMOS? Pseudo-nMOS is a circuit in which the pull-down network is same that of a static gate,but the pull-up network has been replaced with a single pMOS transistor that is grounded so it is always ON. 11. What is ganged CMOS? A GANGED CMOS consists of two inverter ganged together. A B N1 P1 N2 P2 Y 0 0 OFF ON OFF ON 1 0 1 OFF ON OFF OFF ~0 1 0 ON OFF OFF ON ~0 1 1 ON OFF ON OFF 0 Table shows the pair that compute the NOR function. Such a circuit is called as SYMMETRIC NOR or GANGED CMOS. 12. What is CVSL? Cascade voltage switch logic (CVSL) seeks the performance of ratioed circuits without the static power consumption. It uses both true and complementary input signals and computes both true and complementary outputs using a pair of nMOS pull-down networks. 13. What are the features of CVSL? The logic is performed with nMOS transistors, thus reducing the input capacitance. Hence CVSL has a potential speed advantage. In pseudo nMOS the large size of pMOS transistor will slow the falling transition. But in CVSL,the feedback tends to turn off the pMOS so the outputs will eventually settle to a legal logic level. 14. What are the disadvantages of ratioed circuits? Ratioed circuits reduce the input capacitance by replacing the pMOS transistors connected to the inputs with a single pull-up resistor. Slow rising transitions. Contention on the falling transitions. Static power dissipation. Non-zero VOL. 15. What are dynamic circuits? Dynamic circuits are those circuits obtained by using a clocked pull-up transistor rather than a pMOS that is always ON. 16. What are two modes of dynamic circuits? Precharge mode Evaluation mode During precharge mode, the clock Ф is `0`,so the clocked pMOS is ON and initializes the output Y high. During evaluation mode, the clock Ф is `1`, and the clocked pMOS turns OFF. The output may remain high or may be discharged low through the pull-down network. 17. What are the advantages and disadvantages of dynamic circuits? Dynamic circuits are the fastest commonly used circuit family because they have lower input capacitance and no contention during switching. They also have zero static power dissipation. However, they require careful clocking, consume significant dynamic power, and are sensitive to noise during evaluation. Disadvantage of dynamic circuits They require careful clocking. Consume significant dynamic power sensitive to noise during evaluation Dynamic gates sharing same clock cannot be directly connected. 18. What is the foot? In dynamic inverter if the input is `1` during precharge, contension will take place because both pMOS and nMOS transistor will be ON.when the input cannot be guaranteed to be `0` during precharge,an extra clocked evaluation transistor can be added to the bottom of the nMOS stack to avoid contention.this extra transistor is called foot. 19. What is monotonicity? A fundamental difficulty with dynamic circuits is the monotonicity requirements.while a dynamic gate is in evaluation, the input must be monotonically rising. That is, the output can start LOW and remain LOW. start LOW and rise HIGH,start HIGH and remain HIGH, but not start HIGH and fall LOW. 20. How monotonicity problem can be solved? The monotonicity problem can be solved by placing a static CMOS inverter between dynamic gates. This converts the monotonically falling output into a monotonically rising signal suitable for the next gate. 21. What is domino gate? The dynamic-static pair together is called a domino gate, because precharge resembles setting up a chain of dominos and evaluation causes the gates to fire like dominos tipping over, each triggering the next. 22 What is dual-rail domino logic? Dynamic gates are inherently no inverting, while some functions like XOR gates necessarily require inversion. This problem is nullified by dual-rail domino logic. Dualrail domino gates encode signal with a pair of wires. The input and output signal pairs are encoded with _h and_l respectively. Dual-rail domino logic is also called as DCVSdynamic cascade voltage switch. Sig_h 0 0 1 1 Sig_l 0 1 0 1 MEANING PRECHARGED 0 1 INVALID 23. What are the advantage and disadvantage of dual-rail domino logic? Dual-rail domino logic is a complex logic family in that it can compute all inverting and non inverting logic functions. Dual-rail domino logic requires more area,wiring, and power. Dual-rail structures also lose the efficiency of wide dynamic NOR gate because they require complementary tall dynamic NAND stacks. 24. What is MODL? It is often necessary to compute multiple functions where one is a sub-function of another or shares a sub-function. Multiple-output domino logic (MODL) saves area by combining the entire computations multiple-output gate. The more compact design is called Manchester carry chain. 25. What is NP DOMINO? The hi-skew inverting static gates are replaced with precharged dynamic gates using pMOS logic. In a footed dynamic p-logic NOR gate when Ф is 0, the 1st and 3rd stages precharge high while the 2nd stage pre-discharges low. When Ф irises, all stages evaluate. This design style is called NP DOMINO or NORA domino. 26. What are the drawbacks of NORA? The logical effort of footed p-logic gates is generally worse than that of Hi-skew gates NORA is extreamly susceptible to noise. 27. What is zipper domino? Zipper domino is a technique that leaves the precharge transistors slightly ON during evaluation by using precharge clocks that swing between 0 and VDD -|Vtp| for the Pmos precharge and Vtn and VDD for the nMOS precharge. 28. What is threshold drop? A n-pass transistor attempting to pass a `1` never pull up the source above VDD-Vtn. 29. What is CPL? CPL is complementary pass transistor logic.CPL can be understood as an improvement on CVSL. 30. What is LEAP? LEAP builds logic network using fast nMOS transistors. It is a single-ended logic family in that the complementary network is not required, thus saving area and power. The output is buffered with an inverter, which can be LO-skewed to favour the asymmetric response of an nMOS transistor. 31. What is DPL? DPL is DOUBLE PASS TRANSISTOR LOGIC It is a double-rail form of CMOSTG where only know “0” or “1” needs to be passed. It is well high and low logic levels without the need for level-restoring devices. 32. What is EEPL? EEPL is ENERY ECONOMIZED PASS TRANSISTOR LOGIC Dual-rail family EEPL drives the cross coupled level restoring transistors from the opposite rail rather than VDD. 33. What is SRPL? SRPL is SWING-RESTORED PASS TRANSISTOR LOGIC (SRPL) It cross-coupled the inverters instead of using cross-coupled pMOS pull-ups. This tends to require small inverters, which make poor buffers. 34. What is DCVSPG? DCVSPG is Differential Cascode Voltage Switch with Pass Gate Logic It eliminates the output inverters from CPL. Without these buffers, the output of a DVSPG gate makes a poor input to the diffusion terminal of another DCVSPG gate. 35. What is PPL? PPL is Push-Pull Pass Transistor Logic. PPL also has unbuffered outputs and associated delay and noise issues. 36. What is DPTL? DPTL is Differential Pass Transistor Logic. DPTL generalizes the output buffer structure to consider alternatives to the crosscoupled pMOS transistors and LO-skewed inverters of CPL. 37. How Dynamic power can be reduced? Activity Factor reduction. Decreasing the supply voltage. Decreasing the Switching capacitance. 38. What circuit families are best for low power? Dynamic and seudo nMOS gates appear attractive because they eliminate the bulky pMOS transistor the account for 2/3 of the gate width in complementary CMOS logic. However, dynamic gates have a high activity factor that results in high dynamic power consumption. Pass transistor circuits have received much hype for their low power merits.