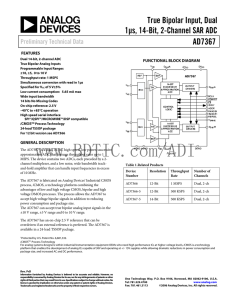

AD7367 数据手册DataSheet下载

... MSPS. The device contains two ADCs, each preceded by a 2channel multiplexer, and a low noise, wide bandwidth trackand-hold amplifier that can handle input frequencies in excess of 10 MHz. The AD7367 is fabricated on Analog Devices’ Industrial CMOS process, iCMOS, a technology platform combining the ...

... MSPS. The device contains two ADCs, each preceded by a 2channel multiplexer, and a low noise, wide bandwidth trackand-hold amplifier that can handle input frequencies in excess of 10 MHz. The AD7367 is fabricated on Analog Devices’ Industrial CMOS process, iCMOS, a technology platform combining the ...

DS90LV110T 1 to 10 LVDS Data/Clock Distributor General Description

... (Low Voltage Differential Signaling) technology for low power, high speed operation. Data paths are fully differential from input to output for low noise generation and low pulse width distortion. The design allows connection of 1 input to all 10 outputs. LVDS I/O enable high speed data transmission ...

... (Low Voltage Differential Signaling) technology for low power, high speed operation. Data paths are fully differential from input to output for low noise generation and low pulse width distortion. The design allows connection of 1 input to all 10 outputs. LVDS I/O enable high speed data transmission ...

Logic gates based on ion transistors Linköping University Post Print

... gate, the top 20 MΩ resistor may be replaced by a pnp-IBJT (Fig. 3b). In such complementary inverter the npn-IBJT is nonconductive for a high input while the pnp-IBJT is nonconductive for a low input signal. Together this minimizes the power consumption of the NOT gate and improves its output swing ...

... gate, the top 20 MΩ resistor may be replaced by a pnp-IBJT (Fig. 3b). In such complementary inverter the npn-IBJT is nonconductive for a high input while the pnp-IBJT is nonconductive for a low input signal. Together this minimizes the power consumption of the NOT gate and improves its output swing ...

PE4460 - Peregrine Semiconductor

... The serial programming interface consists of three CMOS compatible signals; input programming data (DATA), the serial bus clock (CLK) and a Latch Enable (EN) control line. A 32-bit data word is serially clocked LSB (B0) first into a control register on the leading edge of the serial bus clock and th ...

... The serial programming interface consists of three CMOS compatible signals; input programming data (DATA), the serial bus clock (CLK) and a Latch Enable (EN) control line. A 32-bit data word is serially clocked LSB (B0) first into a control register on the leading edge of the serial bus clock and th ...

CXP80732A/80740A

... The CXP80732A/80740A is a CMOS 8-bit microcomputer which consists of A/D converter, serial interface, timer/counter, time base timer, vector interruption, high precision timing pattern generation circuit, PWM generator, PWM for tuner, VISS/VASS circuit, 32kHz timer/event counter, remote control rece ...

... The CXP80732A/80740A is a CMOS 8-bit microcomputer which consists of A/D converter, serial interface, timer/counter, time base timer, vector interruption, high precision timing pattern generation circuit, PWM generator, PWM for tuner, VISS/VASS circuit, 32kHz timer/event counter, remote control rece ...

THE CASCODE AMPLIFIER: A common-gate (common

... to increase the dc gain while leaving the gain bandwidth product unchanged. In many applications the cascade amplifier is thought of and treated as a single-stage amplifier though it is formed by cascading two amplifier stages. The MOS Cascode Figure 20(a) shows the MOS cascode amplifier. Here trans ...

... to increase the dc gain while leaving the gain bandwidth product unchanged. In many applications the cascade amplifier is thought of and treated as a single-stage amplifier though it is formed by cascading two amplifier stages. The MOS Cascode Figure 20(a) shows the MOS cascode amplifier. Here trans ...

Avoiding Op Amp Instability Problems In Single-Supply Applications

... and C2, is equal to 1/[2π (RA/2) C2] = 32 Hz. Although this is an improvement on Figure 1, the common-mode rejection drops below 32 Hz, allowing substantial feedback through the power supply at low signal frequencies. This requires a larger capacitor to avoid “motorboating” and other manifestations ...

... and C2, is equal to 1/[2π (RA/2) C2] = 32 Hz. Although this is an improvement on Figure 1, the common-mode rejection drops below 32 Hz, allowing substantial feedback through the power supply at low signal frequencies. This requires a larger capacitor to avoid “motorboating” and other manifestations ...

AD421: Loop-Powered 4-20 mA DAC Data Sheet

... Output from the Voltage Regulator Loop. The DRIVE signal controls the external pass transistor to establish and maintain the correct VCC level programmed by the LV inputs while providing the necessary bias as the loop current is programmed from 4 mA to 20 mA. Compensation Capacitor Input. A capacito ...

... Output from the Voltage Regulator Loop. The DRIVE signal controls the external pass transistor to establish and maintain the correct VCC level programmed by the LV inputs while providing the necessary bias as the loop current is programmed from 4 mA to 20 mA. Compensation Capacitor Input. A capacito ...

HMC361S8G / 361S8GE

... [1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 ...

... [1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 ...

85-W 48-V Input Dual-Complimentary Output DC/DC Converter for

... Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been de ...

... Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been de ...

SMVD - INTEC Controls

... The SMVD consists of one of three full wave bridge rectifier for the 40, 80 and 120 Watt versions, 15V DC regulated supply, one opto-isolator and an amplifier section. The isolated input accepts a phase cut input (or milliamps when specified) and two non-isolated inputs accept 0-10V DC and 4-20mA. T ...

... The SMVD consists of one of three full wave bridge rectifier for the 40, 80 and 120 Watt versions, 15V DC regulated supply, one opto-isolator and an amplifier section. The isolated input accepts a phase cut input (or milliamps when specified) and two non-isolated inputs accept 0-10V DC and 4-20mA. T ...

Experiment1_EE391_F13

... OR gate. The input capacitance is the gate capacitance of the transistor. If we connect the output of one inverter to the input of a second inverter and measure how fast the first inverter switches, we should be able to determine the capacitance that is connected to that inverter. It’s as if we repl ...

... OR gate. The input capacitance is the gate capacitance of the transistor. If we connect the output of one inverter to the input of a second inverter and measure how fast the first inverter switches, we should be able to determine the capacitance that is connected to that inverter. It’s as if we repl ...

AN-376 Logic-System Design Techniques Reduce Switching-CMOS Power AN-

... Total system power dissipation is the sum of two components: static (or quiescent) and dynamic power. LS TTL systems consume such a great amount of quiescent power that the dynamic component pales into insignificance. When using MM74HC logic in power-critical applications, however, you must consider ...

... Total system power dissipation is the sum of two components: static (or quiescent) and dynamic power. LS TTL systems consume such a great amount of quiescent power that the dynamic component pales into insignificance. When using MM74HC logic in power-critical applications, however, you must consider ...

ADC0820 8-Bit High Speed MuP Compatible A/D Converter with

... Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions. Note 2: All voltages are measured with respect to the GND pin, unless otherwise specifie ...

... Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions. Note 2: All voltages are measured with respect to the GND pin, unless otherwise specifie ...

TLV571 数据资料 dataSheet 下载

... consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REFP and is at zero when the input signal is equal to or lower than REFM. sampling/conversion All sampling, conversion, and data output in the device are start ...

... consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REFP and is at zero when the input signal is equal to or lower than REFM. sampling/conversion All sampling, conversion, and data output in the device are start ...

+ collecting electrode

... A lot of work ongoing toward sparsification implemented at the pixel level (verilog simulation phase): test structures to test digital blocks of readout architecture will be implemented. ...

... A lot of work ongoing toward sparsification implemented at the pixel level (verilog simulation phase): test structures to test digital blocks of readout architecture will be implemented. ...

Lecture7 Integrated Circuits

... – IIH Maximum current that flows into the input in H state – IIL Maximum current that flows into the input in L state – IOH Maximum current that output can source in H state while maintaining output voltage of at least VOH – IOL Maximum current that output can sink in L state while maintaining outpu ...

... – IIH Maximum current that flows into the input in H state – IIL Maximum current that flows into the input in L state – IOH Maximum current that output can source in H state while maintaining output voltage of at least VOH – IOL Maximum current that output can sink in L state while maintaining outpu ...

MAX532 Dual, Serial-Input, Voltage-Output, 12-Bit MDAC _______________General Description

... 4 and 5). Both DACs are programmed by writing three 8-bit words (see Figures 2 and 3, and the Functional Diagram). Serial data is clocked into the data registers MSB first, with DACB information preceding DACA information. Data is clocked in on the rising edge of SCLK while CS is low. With CS high, ...

... 4 and 5). Both DACs are programmed by writing three 8-bit words (see Figures 2 and 3, and the Functional Diagram). Serial data is clocked into the data registers MSB first, with DACB information preceding DACA information. Data is clocked in on the rising edge of SCLK while CS is low. With CS high, ...

Owner`s Manual

... Please check the fuses , If they are blown, please replace with new one. Please check whether speakers work well, you can test speakers by connecting to another amplifier PROTECTION Please check overload, overheat ( thermal ), short and voltage, DC offset. Digital monoblock amplifiers ( APK-2500, AP ...

... Please check the fuses , If they are blown, please replace with new one. Please check whether speakers work well, you can test speakers by connecting to another amplifier PROTECTION Please check overload, overheat ( thermal ), short and voltage, DC offset. Digital monoblock amplifiers ( APK-2500, AP ...

MAX5354/MAX5355 10-Bit Voltage-Output DACs in 8-Pin µMAX __________________General Description

... The output amplifier’s inverting input is available to the user, allowing specific gain configurations, remote sensing, and high output current capability. This makes the MAX5354/MAX5355 ideal for a wide range of applications, including industrial process control. Other features include a software s ...

... The output amplifier’s inverting input is available to the user, allowing specific gain configurations, remote sensing, and high output current capability. This makes the MAX5354/MAX5355 ideal for a wide range of applications, including industrial process control. Other features include a software s ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.