IQ131+ Controller Data Sheet - wind

... The IQ131+ is normally supplied with the battery link fitted in the ON position. In this position the controller memory and internal clock are kept supplied in the event of supply failure. If this link is removed and pushed back onto one pin only, all memory contents (application strategy) are lost ...

... The IQ131+ is normally supplied with the battery link fitted in the ON position. In this position the controller memory and internal clock are kept supplied in the event of supply failure. If this link is removed and pushed back onto one pin only, all memory contents (application strategy) are lost ...

Third-Order ΣΑ Modulator with 61-dB SNR and 6-MHz

... OSR, there is a good correlation between two successive flash inputs. Therefore, it is more convenient to quantize (VO(n) – VO(n – 1)) than VO(n). This leads to the scheme of ...

... OSR, there is a good correlation between two successive flash inputs. Therefore, it is more convenient to quantize (VO(n) – VO(n – 1)) than VO(n). This leads to the scheme of ...

V350-35-T2 - PL Systems

... Do not force the board into place; doing so may damage the controller. 2. Replace the back cover of the controller and fasten the corner ...

... Do not force the board into place; doing so may damage the controller. 2. Replace the back cover of the controller and fasten the corner ...

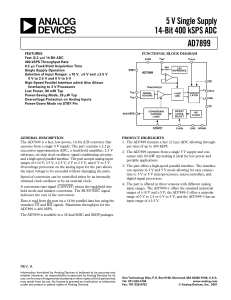

AD7899 5 V Single Supply 14-Bit 400 kSPS ADC

... The AD7899 is tested using two input frequencies. In this case, the second and third order terms are of different significance. The second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies ...

... The AD7899 is tested using two input frequencies. In this case, the second and third order terms are of different significance. The second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies ...

L6370

... deactivates itself. The following actions are taken: all the output stage is switched off; the signal DIAG2 is activated (active low). Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below Θlim-ΘH. The different thresholds with hystereti ...

... deactivates itself. The following actions are taken: all the output stage is switched off; the signal DIAG2 is activated (active low). Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below Θlim-ΘH. The different thresholds with hystereti ...

Zebra

... the DE0 40-pin header pinout doesn’t quite match up with the zebra’s pinout. For example, some of the DE0 pins are hard-wired to 5v, 3v, or ground, but the corresponding pins on zebra are supposed to be inputs controlling the motors or outputs from the quadrature encoders. A custom-made ribbon cable ...

... the DE0 40-pin header pinout doesn’t quite match up with the zebra’s pinout. For example, some of the DE0 pins are hard-wired to 5v, 3v, or ground, but the corresponding pins on zebra are supposed to be inputs controlling the motors or outputs from the quadrature encoders. A custom-made ribbon cable ...

DC/DC power module 12V/0.92A/11W

... • MTBF >10 million hours at +50°C case temperature • Low EMI ...

... • MTBF >10 million hours at +50°C case temperature • Low EMI ...

SLLIMM™- 2nd series IPM, 3-phase inverter, 20 A, 600 V short

... 2. The use of a bypass capacitor CVCC (aluminum or tantalum) can reduce the transient circuit demand on the power supply. Besides, to reduce high frequency switching noise distributed on the power lines, a decoupling capacitor C 2 (100 to 220 nF, with low ESR and low ESL) should be placed as close a ...

... 2. The use of a bypass capacitor CVCC (aluminum or tantalum) can reduce the transient circuit demand on the power supply. Besides, to reduce high frequency switching noise distributed on the power lines, a decoupling capacitor C 2 (100 to 220 nF, with low ESR and low ESL) should be placed as close a ...

document

... high level-active transparent latch (DLH X1, 16 transistors); ii) a positive-edge master-slave D flip-flop (DFF X1, 28 transistors); and iii) a custom sequential circuit (SEQ X1, 90 transistors). The first two circuits are an obvious choice since they are the most common sequential elements used in ...

... high level-active transparent latch (DLH X1, 16 transistors); ii) a positive-edge master-slave D flip-flop (DFF X1, 28 transistors); and iii) a custom sequential circuit (SEQ X1, 90 transistors). The first two circuits are an obvious choice since they are the most common sequential elements used in ...

Fast Frequency Acquisition Phase-Frequency Detectors for GSa/s

... dn signal. The effect appears as a negative output for phase differences higher than 2π – ∆ where ∆ = 2π ⋅ t reset ⁄ T cyc which depends on the reset path ...

... dn signal. The effect appears as a negative output for phase differences higher than 2π – ∆ where ∆ = 2π ⋅ t reset ⁄ T cyc which depends on the reset path ...

Features •

... Conversion to the ATU18 series of ULC provides a significant reduction of the operating power when compared to the original PLD or FPGA. The ATU18 series has a very low standby consumption, less than 0.145 nA/gate typically at commercial temperature. Operating consumption is a strict function of clo ...

... Conversion to the ATU18 series of ULC provides a significant reduction of the operating power when compared to the original PLD or FPGA. The ATU18 series has a very low standby consumption, less than 0.145 nA/gate typically at commercial temperature. Operating consumption is a strict function of clo ...

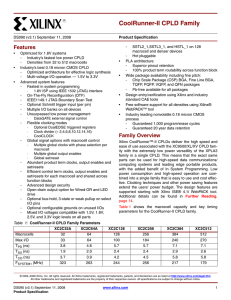

CoolRunner-II CPLD Family Data Sheet

... CPLD architecture combining macrocells into Function Blocks (FBs) interconnected with a global routing matrix, the Xilinx Advanced Interconnect Matrix (AIM). The FBs use a Programmable Logic Array (PLA) configuration which allows all product terms to be routed and shared among any of the macrocells ...

... CPLD architecture combining macrocells into Function Blocks (FBs) interconnected with a global routing matrix, the Xilinx Advanced Interconnect Matrix (AIM). The FBs use a Programmable Logic Array (PLA) configuration which allows all product terms to be routed and shared among any of the macrocells ...

78Q8392L/A03 Low Power Ethernet Coaxial Transceiver

... detected and compared to a set level in the receiver comparator circuit. The pulse width must be greater than 20 ns to pass the narrow pulse filter; the transition timer outputs a true level on the RX Data Valid line provided the time between transitions is less than about 200 ns. As long as a valid ...

... detected and compared to a set level in the receiver comparator circuit. The pulse width must be greater than 20 ns to pass the narrow pulse filter; the transition timer outputs a true level on the RX Data Valid line provided the time between transitions is less than about 200 ns. As long as a valid ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.

![PDF [FULL TEXT]](http://s1.studyres.com/store/data/015018175_1-0620b69520c9bf1d46146ee7338be05c-300x300.png)