a CMOS 80 MHz Monolithic 256 24(18) Color Palette RAM

... When accessing the color palette RAM, the address register resets to 00H following a blue read or write cycle to RAM location FFH. When accessing the overlay color registers, the address register increments following a blue read or write cycle. However, while accessing the overlay color registers, t ...

... When accessing the color palette RAM, the address register resets to 00H following a blue read or write cycle to RAM location FFH. When accessing the overlay color registers, the address register increments following a blue read or write cycle. However, while accessing the overlay color registers, t ...

www.rotalink.com

... to improve noise immunity compared to a standard single ended signal. This benefit is derived from the fact that external electromagnetic interference (EMI) tends to affect wires equally. Using a single ended signal, noise could cause a 0V signal to be raised to a 5V signal. With a dual ended signal ...

... to improve noise immunity compared to a standard single ended signal. This benefit is derived from the fact that external electromagnetic interference (EMI) tends to affect wires equally. Using a single ended signal, noise could cause a 0V signal to be raised to a 5V signal. With a dual ended signal ...

LS7538-LS7539

... with each side of the metal ring connected back to opposite sides of the AC line. This ensures that a path for the spark back to house ground through AC Neutral exists independent of line plug polarity. The split ring and the center conduction plate should be constructed so that the spacing between ...

... with each side of the metal ring connected back to opposite sides of the AC line. This ensures that a path for the spark back to house ground through AC Neutral exists independent of line plug polarity. The split ring and the center conduction plate should be constructed so that the spacing between ...

new dsmreport2

... whether the input is greater than half the reference voltage. If it is, the most significant bit (MSB) of the output is set. This value is then subtracted from the input, and the result is checked for one quarter of the reference voltage. This process continues until all the output bits have been se ...

... whether the input is greater than half the reference voltage. If it is, the most significant bit (MSB) of the output is set. This value is then subtracted from the input, and the result is checked for one quarter of the reference voltage. This process continues until all the output bits have been se ...

General Specifications MODEL UM331 Digital Indicator with Alarms

... • Extra-large digital display allows the indicated values to be read even from a long distance. LEDs of 20 mm height are used for the PV display. • The PV display color changing function "Active Color PV Display" is provided. PV display color is changed from green to red and vice versa when an alarm ...

... • Extra-large digital display allows the indicated values to be read even from a long distance. LEDs of 20 mm height are used for the PV display. • The PV display color changing function "Active Color PV Display" is provided. PV display color is changed from green to red and vice versa when an alarm ...

Fuji Electric PXR3 Temperature Controller Brochure

... Alarm latch function provided Delay setting 0 to 9999 sec settable in 1 sec steps Alarm ON-delay Process alarm output Relay contact: SPST contact: 220 V AC/30 V DC, ...

... Alarm latch function provided Delay setting 0 to 9999 sec settable in 1 sec steps Alarm ON-delay Process alarm output Relay contact: SPST contact: 220 V AC/30 V DC, ...

Chapter 2 - Part 1 - PPT - Mano & Kime

... • Primitive gate - a gate that can be described using a single primitive operation type (AND or OR) plus an optional inversion(s). • Complex gate - a gate that requires more than one primitive operation type for its description ...

... • Primitive gate - a gate that can be described using a single primitive operation type (AND or OR) plus an optional inversion(s). • Complex gate - a gate that requires more than one primitive operation type for its description ...

Chapter 2 Combinational Logic Circuits (Part III)

... • Primitive gate - a gate that can be described using a single primitive operation type (AND or OR) plus an optional inversion(s). • Complex gate - a gate that requires more than one primitive operation type for its description ...

... • Primitive gate - a gate that can be described using a single primitive operation type (AND or OR) plus an optional inversion(s). • Complex gate - a gate that requires more than one primitive operation type for its description ...

Hello, and welcome to this presentation of the STM32 general

... locked by applying the correct write sequence to the lock register, the I/O pin’s configuration cannot be modified until the next reset. ...

... locked by applying the correct write sequence to the lock register, the I/O pin’s configuration cannot be modified until the next reset. ...

Crown Service Web Site

... respect to ground, but ±Vcc remain constant with respect to each other. This allows the power supply to deliver +Vcc and -Vcc from the same bridge rectifier and filter as a total difference in potential, regardless of their voltages with respect to ground. The LS uses inverted feedback from the HS o ...

... respect to ground, but ±Vcc remain constant with respect to each other. This allows the power supply to deliver +Vcc and -Vcc from the same bridge rectifier and filter as a total difference in potential, regardless of their voltages with respect to ground. The LS uses inverted feedback from the HS o ...

A new system of digital circuit blocks for industrial

... different functions required. Sometimes special blocks are provided for this purpose, while sometimes these circuits are built up from two NOR or NAND blocks [41 [51. The bistable circuit (flip-flop) consisting of the two types of active block is shown in jig. 4a for the asynchronous counting mode a ...

... different functions required. Sometimes special blocks are provided for this purpose, while sometimes these circuits are built up from two NOR or NAND blocks [41 [51. The bistable circuit (flip-flop) consisting of the two types of active block is shown in jig. 4a for the asynchronous counting mode a ...

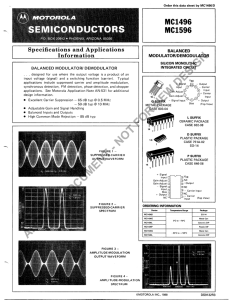

MC1496 MC1596 Specifications and Applications

... TA = + 25°C unless otherwise noted) (All input and output char ...

... TA = + 25°C unless otherwise noted) (All input and output char ...

$doc.title

... Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at th ...

... Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at th ...

File

... In the common-base configuration, the input signal is applied to the emitter, the output is taken from the collector, and the base is the element common to both input and output. Since the input is applied to the emitter, it causes the emitter-base junction to react in the same manner as it did in ...

... In the common-base configuration, the input signal is applied to the emitter, the output is taken from the collector, and the base is the element common to both input and output. Since the input is applied to the emitter, it causes the emitter-base junction to react in the same manner as it did in ...

Analog Devices Welcomes Hittite Microwave Corporation

... [1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 ...

... [1] Reference this number when ordering complete evaluation PCB [2] Circuit Board Material: Rogers 4350 ...

CMOS Schmitt Trigger—A Uniquely Versatile Design Component

... When the input is at 0V, transistors P1 and P2 are ON, and N1, N2 and P3 are OFF. Since out' is high, N3 is ON and acting as a source follower, the drain of N1, which is the source of N2, is at VCC − VTH. If the input voltage is ramped up to one threshold above ground transistor N1 begins to turn ON ...

... When the input is at 0V, transistors P1 and P2 are ON, and N1, N2 and P3 are OFF. Since out' is high, N3 is ON and acting as a source follower, the drain of N1, which is the source of N2, is at VCC − VTH. If the input voltage is ramped up to one threshold above ground transistor N1 begins to turn ON ...

MANLEY - Barry Rudolph

... Typically the release with these is slow to prevent audible damage to the mix. With this unit you can adjust the attack, release and even the overload point in musical ways. Distortion can be creatively used by turning up the INPUT and turning down the OUTPUTs while using very little or no COMPRESSI ...

... Typically the release with these is slow to prevent audible damage to the mix. With this unit you can adjust the attack, release and even the overload point in musical ways. Distortion can be creatively used by turning up the INPUT and turning down the OUTPUTs while using very little or no COMPRESSI ...

PAC3000S12-CE PSU Technical Manual V1.1 90 V AC - 264 V AC

... a latch off mode. Output overcurrent shall be maintained for a period of 1s before the PSU enter a latch off mode. The latch can be cleared by toggling the PSON signal or by an AC input recycle. The delay time from PSON high to PSON low should be more than 1 s. The delay time from AC off to AC on sh ...

... a latch off mode. Output overcurrent shall be maintained for a period of 1s before the PSU enter a latch off mode. The latch can be cleared by toggling the PSON signal or by an AC input recycle. The delay time from PSON high to PSON low should be more than 1 s. The delay time from AC off to AC on sh ...

ICS9DB202.pdf

... In these systems, a jitter-attenuating device may be necessary in order to reduce high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The ICS9DB202 has two PLL bandwidth modes. In low bandwidth mode, the PLL loop bandwidth is 500kHz. This set ...

... In these systems, a jitter-attenuating device may be necessary in order to reduce high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The ICS9DB202 has two PLL bandwidth modes. In low bandwidth mode, the PLL loop bandwidth is 500kHz. This set ...

CD54HC174 数据资料 dataSheet 下载

... A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements is transferred to the outputs on the positive-going edge of the clock p ...

... A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements is transferred to the outputs on the positive-going edge of the clock p ...

2 LXY28161 Specification

... 4.1 The Rt value should satisfy: Rt < ( Rf / N /9), besides, set the value as small as possible. Otherwise, there will be current difference between ICs, which will effect the color uniformity. ...

... 4.1 The Rt value should satisfy: Rt < ( Rf / N /9), besides, set the value as small as possible. Otherwise, there will be current difference between ICs, which will effect the color uniformity. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.