Yogi`s Report

... Figure 7: Two distinct flow patterns representing the states of the flip flop [6] 2.5 Bubble logic: Prakash and Gershenfeld from MIT have implemented logic gates like AND, OR and NOT using bubble logic in microfluidic channels [7]. The functioning of the devices is based on bubbles traveling in micr ...

... Figure 7: Two distinct flow patterns representing the states of the flip flop [6] 2.5 Bubble logic: Prakash and Gershenfeld from MIT have implemented logic gates like AND, OR and NOT using bubble logic in microfluidic channels [7]. The functioning of the devices is based on bubbles traveling in micr ...

AD7650 数据手册DataSheet下载

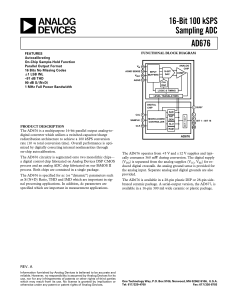

... When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7650 provides the conversion result, M ...

... When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7650 provides the conversion result, M ...

Chapter 4 – Typical application circuits

... Capacitors of 10 μF (47 μF) and 0.1 μF, which are connected to each power supply unit shown in typical application circuits are not used for smoothing the output voltage of the control power supply units but are used for reduction of the wiring impedance from the power supply unit to the IPM. Additi ...

... Capacitors of 10 μF (47 μF) and 0.1 μF, which are connected to each power supply unit shown in typical application circuits are not used for smoothing the output voltage of the control power supply units but are used for reduction of the wiring impedance from the power supply unit to the IPM. Additi ...

Lab report of ETE 02

... 3. A full adder was designed using NAND and XOR gates (Fig 1). The full adder was then converted into a full subtractor by complementing one of the inputs and adding a NOT gate (using a NAND gate) to the difference output (Fig 2). Next a selectable two-bit adder/subtractor was designed. This is crea ...

... 3. A full adder was designed using NAND and XOR gates (Fig 1). The full adder was then converted into a full subtractor by complementing one of the inputs and adding a NOT gate (using a NAND gate) to the difference output (Fig 2). Next a selectable two-bit adder/subtractor was designed. This is crea ...

ADC14C105 14-Bit, 95/105 MSPS A/D Converter (Rev. C)

... All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified. Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is specified to be functional, but do not ensure specific pe ...

... All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified. Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is specified to be functional, but do not ensure specific pe ...

+3 V/+5 V, Dual, Serial Input 12-Bit DAC AD7394

... DAC A Voltage Output. DAC Reference Voltage Input Terminal. Establishes DAC full-scale output voltage. Pin can be tied to VDD pin. Digital Ground. Should be tied to analog GND. Chip Select, Active Low Input. Disables shift register loading when high. Does not affect LDA or LDB operation. Clock Input ...

... DAC A Voltage Output. DAC Reference Voltage Input Terminal. Establishes DAC full-scale output voltage. Pin can be tied to VDD pin. Digital Ground. Should be tied to analog GND. Chip Select, Active Low Input. Disables shift register loading when high. Does not affect LDA or LDB operation. Clock Input ...

IDT8P34S1102I Final Data Sheet.fm

... adjusted to position the V1in the center of the input voltage swing. For example, if the input clock swing is 1.8V and VDD = 1.8V, R1 and R2 value should be adjusted to set V1 at 0.9V. The values below are for when both the single ended swing and VDD are at the same voltage. This configuration requi ...

... adjusted to position the V1in the center of the input voltage swing. For example, if the input clock swing is 1.8V and VDD = 1.8V, R1 and R2 value should be adjusted to set V1 at 0.9V. The values below are for when both the single ended swing and VDD are at the same voltage. This configuration requi ...

AD7191 数据手册DataSheet下载

... These numbers are measured with the load circuit shown in Figure 2 and defined as the time required for the output to cross the VOL or VOH limits. ...

... These numbers are measured with the load circuit shown in Figure 2 and defined as the time required for the output to cross the VOL or VOH limits. ...

THS1215 数据资料 dataSheet 下载

... No matter what operating configuration is chosen, VP is digitized against ADC reference voltages VREFT and VREFB. The VREFT and VREFB voltages set the analog input span limits FS+ and FS–, respectively. Any voltages at AIN greater than REFT or less than REFB causes ADC over-range, which is signaled ...

... No matter what operating configuration is chosen, VP is digitized against ADC reference voltages VREFT and VREFB. The VREFT and VREFB voltages set the analog input span limits FS+ and FS–, respectively. Any voltages at AIN greater than REFT or less than REFB causes ADC over-range, which is signaled ...

STK5F4U3E2D-E - ON Semiconductor

... ssterminal so that it does not flow to the power side the GND signal current. (3) The power GND side and the control GND side a point of connection, GND wiring, pleas e be as short as possible. (4) Snubber capacitor between the positive terminal and the ...

... ssterminal so that it does not flow to the power side the GND signal current. (3) The power GND side and the control GND side a point of connection, GND wiring, pleas e be as short as possible. (4) Snubber capacitor between the positive terminal and the ...

DSi200 Stereo Integrated Amplifiers

... necessary for best sonics; generally, a half-hour to 45 minutes of actual playing time will bring the amplifier around to more than acceptable performance levels, with some additional improvement noticeable over the next hour or two. Warm-up characteristics will depend upon ambient room temperature ...

... necessary for best sonics; generally, a half-hour to 45 minutes of actual playing time will bring the amplifier around to more than acceptable performance levels, with some additional improvement noticeable over the next hour or two. Warm-up characteristics will depend upon ambient room temperature ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.