* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lab report of ETE 02

Phase-locked loop wikipedia , lookup

Electronic engineering wikipedia , lookup

Index of electronics articles wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Integrated circuit wikipedia , lookup

Regenerative circuit wikipedia , lookup

Radio transmitter design wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Integrating ADC wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Digital electronics wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

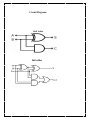

Course Name: Digital Electronics LAB Course Code: ETE 205 Experiment No: 03 Group: 03 Topic of the Experiment: Adder and subtractor. Submitted to: Sajib Roy Lecturer Department of Electronics & Telecommunication Engineering University of Liberal Arts Bangladesh Submitted By: Md.Najim uddin Department of Computer Science Engineering ID:131014001 Date of Submission:22/06/2014 Objective: To study the adder and subtractor circuit using logic gates. Introduction: The half adder is a dual input, dual output logic circuit that adds two binary bits and gives the sum of these bits and a carry. The full adder combines two half adders taking the OR of their carries with the sum of the second being used as the output. The subtraction of two binary numbers can be done by taking the 2’s complement of the subtrahend and adding it to the minuend. The 2’s complement can be obtained by taking the 1’s complement and adding Equipments: 7486 quad 2-input XOR gates 7400 quad 2-input NAND gates 7404 Hex inverter 7408 Quadruple 2 input AND gates Trainer Board LEDs Wires. Procedure: 1. Design a 2 bit half adder and a 2 bit full adder. The half adder will have two binary inputs, a sum output and a carry output. The full adder will have two binary inputs, a carry input, a sum output and a carry output. Use a voltmeter to confirm that the power supply voltage is 5 volts. To evaluate the performance of your adders you will need a means to provide the inputs and read the outputs. Either use the LED indicators on the digital designer or add LED's and current-limiting resistors to make the outputs observable. Use either the slide switches on your digital designer or the power supply voltage and ground to provide the required logical inputs. 2. Test the adders to be sure they function correctly (i.e., verify the truth for the half adder and the full adder). 3. A full adder was designed using NAND and XOR gates (Fig 1). The full adder was then converted into a full subtractor by complementing one of the inputs and adding a NOT gate (using a NAND gate) to the difference output (Fig 2). Next a selectable two-bit adder/subtractor was designed. This is created using a half adder/subtractor for the lower bit and then applying the carry/borrow output from the half adder/subtractor to the carry/borrow input of the full adder/subtractor used for the higher bit (Fig 3). A Fifth “select” input determined if the circuit was running in add or subtract mode. The select input was connected using XOR gates to the two inputs that needed to be complemented for the circuit to subtract correctly. The XOR gates acted as programmable inverters in this case. Result: Half Adder: S=A B C=A.B Full Adder: S=A B Cin Cout=A.B+B.Cin+A.Cin Half Subtractor: D=Y X B=X.Y Full Subtractor: D=X Y Z B=Z.(X Y)+X.Y Circuit Diagram: Half Adder Full adder Half Subtractor Full Subtractor Conclusion: The truth table generated from testing the adder/subtractor circuit is identical to the truth table generated in the Preliminary Work, therefore the design presented has been validated. No problems occurred and no design modifications were required. Reference: http://www.scribd.com/doc/93673825/Logic-Org-Exp-1-7 http://graphics5.net/f/fundamentals-of-computer-engineering-file-egr270samplelab-labe1753-pdf.pdf http://www.learningace.com/doc/10903/0c6fb040e5089778e00f759e42f3de7f/egr270sam plelab