DC115A - Demo Manual

... is activated by a falling-edge-triggered STROBE signal on Pin 2 of JP1. This STROBE pin is loaded by a 5.1k pull-up resistor to VCC. Be sure to set the SELECT switch to the ON position for noncontinuous mode. If SELECT is still active, changing any bit on JP1 creates an instant change to the continu ...

... is activated by a falling-edge-triggered STROBE signal on Pin 2 of JP1. This STROBE pin is loaded by a 5.1k pull-up resistor to VCC. Be sure to set the SELECT switch to the ON position for noncontinuous mode. If SELECT is still active, changing any bit on JP1 creates an instant change to the continu ...

PCM185x: 24-Bit 96-kHx Stereo A/D Converter w/6 x 2

... analog front end that consists of a 6-stereo-input multiplexer and wide-range PGA. The PCM1850/1851 includes a delta-sigma modulator with 64-times oversampling, a digital decimation filter and a low-cut filter that removes the dc component of the input signal. For various applications, the PCM1850/1 ...

... analog front end that consists of a 6-stereo-input multiplexer and wide-range PGA. The PCM1850/1851 includes a delta-sigma modulator with 64-times oversampling, a digital decimation filter and a low-cut filter that removes the dc component of the input signal. For various applications, the PCM1850/1 ...

FEATURES PIN ASSIGNMENT

... signal input is low. Communication with the DS1868B requires the transition of the RST input from a low state to a high state. Once the 3-wire port has been activated, data is entered into the part on the low to high transition of the CLK signal inputs. Three-wire serial timing requirements are prov ...

... signal input is low. Communication with the DS1868B requires the transition of the RST input from a low state to a high state. Once the 3-wire port has been activated, data is entered into the part on the low to high transition of the CLK signal inputs. Three-wire serial timing requirements are prov ...

MAX9181 Low-Jitter, Low-Noise LVPECL-to-LVDS Level Translator in an SC70 Package General Description

... a single LVDS output. It is ideal for interfacing between LVPECL and LVDS interfaces in systems that require minimum jitter, noise, power, and space. Ultra-low, 23ps P-P added deterministic jitter and 0.6psRMS added random jitter ensure reliable communication in high-speed links that are highly sens ...

... a single LVDS output. It is ideal for interfacing between LVPECL and LVDS interfaces in systems that require minimum jitter, noise, power, and space. Ultra-low, 23ps P-P added deterministic jitter and 0.6psRMS added random jitter ensure reliable communication in high-speed links that are highly sens ...

AD9708 数据手册DataSheet 下载

... current IREF, which is nominally set by a reference voltage VREFIO and external resistor RSET. It can be expressed as: ...

... current IREF, which is nominally set by a reference voltage VREFIO and external resistor RSET. It can be expressed as: ...

ADM222 数据手册DataSheet 下载

... *This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability. ...

... *This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability. ...

2-555 Timer-Rev2p1

... Pin 7 is discharge. Connects to ground when output goes low. Pins 2, 6 and 7 control the timing. 2 and 7 are often connected to a resistor and capacitor combination for this purpose ...

... Pin 7 is discharge. Connects to ground when output goes low. Pins 2, 6 and 7 control the timing. 2 and 7 are often connected to a resistor and capacitor combination for this purpose ...

18-Bit, 2.5 LSB INL, 100 kSPS SAR ADC AD7678 FUNCTIONAL BLOCK DIAGRAM

... In all modes except MODE = 3, this output is used as Bit 10 of the parallel port data output bus. When MODE = 3 (serial mode), this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7678 provides the con ...

... In all modes except MODE = 3, this output is used as Bit 10 of the parallel port data output bus. When MODE = 3 (serial mode), this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7678 provides the con ...

MAX9424–MAX9427 Lowest Jitter Quad PECL-to-ECL Differential Translators General Description

... The MAX9424–MAX9427 high-speed, low-skew quad PECL-to-ECL translators are designed for high-speed data and clock driver applications. These devices feature an ultra-low 0.24ps(RMS) random jitter and channel-tochannel skew is less than 90ps in asynchronous mode. The four channels can be operated sync ...

... The MAX9424–MAX9427 high-speed, low-skew quad PECL-to-ECL translators are designed for high-speed data and clock driver applications. These devices feature an ultra-low 0.24ps(RMS) random jitter and channel-tochannel skew is less than 90ps in asynchronous mode. The four channels can be operated sync ...

555 Timer - Electro Tech Online

... Pin 7 is discharge. Connects to ground when output goes low. Pins 2, 6 and 7 control the timing. 2 and 7 are often connected to a resistor and capacitor combination for this purpose ...

... Pin 7 is discharge. Connects to ground when output goes low. Pins 2, 6 and 7 control the timing. 2 and 7 are often connected to a resistor and capacitor combination for this purpose ...

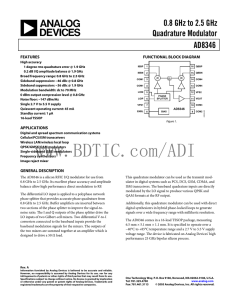

AD8346 数据手册DataSheet 下载

... local 100 pF and 0.01 μF capacitors. Enable Pin. A high level enables the device; a low level puts the device in sleep mode. Ground Pin for the input stage of output amplifier. Ground Pin for the output stage of output amplifier. 50 Ω DC-Coupled RF Output. User must provide ac coupling on this pin. ...

... local 100 pF and 0.01 μF capacitors. Enable Pin. A high level enables the device; a low level puts the device in sleep mode. Ground Pin for the input stage of output amplifier. Ground Pin for the output stage of output amplifier. 50 Ω DC-Coupled RF Output. User must provide ac coupling on this pin. ...

FLASH (SIMULTANEOUS ) ADC CONVERTER (1)…

... A dual slope ADC is common in digital voltmeters and other type of measurement instruments. A block diagram of dual slope ADC is shown in fig 7. ...

... A dual slope ADC is common in digital voltmeters and other type of measurement instruments. A block diagram of dual slope ADC is shown in fig 7. ...

POWERWARE 9315 300

... Designed for Inherent Reliability ✔Fundamental design with no compromises. ✔Minimised component count – only 4 PCB control boards. ✔Modular design – low MTTR. ✔Prioritised cooling – printed circuit boards…power processing…magnetics. ✔Static switch features electrical quick disconnects - assembly is ...

... Designed for Inherent Reliability ✔Fundamental design with no compromises. ✔Minimised component count – only 4 PCB control boards. ✔Modular design – low MTTR. ✔Prioritised cooling – printed circuit boards…power processing…magnetics. ✔Static switch features electrical quick disconnects - assembly is ...

DS1110L 3V 10-Tap Silicon Delay Line General Description Features

... All voltages are referenced to ground. Measured with outputs open. Initial tolerances are ± with respect to the nominal value at +25°C and VCC = 3.3V for both leading and trailing edges. Temperature and voltage tolerances are with respect to the nominal delay value over stated temperature range and ...

... All voltages are referenced to ground. Measured with outputs open. Initial tolerances are ± with respect to the nominal value at +25°C and VCC = 3.3V for both leading and trailing edges. Temperature and voltage tolerances are with respect to the nominal delay value over stated temperature range and ...

Feasibility study

... behavior there is no circuit with input impedance that matches to the function W() for all frequencies. The characteristic impedance goes to the value of 300Ohm at high frequencies, so resistive part of the electronic input impedance must go to the value as well. A serial capacitor in front of it d ...

... behavior there is no circuit with input impedance that matches to the function W() for all frequencies. The characteristic impedance goes to the value of 300Ohm at high frequencies, so resistive part of the electronic input impedance must go to the value as well. A serial capacitor in front of it d ...

MAX5400/MAX5401 256-Tap SOT-PoT, Low-Drift Digital Potentiometers in SOT23 General Description

... in series between pins H and L. The potentiometer wiper (pin W) can be programmed to access any one of the 256 different tap points on the resistor string. The MAX5400/MAX5401 uses a 3-wire serial data interface to control the wiper tap position. This write-only interface contains three inputs: Chip ...

... in series between pins H and L. The potentiometer wiper (pin W) can be programmed to access any one of the 256 different tap points on the resistor string. The MAX5400/MAX5401 uses a 3-wire serial data interface to control the wiper tap position. This write-only interface contains three inputs: Chip ...

LT5520 - 1.3GHz to 2.3GHz High Linearity Upconverting Mixer.

... The IF inputs are connected to the emitters of the doublebalanced mixer transistors, as shown in Figure 3. These pins are internally biased and an external resistor must be connected from each IF pin to ground to set the current through the mixer core. The circuit has been optimized to work with 100 ...

... The IF inputs are connected to the emitters of the doublebalanced mixer transistors, as shown in Figure 3. These pins are internally biased and an external resistor must be connected from each IF pin to ground to set the current through the mixer core. The circuit has been optimized to work with 100 ...

KTA-249 UV Solar and Anemometer Modbus Interface

... The Davis Anemometer measures wind direction using a 360º potentiometer. Unfortunately, there's a small area between 0º and 360º where the potentiometer can report values that are not sensible. To work around this, the circuitry of the KTA-249 measures the potentiometer resistance and calculates dir ...

... The Davis Anemometer measures wind direction using a 360º potentiometer. Unfortunately, there's a small area between 0º and 360º where the potentiometer can report values that are not sensible. To work around this, the circuitry of the KTA-249 measures the potentiometer resistance and calculates dir ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.