QPro Family of XC1700D QML 配置 PROM

... and the FPGA must both be clocked by an incoming signal. Multiple devices can be concatenated by using the CEO output to drive the CE input of the following device. The clock inputs and the DATA outputs of all PROMs in this chain are interconnected. All devices are compatible and can be cascaded wit ...

... and the FPGA must both be clocked by an incoming signal. Multiple devices can be concatenated by using the CEO output to drive the CE input of the following device. The clock inputs and the DATA outputs of all PROMs in this chain are interconnected. All devices are compatible and can be cascaded wit ...

IDT74FCT3245/A - Integrated Device Technology

... The FCT3245/A octal transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power transceivers are ideal for asynchronous communication between two buses (A and B). The direction control pin (DIR) controls the direction of data flow. The output enable pin (OE) overrid ...

... The FCT3245/A octal transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power transceivers are ideal for asynchronous communication between two buses (A and B). The direction control pin (DIR) controls the direction of data flow. The output enable pin (OE) overrid ...

MAX1134/MAX1135 16-Bit ADCs, 150ksps, 3.3V Single Supply General Description Features

... General Description The MAX1134/MAX1135 are 150ksps, 16-bit ADCs. These serially interfaced ADCs connect directly to SPI™, QSPI™, and MICROWIRE™ devices without external logic. They combine an input scaling network, internal track/hold (T/H), clock, and three general-purpose digital output pins (for ...

... General Description The MAX1134/MAX1135 are 150ksps, 16-bit ADCs. These serially interfaced ADCs connect directly to SPI™, QSPI™, and MICROWIRE™ devices without external logic. They combine an input scaling network, internal track/hold (T/H), clock, and three general-purpose digital output pins (for ...

Low-power LVDS for digital readout circuits

... single-end output swing of 203-288 mV. This driver possesses a 1.8 V supply voltage and can go up to 4.25 Gbps and it is an all-digital LVDS driver. Another work in the literature in 0.18 micron technology is [5] work which use a source coupled logic topology and no internal termination resistance t ...

... single-end output swing of 203-288 mV. This driver possesses a 1.8 V supply voltage and can go up to 4.25 Gbps and it is an all-digital LVDS driver. Another work in the literature in 0.18 micron technology is [5] work which use a source coupled logic topology and no internal termination resistance t ...

a CMOS Quad Sample-and-Hold Amplifier SMP04*

... single supply applications, it is extremely important that the VSS (negative supply) pin be connected to a clean ground. This is because the hold capacitor is internally tied to VSS. Any noise or disturbance in the ground will directly couple to the output of the sample-and-hold, degrading the signa ...

... single supply applications, it is extremely important that the VSS (negative supply) pin be connected to a clean ground. This is because the hold capacitor is internally tied to VSS. Any noise or disturbance in the ground will directly couple to the output of the sample-and-hold, degrading the signa ...

NemFX Reverb2 - Profusion plc

... Nemesis Technology, Inc. assumes no responsibility for any errors which may appear in this document and reserves the right to change information or specifications detailed herein at any time without notice. Before considering any use or application, consult Nemesis Technology, Inc. to verify that th ...

... Nemesis Technology, Inc. assumes no responsibility for any errors which may appear in this document and reserves the right to change information or specifications detailed herein at any time without notice. Before considering any use or application, consult Nemesis Technology, Inc. to verify that th ...

A Generic Architecture for Wafer-Scale Neuromorphic Systems

... values of V.In and all 16 values of the stored digital word are unifonn to within 5%. By tying input lines in parallel. the precision of the MDACs can be extended beyond four bits. For example, when two input lines are tied together, and all four bits in one of the MDACs are held at zero while the o ...

... values of V.In and all 16 values of the stored digital word are unifonn to within 5%. By tying input lines in parallel. the precision of the MDACs can be extended beyond four bits. For example, when two input lines are tied together, and all four bits in one of the MDACs are held at zero while the o ...

PDF link.

... due to its simplicity and scalability, has been the starting point for many min–max circuits in fuzzy logic implementations, such as [5,6] and subsequent modifications [7,8]. Other min–max circuits [9–12] and rectifiers [13–18] with complex topologies allow to implement two-input min–max current sel ...

... due to its simplicity and scalability, has been the starting point for many min–max circuits in fuzzy logic implementations, such as [5,6] and subsequent modifications [7,8]. Other min–max circuits [9–12] and rectifiers [13–18] with complex topologies allow to implement two-input min–max current sel ...

Troubleshooting Digital Circuit

... Logic LOW input – any value less than 1/3 of Vdd Example: if a 5V supply is used for Vdd and Vss is ground, Valid inputs are 0 to 1.7V for a LOW and 3.33 to 5.0V for a HIGH If TTL outputs are used to drive CMOS, a pull-up resistor is often added to the TTL outputs. TTL only outputs 2.4V as ...

... Logic LOW input – any value less than 1/3 of Vdd Example: if a 5V supply is used for Vdd and Vss is ground, Valid inputs are 0 to 1.7V for a LOW and 3.33 to 5.0V for a HIGH If TTL outputs are used to drive CMOS, a pull-up resistor is often added to the TTL outputs. TTL only outputs 2.4V as ...

ICS86004-01

... POWER SUPPLY FILTERING TECHNIQUES As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The 86004-01 provides separate power supplies to isolate any high switching noise from the outputs ...

... POWER SUPPLY FILTERING TECHNIQUES As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The 86004-01 provides separate power supplies to isolate any high switching noise from the outputs ...

ADS5411 数据资料 dataSheet 下载

... The ADS5411 is an 11 bit, 105 MSPS analog-to-digital converter (ADC) that operates from a 5 V supply, while providing 3.3 V CMOS compatible digital outputs. The ADS5411 input buffer isolates the internal switching of the on-chip Track and Hold (T&H) from disturbing the signal source. An internal ref ...

... The ADS5411 is an 11 bit, 105 MSPS analog-to-digital converter (ADC) that operates from a 5 V supply, while providing 3.3 V CMOS compatible digital outputs. The ADS5411 input buffer isolates the internal switching of the on-chip Track and Hold (T&H) from disturbing the signal source. An internal ref ...

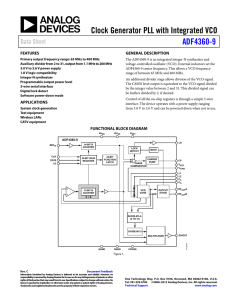

ADF4360-9 Clock Generator PLL with Integrated VCO (Rev. C)

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

ADM483 数据手册DataSheet 下载

... is a twisted pair. Twisted pair cable tends to cancel commonmode noise and the magnetic fields generated by the current flowing through each wire, thereby reducing the effective inductance of the pair. The ADM483 is designed for bidirectional data communications on multipoint transmission lines. A t ...

... is a twisted pair. Twisted pair cable tends to cancel commonmode noise and the magnetic fields generated by the current flowing through each wire, thereby reducing the effective inductance of the pair. The ADM483 is designed for bidirectional data communications on multipoint transmission lines. A t ...

Phase II report - cs.Virginia

... thermal sensors, IO pads). The LEF file is generated by Cadence Abstract Generator. The first part of this file describes technology related information such as metal/via width and pitch. It also includes via generation rules to be used by routing interconnects in Encounter. In the LEF file for our ...

... thermal sensors, IO pads). The LEF file is generated by Cadence Abstract Generator. The first part of this file describes technology related information such as metal/via width and pitch. It also includes via generation rules to be used by routing interconnects in Encounter. In the LEF file for our ...

MC13020 Motorola C-QUAM® AM Stereo Decoder

... 90° relative demodulation angles by reference signals from the phase–locked, divided–down VCO. The output of the I DET is 1 + L + R, with the added benefit (over the Env DET) of being able to produce a negative output on strong co–channel or noise interference. This is used to tell the Lock circuit ...

... 90° relative demodulation angles by reference signals from the phase–locked, divided–down VCO. The output of the I DET is 1 + L + R, with the added benefit (over the Env DET) of being able to produce a negative output on strong co–channel or noise interference. This is used to tell the Lock circuit ...

Dual 160 MHz Rail-to-Rail Amplifier AD8042

... CCD Imaging systems Ultrasound equipment (multichannel) ...

... CCD Imaging systems Ultrasound equipment (multichannel) ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.