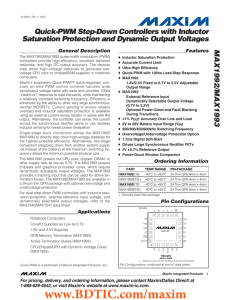

MAX1992/MAX1993 Quick-PWM Step-Down Controllers with Inductor Saturation Protection and Dynamic Output Voltages

... V+ to AGND............................................................-0.3V to +30V VCC to AGND............................................................-0.3V to +6V VDD to PGND............................................................-0.3V to +6V PGOOD, ILIM, SKIP, SHDN to AGND ................ ...

... V+ to AGND............................................................-0.3V to +30V VCC to AGND............................................................-0.3V to +6V VDD to PGND............................................................-0.3V to +6V PGOOD, ILIM, SKIP, SHDN to AGND ................ ...

Figure 55 - We can`t sign you in

... transmitted in any form or by any means manual, electric, electronic, electromechanical, chemical, optical, or otherwise without prior explicit written permission from Alpha Technologies. This documentation, the software it describes, and the information and know-how they contain constitute the prop ...

... transmitted in any form or by any means manual, electric, electronic, electromechanical, chemical, optical, or otherwise without prior explicit written permission from Alpha Technologies. This documentation, the software it describes, and the information and know-how they contain constitute the prop ...

LNCP - RR

... wire several CT coils to the LNCP using a single common wire. The readily available CAT3, CAT5, or other network cable works very well. Each CAT5 cable can be used to connect up to 4 CT coils without interference between their signals. The opposite end of each CAT5 pair is connected to the compressi ...

... wire several CT coils to the LNCP using a single common wire. The readily available CAT3, CAT5, or other network cable works very well. Each CAT5 cable can be used to connect up to 4 CT coils without interference between their signals. The opposite end of each CAT5 pair is connected to the compressi ...

ppt - University of Southern California

... Toutput k1 k2Cload Tin (k3 k4Cload ) k5Cload 2 ...

... Toutput k1 k2Cload Tin (k3 k4Cload ) k5Cload 2 ...

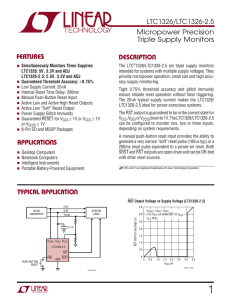

ltc1326.pdf

... narrow (100µs typ) soft reset pulse is generated on the SRST output pin after the button is released. The pushbutton circuitry contains an internal debounce counter which delays the output of the soft reset pulse by typically 20ms. This pin can be OR-tied to the RST pin and issue what is called a “s ...

... narrow (100µs typ) soft reset pulse is generated on the SRST output pin after the button is released. The pushbutton circuitry contains an internal debounce counter which delays the output of the soft reset pulse by typically 20ms. This pin can be OR-tied to the RST pin and issue what is called a “s ...

Z8 Low-Voltage ROM MCU with Infrared Timers

... the CMOS input buffer to float. This might lead to excessive leakage current of more than 100 A. To prevent this leakage, connect the pin to an external signal with a defined logic level or ensure its output state is Low, especially during STOP mode. Internal pull-ups are disabled on any given pin ...

... the CMOS input buffer to float. This might lead to excessive leakage current of more than 100 A. To prevent this leakage, connect the pin to an external signal with a defined logic level or ensure its output state is Low, especially during STOP mode. Internal pull-ups are disabled on any given pin ...

DS1390–DS1394 Low-Voltage SPI/3-Wire RTCs with Trickle Charger General Description

... the control register. The maximum voltage on this pin is 5.5V, independent of VCC or VBACKUP. If enabled, INT functions when the device is powered by either VCC or VBACKUP. Reset. This active-low, open-drain output indicates the status of VCC relative to the V PF specification. As Vcc falls below V ...

... the control register. The maximum voltage on this pin is 5.5V, independent of VCC or VBACKUP. If enabled, INT functions when the device is powered by either VCC or VBACKUP. Reset. This active-low, open-drain output indicates the status of VCC relative to the V PF specification. As Vcc falls below V ...

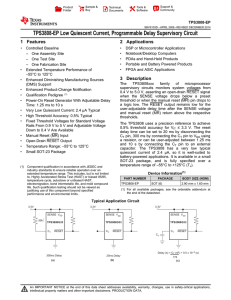

Low Quiescent Current, Programmable Delay Supervisory Circuit

... The reset delay time is determined by the time it takes an on-chip precision 220-nA current source to charge the external capacitor to 1.23 V. When a RESET is asserted the capacitor is discharged. When the RESET conditions are cleared, the internal current source is enabled and begins to charge the ...

... The reset delay time is determined by the time it takes an on-chip precision 220-nA current source to charge the external capacitor to 1.23 V. When a RESET is asserted the capacitor is discharged. When the RESET conditions are cleared, the internal current source is enabled and begins to charge the ...

Programmable Output Voltage Ultra-Low Power Buck

... The TPS6273X family provides a highly integrated ultra low power buck converter solution that is well suited for meeting the special needs of ultra low power applications such as energy harvesting. The TPS6273X provides the system with an externally programmable regulated supply in order to preserve ...

... The TPS6273X family provides a highly integrated ultra low power buck converter solution that is well suited for meeting the special needs of ultra low power applications such as energy harvesting. The TPS6273X provides the system with an externally programmable regulated supply in order to preserve ...

CFP-MSA_CFP8_HW-Spec

... 1.1 SCOPE This hardware specification defines the CFP8 form factor for a 400 Gb/s optical transceiver used for Ethernet and other applications. Specifications provided in this document are a “delta” to the CFP MSA Hardware Specification [1]; the CFP2 Hardware Specification [2]; and the CFP4 Hardware ...

... 1.1 SCOPE This hardware specification defines the CFP8 form factor for a 400 Gb/s optical transceiver used for Ethernet and other applications. Specifications provided in this document are a “delta” to the CFP MSA Hardware Specification [1]; the CFP2 Hardware Specification [2]; and the CFP4 Hardware ...

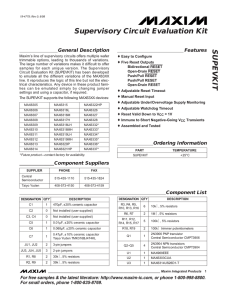

SUPEVKIT Supervisory Circuit Evaluation Kit General Description Features

... Potentiometer R19 sets the overvoltage reset threshold. To enable the overvoltage reset feature, install the jumpers in the positions specified in Table 5. Use a voltmeter to set the power-supply voltage to the desired trip voltage. Connect a voltmeter or oscilloscope to the TP pad. Turn R19 clockwi ...

... Potentiometer R19 sets the overvoltage reset threshold. To enable the overvoltage reset feature, install the jumpers in the positions specified in Table 5. Use a voltmeter to set the power-supply voltage to the desired trip voltage. Connect a voltmeter or oscilloscope to the TP pad. Turn R19 clockwi ...

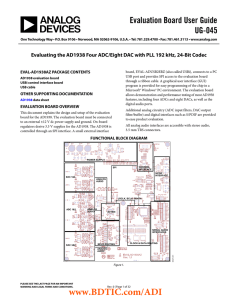

Evaluation Board User Guide UG-045

... For full flexibility of the AD1938, the part can be put in SPI control mode and programmed with the Automated Register Window Builder application (see Figure 4 for the appropriate jumper settings). Changing the registers and setting the DIP switches allow many possible configurations. In the various ...

... For full flexibility of the AD1938, the part can be put in SPI control mode and programmed with the Automated Register Window Builder application (see Figure 4 for the appropriate jumper settings). Changing the registers and setting the DIP switches allow many possible configurations. In the various ...

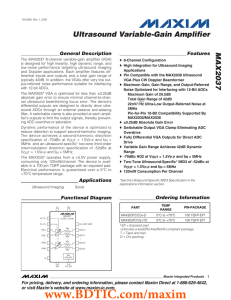

MAX2037 Ultrasound Variable-Gain Amplifier General Description Features

... The MAX2037 8-channel variable-gain amplifier (VGA) is designed for high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of typically 42dB. In addition, the ...

... The MAX2037 8-channel variable-gain amplifier (VGA) is designed for high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of typically 42dB. In addition, the ...

STM1810

... STM1813 and STM1818 feature a debounced manual reset feature that asserts a reset if the RST pin is pulled low for more than 1.5 µs. When used to initiate manual reset, RST debounces signals from devices such as mechanical switches. For devices with this feature, the release of the external switch t ...

... STM1813 and STM1818 feature a debounced manual reset feature that asserts a reset if the RST pin is pulled low for more than 1.5 µs. When used to initiate manual reset, RST debounces signals from devices such as mechanical switches. For devices with this feature, the release of the external switch t ...

MAX2037 - Part Number Search

... The MAX2037 8-channel variable-gain amplifier (VGA) is designed for high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of typically 42dB. In addition, the ...

... The MAX2037 8-channel variable-gain amplifier (VGA) is designed for high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of typically 42dB. In addition, the ...

Dynamic Gate - Washington State University

... cannot be charged again until the next precharge operation. Inputs to the gate can make at most one transition during evaluation. Output can be in the high impedance state during and after evaluation (PDN off), state is stored on CL This behavior is fundamentally different than the static counterpar ...

... cannot be charged again until the next precharge operation. Inputs to the gate can make at most one transition during evaluation. Output can be in the high impedance state during and after evaluation (PDN off), state is stored on CL This behavior is fundamentally different than the static counterpar ...

FT 3120 and FT 3150 Free Topology Smart Transceivers

... channel and can communicate with devices using Echelon's FTT-10A Free Topology Transceiver, and, when used with suitable DC isolation capacitors, the LPT-11 Link Power Transceiver. The free topology transceiver supports polarity insensitive cabling using a star, bus, daisy-chain, loop, or combinatio ...

... channel and can communicate with devices using Echelon's FTT-10A Free Topology Transceiver, and, when used with suitable DC isolation capacitors, the LPT-11 Link Power Transceiver. The free topology transceiver supports polarity insensitive cabling using a star, bus, daisy-chain, loop, or combinatio ...

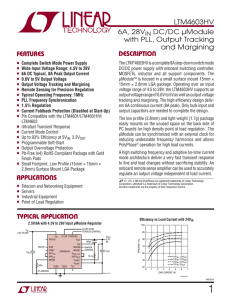

LTM4603HV - 6A, 28VIN DC/DC uModule with PLL, Output Tracking and Margining

... output, then a soft-start capacitor is placed on this pin to ground to control the master ramp rate. A soft-start capacitor can be used for soft-start turn on as a stand alone regulator. Slave operation is performed by putting a resistor divider from the master output to the ground, and connecting t ...

... output, then a soft-start capacitor is placed on this pin to ground to control the master ramp rate. A soft-start capacitor can be used for soft-start turn on as a stand alone regulator. Slave operation is performed by putting a resistor divider from the master output to the ground, and connecting t ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.