Hardware Design Guide for KeyStone Devices

... Hardware Design Guide for KeyStone I Devices Application Report ...

... Hardware Design Guide for KeyStone I Devices Application Report ...

Smart Alarm Clock

... force/weight sensor was considered. Load cells found were mainly for industrial use and are quite expensive. Finding one that was right for our use exceeded $500, more than double out budget, just on one part. Motion sensors (beam type sensors that are activated when the beam’s path is disturbed) we ...

... force/weight sensor was considered. Load cells found were mainly for industrial use and are quite expensive. Finding one that was right for our use exceeded $500, more than double out budget, just on one part. Motion sensors (beam type sensors that are activated when the beam’s path is disturbed) we ...

A Low-Power Wide-Dynamic-Range Analog VLSI Cochlea

... 3. Translinear bipolar biasing circuits provide Qs that are approximately invariant with corner frequency, and allow better matching. Bipolar biasing circuits were ®rst used in cochlear designs by [8]. We shall discuss all of these preceding techniques in this paper. The organization of this paper i ...

... 3. Translinear bipolar biasing circuits provide Qs that are approximately invariant with corner frequency, and allow better matching. Bipolar biasing circuits were ®rst used in cochlear designs by [8]. We shall discuss all of these preceding techniques in this paper. The organization of this paper i ...

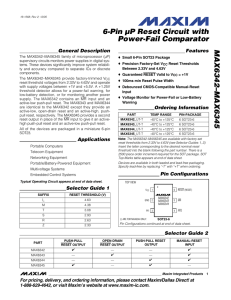

MAX6342–MAX6345 6-Pin µP Reset Circuit with Power-Fail Comparator General Description

... A µP’s reset input starts the µP in a known state. These µP supervisory circuits assert reset to prevent codeexecution errors during power-up, power-down, or brownout conditions. RESET and RESET are guaranteed to be asserted at a valid logic level for VCC > +1V (see the Electrical Characteristics ta ...

... A µP’s reset input starts the µP in a known state. These µP supervisory circuits assert reset to prevent codeexecution errors during power-up, power-down, or brownout conditions. RESET and RESET are guaranteed to be asserted at a valid logic level for VCC > +1V (see the Electrical Characteristics ta ...

Xcell27

... special circuitry for implementing efficient multipliers. Combining these features with an abundance of registers makes it very easy to create very high speed, pipelined multipliers for use in DSP and other applications. ...

... special circuitry for implementing efficient multipliers. Combining these features with an abundance of registers makes it very easy to create very high speed, pipelined multipliers for use in DSP and other applications. ...

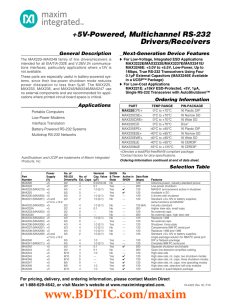

+5V-Powered, Multichannel RS-232 Drivers/Receivers General Description Next-Generation Device Features

... ROUT........................................................-0.3V to (VCC + 0.3V) Short-Circuit Duration, TOUT to GND ........................Continuous Continuous Power Dissipation (TA = +70°C) 14-Pin Plastic DIP (derate 10.00mW/°C above +70°C)....800mW 16-Pin Plastic DIP (derate 10.53mW/°C above + ...

... ROUT........................................................-0.3V to (VCC + 0.3V) Short-Circuit Duration, TOUT to GND ........................Continuous Continuous Power Dissipation (TA = +70°C) 14-Pin Plastic DIP (derate 10.00mW/°C above +70°C)....800mW 16-Pin Plastic DIP (derate 10.53mW/°C above + ...

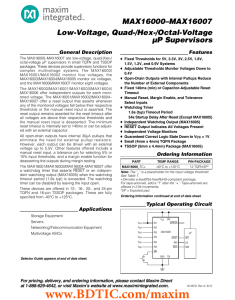

General Description Features

... startup period that allows 54s for the first transition to occur before a reset. Leave WDI unconnected to disable the watchdog timer. MAX16005: If WDI remains low or high for longer than the watchdog timeout period, WDO is asserted. The timer clears whenever a rising or falling edge on WDI is detect ...

... startup period that allows 54s for the first transition to occur before a reset. Leave WDI unconnected to disable the watchdog timer. MAX16005: If WDI remains low or high for longer than the watchdog timeout period, WDO is asserted. The timer clears whenever a rising or falling edge on WDI is detect ...

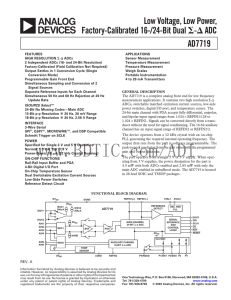

a Low Voltage, Low Power, Factory-Calibrated 16-/24-Bit Dual AD7719

... and bipolar input signal ranges from 1.024 × REFIN1/128 to 1.024 × REFIN1. Signals can be converted directly from a transducer without the need for signal conditioning. The 16-bit auxiliary channel has an input signal range of REFIN2 or REFIN2/2. ...

... and bipolar input signal ranges from 1.024 × REFIN1/128 to 1.024 × REFIN1. Signals can be converted directly from a transducer without the need for signal conditioning. The 16-bit auxiliary channel has an input signal range of REFIN2 or REFIN2/2. ...

Accelnet Plus Module CANopen

... Encoders with differential line-driver outputs provide incremental position feedback via the A/B signals and the optional index signal (X) gives a once per revolution position mark. The MAX3097 receiver has differential inputs with fault protections for the following conditions: Short-circuits line- ...

... Encoders with differential line-driver outputs provide incremental position feedback via the A/B signals and the optional index signal (X) gives a once per revolution position mark. The MAX3097 receiver has differential inputs with fault protections for the following conditions: Short-circuits line- ...

NBSG16M - 2.5 V/3.3 V Multilevel Input to CML Clock/Data Receiver

... Inputs incorporate internal 50 W termination resistors and accept LVNECL (Negative ECL), LVPECL (Positive ECL), LVTTL, LVCMOS, CML, or LVDS. The CML output structure contains internal 50 W source termination resistor to VCC. The device generates 400 mV output amplitude with 50 W receiver resistor to ...

... Inputs incorporate internal 50 W termination resistors and accept LVNECL (Negative ECL), LVPECL (Positive ECL), LVTTL, LVCMOS, CML, or LVDS. The CML output structure contains internal 50 W source termination resistor to VCC. The device generates 400 mV output amplitude with 50 W receiver resistor to ...

Rail-to-Rail Op Amp Design ( cont`d )

... 6. Using maximum/minimum selection circuit to conduct the output current of the differential pair with larger current, as well as larger gm, to the next stage [8][9]; 7. Using electronic zener diode to keep VGSn + | VGSp | constant [10]; 8. Using DC level shift circuit to change the input DC level [ ...

... 6. Using maximum/minimum selection circuit to conduct the output current of the differential pair with larger current, as well as larger gm, to the next stage [8][9]; 7. Using electronic zener diode to keep VGSn + | VGSp | constant [10]; 8. Using DC level shift circuit to change the input DC level [ ...

MAX965–MAX970 Single/Dual/Quad, Micropower, Ultra-Low-Voltage, Rail-to-Rail I/O Comparators General Description

... ultra-low-voltage comparators feature rail-to-rail inputs and outputs and an internal 1.235V ±1.5% bandgap reference. These devices operate from a single +1.6V to +5.5V supply voltage range, and consume less than 5µA supply current per comparator over the extended temperature range. Internal hystere ...

... ultra-low-voltage comparators feature rail-to-rail inputs and outputs and an internal 1.235V ±1.5% bandgap reference. These devices operate from a single +1.6V to +5.5V supply voltage range, and consume less than 5µA supply current per comparator over the extended temperature range. Internal hystere ...

Adjustable Battery-Backup Supervisor for RAM

... chip-enable signal gating The internal gating of chip-enable (CE) signals prevents erroneous data from corrupting CMOS RAM during an under-voltage condition. The TPS3613 uses a series transmission gate from CEIN to CEOUT. During normal operation (reset not asserted), the CE transmission gate is enab ...

... chip-enable signal gating The internal gating of chip-enable (CE) signals prevents erroneous data from corrupting CMOS RAM during an under-voltage condition. The TPS3613 uses a series transmission gate from CEIN to CEOUT. During normal operation (reset not asserted), the CE transmission gate is enab ...

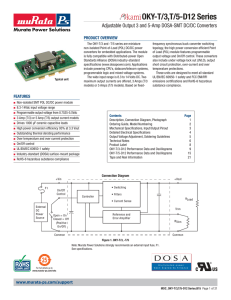

OKY-T/3,T/5-D12 Series

... These converters include a soft start circuit to moderate the duty cycle of its PWM controller at power up, thereby limiting the input inrush current. The On/Off Remote Control interval from On command to Vout regulated assumes that the converter already has its input voltage stabilized above the St ...

... These converters include a soft start circuit to moderate the duty cycle of its PWM controller at power up, thereby limiting the input inrush current. The On/Off Remote Control interval from On command to Vout regulated assumes that the converter already has its input voltage stabilized above the St ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.