LX7730 Datasheet

... universal inputs can also function as variable bi-level inputs with the threshold set by an internal 8 bit digital-toanalog converter. There is an additional 10 bit digital-toanalog current DAC with complementary outputs. Finally there are 8 fixed threshold bi-level inputs. The LX7730 is register pr ...

... universal inputs can also function as variable bi-level inputs with the threshold set by an internal 8 bit digital-toanalog converter. There is an additional 10 bit digital-toanalog current DAC with complementary outputs. Finally there are 8 fixed threshold bi-level inputs. The LX7730 is register pr ...

ISL55100B Datasheet

... respectively. COMP HIGH and COMP LOW set all the comparator output levels and COMP HIGH must be more positive than COMP LOW. These two inputs are unbuffered supply pins, so the sources driving these pins must provide adequate current for the expected load. COMP HIGH and COMP LOW typically connect to ...

... respectively. COMP HIGH and COMP LOW set all the comparator output levels and COMP HIGH must be more positive than COMP LOW. These two inputs are unbuffered supply pins, so the sources driving these pins must provide adequate current for the expected load. COMP HIGH and COMP LOW typically connect to ...

Current-shunt feedback

... The signal Xi , representing the output of the summing network is the amplifier input Xi . If the feedback signal Xf is 180 out of phase with the input Xs—as is true in negative feedback systems—then Xi is a difference signal. Therefore, Xi decreases as | Xf | increases. The reverse transmission o ...

... The signal Xi , representing the output of the summing network is the amplifier input Xi . If the feedback signal Xf is 180 out of phase with the input Xs—as is true in negative feedback systems—then Xi is a difference signal. Therefore, Xi decreases as | Xf | increases. The reverse transmission o ...

ADuC834 数据手册DataSheet 下载

... temperature sensor and a PGA (allowing direct measurement of low level signals). The ADCs with on-chip digital filtering and programmable output data rates are intended for the measurement of wide dynamic range, low frequency signals, such as those in weigh scale, strain-gage, pressure transducer, o ...

... temperature sensor and a PGA (allowing direct measurement of low level signals). The ADCs with on-chip digital filtering and programmable output data rates are intended for the measurement of wide dynamic range, low frequency signals, such as those in weigh scale, strain-gage, pressure transducer, o ...

P84662

... The AC must first be wired into the buildings main electrical power. The conduit entry can be either from the top or left hand side using the knock-outs. See Figure 3. Connect Earth Ground First. M. Connect backup batteries. Observe correct polarity, use two of the same connected in series. Use eith ...

... The AC must first be wired into the buildings main electrical power. The conduit entry can be either from the top or left hand side using the knock-outs. See Figure 3. Connect Earth Ground First. M. Connect backup batteries. Observe correct polarity, use two of the same connected in series. Use eith ...

600/1v3 - JL Audio

... appropriate power ring or specialized battery terminal connector, such as the JL Audio XB-BTU or XD-BTS. This connection must be tight and corrosion-free to ensure proper connectivity. This wire MUST be fused appropriately for safety. Any power wires run through metal barriers (such as firewalls), m ...

... appropriate power ring or specialized battery terminal connector, such as the JL Audio XB-BTU or XD-BTS. This connection must be tight and corrosion-free to ensure proper connectivity. This wire MUST be fused appropriately for safety. Any power wires run through metal barriers (such as firewalls), m ...

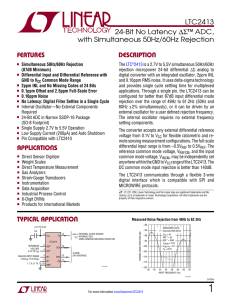

LTC2413 - 24-Bit No Latency ∆Σ™ ADC, with Simultaneous 50Hz

... Note 7: FO = 0V (internal oscillator) or fEOSC = 139800Hz ± 2% (external oscillator). Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as digital input. The frequency of the clock signal driving SCK during the data output is fESCK and is expressed in kHz. Note ...

... Note 7: FO = 0V (internal oscillator) or fEOSC = 139800Hz ± 2% (external oscillator). Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as digital input. The frequency of the clock signal driving SCK during the data output is fESCK and is expressed in kHz. Note ...

Analog Devices ADuC845, ADuC847, ADuC848 Data Sheet

... 3 levels of Flash/EE program memory security In-circuit serial download (no external hardware) High speed user download (5 seconds) 2304 bytes on-chip data RAM 8051-based core 8051-compatible instruction set High performance single-cycle core 32 kHz external crystal On-chip programmable PLL (12.58 M ...

... 3 levels of Flash/EE program memory security In-circuit serial download (no external hardware) High speed user download (5 seconds) 2304 bytes on-chip data RAM 8051-based core 8051-compatible instruction set High performance single-cycle core 32 kHz external crystal On-chip programmable PLL (12.58 M ...

0.35µm ULC Series

... FPGAs on applications which do not require large memories (see UA1E datasheet for application with memories) .Typically, ULC die size is 50% smaller than the equivalent FPGA die size. Devices are implemented in high–performance CMOS technology with 0.35µm (drawn) channel lengths, and are capable of ...

... FPGAs on applications which do not require large memories (see UA1E datasheet for application with memories) .Typically, ULC die size is 50% smaller than the equivalent FPGA die size. Devices are implemented in high–performance CMOS technology with 0.35µm (drawn) channel lengths, and are capable of ...

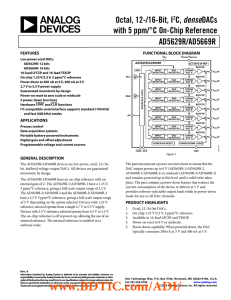

AD5629R: 英文产品数据手册下载

... Address Input. Sets the least significant bit of the 7-bit slave address. Power Supply Input. These parts can be operated from 2.7 V to 5.5 V. Decouple the supply with a 10 μF capacitor in parallel with a 0.1 μF capacitor to GND. Analog Output Voltage from DAC A. The output amplifier has rail-to-rai ...

... Address Input. Sets the least significant bit of the 7-bit slave address. Power Supply Input. These parts can be operated from 2.7 V to 5.5 V. Decouple the supply with a 10 μF capacitor in parallel with a 0.1 μF capacitor to GND. Analog Output Voltage from DAC A. The output amplifier has rail-to-rai ...

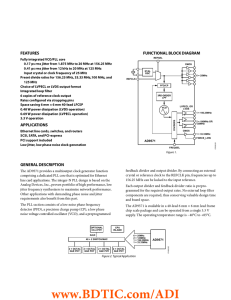

FEATURES FUNCTIONAL BLOCK DIAGRAM

... The AD9571 provides a multioutput clock generator function comprising a dedicated PLL core that is optimized for Ethernet line card applications. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network ...

... The AD9571 provides a multioutput clock generator function comprising a dedicated PLL core that is optimized for Ethernet line card applications. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network ...

MCP809/MCP810 3-Pin Microprocessor Reset

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain t ...

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain t ...

Design of 8-bit Ripple Carry Adder Using Constant Delay

... takes places when IN make a transition from high to low before CLK becomes low. When CLK becomes low, X rises to logic “1” and Y remains at logic “0” for the entire evaluation cycle. The delay is measured by the falling edge of both CLK and Out: hence the name C–Q delay. D–Q delay mode utilizes the ...

... takes places when IN make a transition from high to low before CLK becomes low. When CLK becomes low, X rises to logic “1” and Y remains at logic “0” for the entire evaluation cycle. The delay is measured by the falling edge of both CLK and Out: hence the name C–Q delay. D–Q delay mode utilizes the ...

2 × 2 W, Filterless, Stereo, Class-D C SSM2380

... scheme that requires no external LC output filters. The modulation continues to provide high efficiency even at low output power. The SSM2380 operates with 93% efficiency at 1.4 W into 8 Ω or with 85% efficiency at 2 W into 4 Ω from a 5.0 V supply and has an SNR of >100 dB. Spread-spectrum pulse den ...

... scheme that requires no external LC output filters. The modulation continues to provide high efficiency even at low output power. The SSM2380 operates with 93% efficiency at 1.4 W into 8 Ω or with 85% efficiency at 2 W into 4 Ω from a 5.0 V supply and has an SNR of >100 dB. Spread-spectrum pulse den ...

GE 12A Digital PicoDLynx : Non-Isolated DC-DC Power Modules Data Sheet

... 12A Digital PicoDLynxTM: Non-Isolated DC-DC Power Modules 3Vdc –14.4Vdc input; 0.45Vdc to 5.5Vdc output; 12A Output Current Digital Interface Specifications Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. See Feature Desc ...

... 12A Digital PicoDLynxTM: Non-Isolated DC-DC Power Modules 3Vdc –14.4Vdc input; 0.45Vdc to 5.5Vdc output; 12A Output Current Digital Interface Specifications Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. See Feature Desc ...

Chapter 6

... TTL level : logic 0(0.0V~0.8V) logic 1(2.0V~5.0V) switch-based device : not TTL-compatible ...

... TTL level : logic 0(0.0V~0.8V) logic 1(2.0V~5.0V) switch-based device : not TTL-compatible ...

On the Efficacy of Input Vector Control to Mitigate

... effect of this technique on an adder is evaluated, however, detailed research for random logic is needed. In this paper, we first propose a co-simulation flow to estimate NBTI-induced aging effect and leakage power, and then evaluate the potential and efficacy of the IVC techniques. The contribution ...

... effect of this technique on an adder is evaluated, however, detailed research for random logic is needed. In this paper, we first propose a co-simulation flow to estimate NBTI-induced aging effect and leakage power, and then evaluate the potential and efficacy of the IVC techniques. The contribution ...

MAX17000 Complete DDR2 and DDR3 Memory Power-Management Solution General Description

... switching frequency. The Quick-PWM architecture circumvents the poor load-transient timing problems of fixed-frequency current-mode PWMs while also avoiding the problems caused by widely varying switching frequencies in conventional constant-on-time and constant-off-time PWM schemes. The controller ...

... switching frequency. The Quick-PWM architecture circumvents the poor load-transient timing problems of fixed-frequency current-mode PWMs while also avoiding the problems caused by widely varying switching frequencies in conventional constant-on-time and constant-off-time PWM schemes. The controller ...

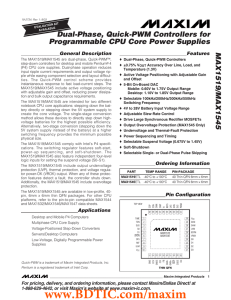

MAX1519/MAX1545 Dual-Phase, Quick-PWM Controllers for Programmable CPU Core Power Supplies General Description

... step-down controllers for desktop and mobile Pentium® 4 (P4) CPU core supplies. Dual-phase operation reduces input ripple current requirements and output voltage ripple while easing component selection and layout difficulties. The Quick-PWM control scheme provides instantaneous response to fast load ...

... step-down controllers for desktop and mobile Pentium® 4 (P4) CPU core supplies. Dual-phase operation reduces input ripple current requirements and output voltage ripple while easing component selection and layout difficulties. The Quick-PWM control scheme provides instantaneous response to fast load ...

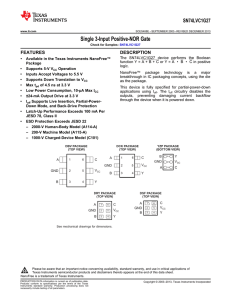

Single 3-Input Positive-NOR Gate (Rev. E)

... Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on ...

... Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.