Midterm Solutions

... All we need to do is generate a table that shows the corresponding output for each possible input set, and compare it to the output when a stuck-at fault is present. For example, if x2 becomes stuck at 0, the function can never be 1, no matter what the values of x1 and x3 are. Overall, you should fi ...

... All we need to do is generate a table that shows the corresponding output for each possible input set, and compare it to the output when a stuck-at fault is present. For example, if x2 becomes stuck at 0, the function can never be 1, no matter what the values of x1 and x3 are. Overall, you should fi ...

LMC7221 Tiny CMOS Comparator with Rail-To

... previously used to match signals to the limited input range of earlier comparators. This is useful to power supply monitoring circuits which need to sense their own power supply, and compare it to a reference voltage which is close to the power supply voltage. The wide input range can also be useful ...

... previously used to match signals to the limited input range of earlier comparators. This is useful to power supply monitoring circuits which need to sense their own power supply, and compare it to a reference voltage which is close to the power supply voltage. The wide input range can also be useful ...

MAX5186/MAX5189 Dual, 8-Bit, 40MHz, Current/Voltage, Simultaneous-Output DACs General Description

... Simultaneous-Output DACs Detailed Description The MAX5186/MAX5189 are dual, 8-bit digital-to-analog converters (DACs) capable of operating with clock speeds up to 40MHz. Each of these dual converters consists of separate input and DAC registers, followed by a current source array capable of generati ...

... Simultaneous-Output DACs Detailed Description The MAX5186/MAX5189 are dual, 8-bit digital-to-analog converters (DACs) capable of operating with clock speeds up to 40MHz. Each of these dual converters consists of separate input and DAC registers, followed by a current source array capable of generati ...

Dual Power-Supply Supervisors

... † Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

... † Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

MAX8794 Low-Voltage DDR Linear Regulator General Description Features

... that goes high 2ms (typ) after the output initially reaches regulation during startup. PGOOD transitions to low after a 10µs delay when either the output goes out of regulation by ±150mV, or when the device enters shutdown. Connect a pullup resistor from PGOOD to VCC for a logic-level output. Use a ...

... that goes high 2ms (typ) after the output initially reaches regulation during startup. PGOOD transitions to low after a 10µs delay when either the output goes out of regulation by ±150mV, or when the device enters shutdown. Connect a pullup resistor from PGOOD to VCC for a logic-level output. Use a ...

experiment #1 - Dr. Charbel T. Fahed, Ph.D.

... 5. Indicate the levels on the chip diagram and hook up the circuit to verify the truth table for the expression. ...

... 5. Indicate the levels on the chip diagram and hook up the circuit to verify the truth table for the expression. ...

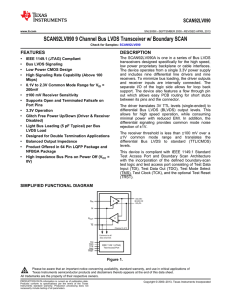

SCAN92LV090 9 Channel Bus LVDS

... General application guidelines and hints may be found in the following application notes: AN-808 (SNLA028), AN-1108 (SNLA008), AN-977 (SNLA166), AN-971 (SNLA165), and AN-903 (SNLA034). There are a few common practices which should be implied when designing PCB for Bus LVDS signaling. Recommended pra ...

... General application guidelines and hints may be found in the following application notes: AN-808 (SNLA028), AN-1108 (SNLA008), AN-977 (SNLA166), AN-971 (SNLA165), and AN-903 (SNLA034). There are a few common practices which should be implied when designing PCB for Bus LVDS signaling. Recommended pra ...

LT6205/LT6206/LT6207 - Single/Dual/Quad Single Supply 3V, 100MHz Video Op Amps

... Note 5: Matching parameters are the difference between the two amplifiers A and D and between B and C of the LT6207; between the two amplifiers of the LT6206. Note 6: This parameter is not 100% tested. Note 7: Output voltage swings are measured between the output and power supply rails. Note 8: Full p ...

... Note 5: Matching parameters are the difference between the two amplifiers A and D and between B and C of the LT6207; between the two amplifiers of the LT6206. Note 6: This parameter is not 100% tested. Note 7: Output voltage swings are measured between the output and power supply rails. Note 8: Full p ...

OP77 (Rev. G)

... Removed Figure 33 and Two Subsequent Paragraphs ............... 12 6/09—Rev. C to Rev. D Changes to Figure 1 and Figure 2 ................................................... 1 Changes to Table 1 ............................................................................ 3 Removed Endnote 1 and Endn ...

... Removed Figure 33 and Two Subsequent Paragraphs ............... 12 6/09—Rev. C to Rev. D Changes to Figure 1 and Figure 2 ................................................... 1 Changes to Table 1 ............................................................................ 3 Removed Endnote 1 and Endn ...

SN74LV4046A High-Speed CMOS Logic Phase

... the phase differences of signals (SIGIN) and the compartor input (COMPIN) as shown in Figure 7. The average of V DEM is equal to 1/2 VCC when there is no signal or noise at SIGIN, and with this input the VCO oscillates at the center frequency (fo). • Phase comparator 2 (PC2) is an Edge-Triggered Fli ...

... the phase differences of signals (SIGIN) and the compartor input (COMPIN) as shown in Figure 7. The average of V DEM is equal to 1/2 VCC when there is no signal or noise at SIGIN, and with this input the VCO oscillates at the center frequency (fo). • Phase comparator 2 (PC2) is an Edge-Triggered Fli ...

MAX31913 - Maxim Part Number Search

... The MAX31913 industrial interface serializer translates, conditions, and serializes the 24V digital output of sensors and switches used in industrial, process, and building automation to 5V CMOS-compatible signals required by microcontrollers. It provides the front-end interface circuit of a program ...

... The MAX31913 industrial interface serializer translates, conditions, and serializes the 24V digital output of sensors and switches used in industrial, process, and building automation to 5V CMOS-compatible signals required by microcontrollers. It provides the front-end interface circuit of a program ...

PLC Demo System User Guide UG-181

... the input requirements of the AD7793. This circuit has bipolar supplies and, thus, allows bipolar inputs. ...

... the input requirements of the AD7793. This circuit has bipolar supplies and, thus, allows bipolar inputs. ...

Miniature In Cell Amplifier for Strain Gauges

... The ability of a signal conditioner to display both positive and negative readings. The resistance measured across the excitation terminals of a Strain Gauge. Adjustment of an instrument or compiling a deviation chart so that it’s reading can be correlated to the actual value being measured. The abi ...

... The ability of a signal conditioner to display both positive and negative readings. The resistance measured across the excitation terminals of a Strain Gauge. Adjustment of an instrument or compiling a deviation chart so that it’s reading can be correlated to the actual value being measured. The abi ...

Bridging the Divide: Part I - DAC Introduction By Bill

... Returning to Equation 1, the LSB value is inversely proportional to the number of bits (N) and directly proportional to VREF. Figure 2 shows a pure sinusoid (A), the output of a 4-bit DAC (B), and a 6-bit DAC (C). While an ideal DAC output is actually represented by discrete points, the output of a ...

... Returning to Equation 1, the LSB value is inversely proportional to the number of bits (N) and directly proportional to VREF. Figure 2 shows a pure sinusoid (A), the output of a 4-bit DAC (B), and a 6-bit DAC (C). While an ideal DAC output is actually represented by discrete points, the output of a ...

GENERAL DESCRIPTION FEATURES

... With the exception of the START and STOP condition, transitions of SDA may occur only during the LOW state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the required setup and hold time (tHD:DAT after the falling edge of SCL and tSU:DAT before the r ...

... With the exception of the START and STOP condition, transitions of SDA may occur only during the LOW state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the required setup and hold time (tHD:DAT after the falling edge of SCL and tSU:DAT before the r ...

LT6010 - 135µA, 14nV/rtHz, Rail-to-Rail Output Precision Op Amp with Shutdown

... leads should be short, close together, and away from heat dissipating components. Air currents across the board can also generate temperature differentials. The extremely low input bias currents (20pA typical) allow high accuracy to be maintained with high impedance sources and feedback resistors. T ...

... leads should be short, close together, and away from heat dissipating components. Air currents across the board can also generate temperature differentials. The extremely low input bias currents (20pA typical) allow high accuracy to be maintained with high impedance sources and feedback resistors. T ...

AN7 - Some Techniques for Direct Digitization of Transducer Outputs

... impossible to digitize without DC preamplification. In fact, both transducers’ outputs may be directly digitized to stable 10-bit resolution using circuitry specifically designed for the function. This application note details circuit techniques which directly digitize the low level outputs of a varie ...

... impossible to digitize without DC preamplification. In fact, both transducers’ outputs may be directly digitized to stable 10-bit resolution using circuitry specifically designed for the function. This application note details circuit techniques which directly digitize the low level outputs of a varie ...

XC3S1400A 工程样品勘误表

... A software workaround exists, as shown in Figure 2. This circuit is automatically inserted by the ISE development software starting with version 9.1i. Using FPGA logic, the circuit monitors both the LOCKED output from the DCM_SP function and the STATUS[2] bit, which indicates that the DFS output CLK ...

... A software workaround exists, as shown in Figure 2. This circuit is automatically inserted by the ISE development software starting with version 9.1i. Using FPGA logic, the circuit monitors both the LOCKED output from the DCM_SP function and the STATUS[2] bit, which indicates that the DFS output CLK ...

MAX11254EVKIT# Datasheet Maxim Integrated

... Sample Rate, Number of Samples and Clock Source if FPGA device is used. The Read Data and Status information is displayed on the right, which shows the data in both voltage and Hex, the sample rate, and power state for the selected channel. In addition, if there are any errors, the indicator lights ...

... Sample Rate, Number of Samples and Clock Source if FPGA device is used. The Read Data and Status information is displayed on the right, which shows the data in both voltage and Hex, the sample rate, and power state for the selected channel. In addition, if there are any errors, the indicator lights ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.