MAX1082/MAX1083 300ksps/400ksps, Single-Supply, 4-Channel, Serial 10-Bit ADCs with Internal Reference General Description

... The MAX1082/MAX1083 10-bit analog-to-digital converters (ADCs) combine a 4-channel analog-input multiplexer, high-bandwidth track/hold (T/H), and serial interface with high conversion speed and low power consumption. The MAX1082 operates from a single +4.5V to +5.5V supply; the MAX1083 operates from ...

... The MAX1082/MAX1083 10-bit analog-to-digital converters (ADCs) combine a 4-channel analog-input multiplexer, high-bandwidth track/hold (T/H), and serial interface with high conversion speed and low power consumption. The MAX1082 operates from a single +4.5V to +5.5V supply; the MAX1083 operates from ...

Exploring Different SAR ADC Analog Input

... process, a binary search is performed through all possible digital codes (quantization levels) where the end result converges on a code that brings the internally housed comparator back into balance. The combination of ones and zeros represents the decision sequence generated by the circuit that bro ...

... process, a binary search is performed through all possible digital codes (quantization levels) where the end result converges on a code that brings the internally housed comparator back into balance. The combination of ones and zeros represents the decision sequence generated by the circuit that bro ...

instruction manual

... 2.2.1.2 When the adjustable output is used as CV output, first should rotate clockwise the CC adjustment (2) and (17) to maximum, then turn on power switch (13), adjust CV adjustment (4) and (14) till output voltage reach required voltage value. At this time, the CC state indicator (1) and (11) go o ...

... 2.2.1.2 When the adjustable output is used as CV output, first should rotate clockwise the CC adjustment (2) and (17) to maximum, then turn on power switch (13), adjust CV adjustment (4) and (14) till output voltage reach required voltage value. At this time, the CC state indicator (1) and (11) go o ...

INTELLIGENT MULTIPLEX SYSTEM

... node failures caused by loss of communications between input and control units. In addition, the software provides a two-stage continuous failure analysis for all outputs. The hardware also has provisions to overcome possible node failures in the unlikely event of a processor failure. ...

... node failures caused by loss of communications between input and control units. In addition, the software provides a two-stage continuous failure analysis for all outputs. The hardware also has provisions to overcome possible node failures in the unlikely event of a processor failure. ...

Dual Differential Line Driver (Rev. B)

... Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above. Green (RoHS ...

... Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above. Green (RoHS ...

74VHC4046 CMOS Phase Lock Loop

... flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 5. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle. Phase comparator II operates in such a way as to force the PLL into lock with 0 pha ...

... flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 5. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle. Phase comparator II operates in such a way as to force the PLL into lock with 0 pha ...

3. The MC6802 MICROPROCESSOR

... 1) All the higher order address lines will be forced high. 2) For the restart, the last two (FFFEH, FFFFH) locations in memory will be used to load the program that is addressed by the program counter. 3) During the restart routine, the interrupt mask bit in the Conditon Code Register (CCR) is set ( ...

... 1) All the higher order address lines will be forced high. 2) For the restart, the last two (FFFEH, FFFFH) locations in memory will be used to load the program that is addressed by the program counter. 3) During the restart routine, the interrupt mask bit in the Conditon Code Register (CCR) is set ( ...

MAX1206 40Msps, 12-Bit ADC General Description Features

... A flexible reference structure allows the MAX1206 to use its internal precision bandgap reference or accept an externally applied reference. A common-mode reference is provided to simplify design and reduce external component count in differential analog input circuits. The MAX1206 supports both a s ...

... A flexible reference structure allows the MAX1206 to use its internal precision bandgap reference or accept an externally applied reference. A common-mode reference is provided to simplify design and reduce external component count in differential analog input circuits. The MAX1206 supports both a s ...

FSAV330 — 4-Channel, 2:1 Video Switch FAV330 — 4-Channel, 2: 1 Video Swit

... The FSAV330 video switch is a quad, single-pole / double-throw, high-speed CMOS TTL-compatible video switch. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. ...

... The FSAV330 video switch is a quad, single-pole / double-throw, high-speed CMOS TTL-compatible video switch. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. ...

74VHC4046 CMOS Phase Lock Loop

... flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 5. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle. Phase comparator II operates in such a way as to force the PLL into lock with 0 pha ...

... flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 5. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle. Phase comparator II operates in such a way as to force the PLL into lock with 0 pha ...

Technical description APCI-3002 Analog input board - ADDI-DATA

... Please read this licence carefully before using the standard software. The customer is only granted the right to use this software if he/she agrees with the conditions of this licence. The software may only be used to set up the ADDI-DATA products. Reproduction of the software is forbidden (except f ...

... Please read this licence carefully before using the standard software. The customer is only granted the right to use this software if he/she agrees with the conditions of this licence. The software may only be used to set up the ADDI-DATA products. Reproduction of the software is forbidden (except f ...

ADV7127 数据手册DataSheet 下载

... Clock Input (TTL Compatible). The rising edge of CLOCK latches the R0–R9, G0–G9, B0–B9, SYNC and BLANK pixel and control inputs. It is typically the pixel clock rate of the video system. CLOCK should be driven by a dedicated TTL buffer. Data Inputs (TTL Compatible). Data is latched on the rising edg ...

... Clock Input (TTL Compatible). The rising edge of CLOCK latches the R0–R9, G0–G9, B0–B9, SYNC and BLANK pixel and control inputs. It is typically the pixel clock rate of the video system. CLOCK should be driven by a dedicated TTL buffer. Data Inputs (TTL Compatible). Data is latched on the rising edg ...

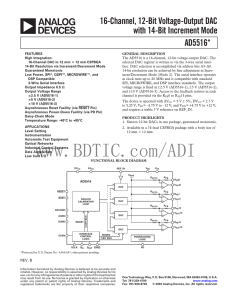

AD5516: 英文产品数据手册下载

... Feedback Resistors. For nominal output voltage range, connect each R FB to its corresponding VOUT. Access to the feedback resistors enables the user to increase the DAC current drive or generate programmable current sources. They should not be used for gain adjustment. Active Low Input. This is the ...

... Feedback Resistors. For nominal output voltage range, connect each R FB to its corresponding VOUT. Access to the feedback resistors enables the user to increase the DAC current drive or generate programmable current sources. They should not be used for gain adjustment. Active Low Input. This is the ...

DAC7724 数据资料 dataSheet 下载

... ● 12-BIT LINEARITY AND MONOTONICITY: –40°C to +85°C ● RESET TO MID-SCALE (DAC7724) OR ZERO-SCALE (DAC7725) ● DATA READBACK ● DOUBLE-BUFFERED DATA INPUTS ...

... ● 12-BIT LINEARITY AND MONOTONICITY: –40°C to +85°C ● RESET TO MID-SCALE (DAC7724) OR ZERO-SCALE (DAC7725) ● DATA READBACK ● DOUBLE-BUFFERED DATA INPUTS ...

SMTR Single and Dual DC-DC Converters

... minimizing interference and reducing the need for filtering. In sync mode, the converter will run at any frequency between 500 kHz and 675 kHz. The sync control operates with an active high at any duty cycle between 40% and 60%. The sync pin should be connected to input common pin when not in use. ...

... minimizing interference and reducing the need for filtering. In sync mode, the converter will run at any frequency between 500 kHz and 675 kHz. The sync control operates with an active high at any duty cycle between 40% and 60%. The sync pin should be connected to input common pin when not in use. ...

MAX5174/MAX5176 General Description Features

... +5V supply, and the MAX5176 operates from a single +3V supply. Both devices draw only 280µA of supply current, which reduces to 1µA in shutdown. In addition, the programmable power-up reset feature allows for a user-selectable output voltage state of either 0 or midscale. The 3-wire, digital, serial ...

... +5V supply, and the MAX5176 operates from a single +3V supply. Both devices draw only 280µA of supply current, which reduces to 1µA in shutdown. In addition, the programmable power-up reset feature allows for a user-selectable output voltage state of either 0 or midscale. The 3-wire, digital, serial ...

XLogic E Signature™ Channel Owner`s Manual

... light indication of gain reduction. Due to the vagaries of the original design, the range of the threshold control is indicated as either LESS or MORE! The gain reduction indication takes the form of a bi-colour LED located under the IN switch; it will glow green to show that it is in-circuit and th ...

... light indication of gain reduction. Due to the vagaries of the original design, the range of the threshold control is indicated as either LESS or MORE! The gain reduction indication takes the form of a bi-colour LED located under the IN switch; it will glow green to show that it is in-circuit and th ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.