The DatasheetArchive - Datasheet Search Engine - I

... The guard time control input provides two sets of detecte&~”” When using the alternate clock source from ATB, Xin should time and release time, both within the allowed ranges of t@e be tied to VDD. on and tone off (see Figure 1). A longer tone @%~i~ttime rejects signals too short to be considered va ...

... The guard time control input provides two sets of detecte&~”” When using the alternate clock source from ATB, Xin should time and release time, both within the allowed ranges of t@e be tied to VDD. on and tone off (see Figure 1). A longer tone @%~i~ttime rejects signals too short to be considered va ...

On Clock Network Design for Sub

... Scope and limitations to individual methods Slew Aware Clock Tree Design for Sub-threshold: Good for slew control by design Universal for all clock network topologies Always saves something in power Does not address variations ...

... Scope and limitations to individual methods Slew Aware Clock Tree Design for Sub-threshold: Good for slew control by design Universal for all clock network topologies Always saves something in power Does not address variations ...

PL-2 Analog Peak Limiter Manual Features · Two independent

... built-in to the limiting action. This means that instead of chopping off the peaks and losing all dynamic information, some 'wiggle' is left at the top. The JFET and MOSFET devices have differing amounts of compliance, which results in differences in the character of limiting. The JFET tends to prod ...

... built-in to the limiting action. This means that instead of chopping off the peaks and losing all dynamic information, some 'wiggle' is left at the top. The JFET and MOSFET devices have differing amounts of compliance, which results in differences in the character of limiting. The JFET tends to prod ...

INA121 数据资料 dataSheet 下载

... mismatch in C1 and C 2. Make C 3 much larger than C1 and C 2. If properly matched, C1 and C2 also improve ac CMR. ...

... mismatch in C1 and C 2. Make C 3 much larger than C1 and C 2. If properly matched, C1 and C2 also improve ac CMR. ...

MAX9121/MAX9122 Quad LVDS Line Receivers with Integrated Termination and Flow-Through Pinout General Description

... signals as low as 100mV and as high as 1V within an input voltage range of 0 to 2.4V. The 250mV to 400mV differential output of an LVDS driver is nominally centered around a +1.2V offset. This offset, coupled with the receiver’s 0 to 2.4V input voltage range, allows an approximate ±1V shift in the s ...

... signals as low as 100mV and as high as 1V within an input voltage range of 0 to 2.4V. The 250mV to 400mV differential output of an LVDS driver is nominally centered around a +1.2V offset. This offset, coupled with the receiver’s 0 to 2.4V input voltage range, allows an approximate ±1V shift in the s ...

DATA SHEET UDA1334ATS Low power audio DAC with PLL

... implemented as current sources and are summed at virtual ground of the output operational amplifier. In this way very high signal-to-noise performance and low clock jitter sensitivity is achieved. No post filter is needed due to the inherent filter function of the DAC. On-board amplifiers convert th ...

... implemented as current sources and are summed at virtual ground of the output operational amplifier. In this way very high signal-to-noise performance and low clock jitter sensitivity is achieved. No post filter is needed due to the inherent filter function of the DAC. On-board amplifiers convert th ...

INA118 数据资料 dataSheet 下载

... one input and +40V on the other input will not cause damage. Internal circuitry on each input provides low series impedance under normal signal conditions. To provide equivalent protection, series input resistors would contribute excessive noise. If the input is overloaded, the protection circuitry ...

... one input and +40V on the other input will not cause damage. Internal circuitry on each input provides low series impedance under normal signal conditions. To provide equivalent protection, series input resistors would contribute excessive noise. If the input is overloaded, the protection circuitry ...

RESET MAX8530/MAX8531 Dual Low-Dropout Linear Regulators with

... The MAX8530/MAX8531 are low-power, low-dropout, low-quiescent current linear regulators with reset designed primarily for battery-powered applications. For preset output voltages, refer to the Output Voltage Selector Guide. Other combinations between 1.5V and 3.3V are available in 50mV increments. T ...

... The MAX8530/MAX8531 are low-power, low-dropout, low-quiescent current linear regulators with reset designed primarily for battery-powered applications. For preset output voltages, refer to the Output Voltage Selector Guide. Other combinations between 1.5V and 3.3V are available in 50mV increments. T ...

a +5 V, Serial Input Complete 12-Bit DAC DAC8512

... present on the SDI, CS, LD, and CLR pins. Since these inputs are standard CMOS logic structures they contribute static power dissipation dependent on the actual driving logic VOH and VOL voltage levels. The graph in Figure 9 shows the effect on total DAC8512 supply current as a function of the actua ...

... present on the SDI, CS, LD, and CLR pins. Since these inputs are standard CMOS logic structures they contribute static power dissipation dependent on the actual driving logic VOH and VOL voltage levels. The graph in Figure 9 shows the effect on total DAC8512 supply current as a function of the actua ...

$doc.title

... 2. This is the increase in supply current for each input at VCC –0.6V. 3. This parameter is valid for any VCC between 0V and 1.2V with a transition time of up to 10msec. From VCC = 1.2V to VCC = 3.3V ± 10% a transition time of 100µsec is permitted. This parameter is valid for Tamb = 25°C only. 4. Un ...

... 2. This is the increase in supply current for each input at VCC –0.6V. 3. This parameter is valid for any VCC between 0V and 1.2V with a transition time of up to 10msec. From VCC = 1.2V to VCC = 3.3V ± 10% a transition time of 100µsec is permitted. This parameter is valid for Tamb = 25°C only. 4. Un ...

PT2272

... otherwise, the address bits are compared with the address configuration of the pins. 3. Whenever the Address Bits in a Frame match with that of the Address Configuration of the Pin, the data bits are stored into the memory. Also, when this IC finds two (2) continuous and identical data having the sa ...

... otherwise, the address bits are compared with the address configuration of the pins. 3. Whenever the Address Bits in a Frame match with that of the Address Configuration of the Pin, the data bits are stored into the memory. Also, when this IC finds two (2) continuous and identical data having the sa ...

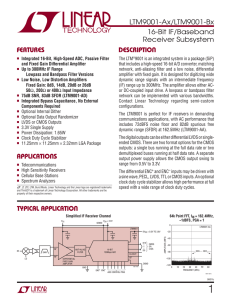

LTM9001-Ax/LTM9001-Bx - 16-Bit IF/Baseband Receiver Subsystem

... and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. ...

... and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. ...

MAX8633–MAX8636 Dual 300mA Pin-Programmable LDO Linear Regulators General Description

... inputs allow easy configuration of OUT1 and OUT2 voltages without external 1% resistors. The devices can supply up to 300mA from each output, provided they do not exceed the maximum package power dissipation. The MAX8633–MAX8636 regulate OUT1 and OUT2 by using simple control loops incorporating inte ...

... inputs allow easy configuration of OUT1 and OUT2 voltages without external 1% resistors. The devices can supply up to 300mA from each output, provided they do not exceed the maximum package power dissipation. The MAX8633–MAX8636 regulate OUT1 and OUT2 by using simple control loops incorporating inte ...

AD9762 Data Sheet

... differential output configuration. The current outputs may be tied directly to an output resistor to provide two complementary, single-ended voltage outputs or fed directly into a transformer. The output voltage compliance range is 1.25 V. The on-chip reference and control amplifier are configured f ...

... differential output configuration. The current outputs may be tied directly to an output resistor to provide two complementary, single-ended voltage outputs or fed directly into a transformer. The output voltage compliance range is 1.25 V. The on-chip reference and control amplifier are configured f ...

CLC5523 Low Power, Variable Gain Amplifier

... referred to as the S-curve, is the linear (V/V) gain. This is a hyperbolic tangent relationship. The second gain curve plots the gain in dB and is linear over a wide range of gains. Because of this, the CLC5523 gain control is referred to as “linear-in-dB.” For applications where the CLC5523 will be ...

... referred to as the S-curve, is the linear (V/V) gain. This is a hyperbolic tangent relationship. The second gain curve plots the gain in dB and is linear over a wide range of gains. Because of this, the CLC5523 gain control is referred to as “linear-in-dB.” For applications where the CLC5523 will be ...

14-Bit, 150 MSPS, 1.8 V Analog-to-Digital Converter AD9254

... analog-to-digital converter (ADC), featuring a high performance sample-and-hold amplifier (SHA) and on-chip voltage reference. The product uses a multistage differential pipeline architecture with output error correction logic to provide 14-bit accuracy at 150 MSPS data rates and guarantees no missi ...

... analog-to-digital converter (ADC), featuring a high performance sample-and-hold amplifier (SHA) and on-chip voltage reference. The product uses a multistage differential pipeline architecture with output error correction logic to provide 14-bit accuracy at 150 MSPS data rates and guarantees no missi ...

MAX5251 +3V, Quad, 10-Bit Voltage-Output DAC with Serial Interface __________________General Description

... (Figure 3). The serial input word consists of two address bits and two control bits followed by 10+2 data bits (MSB first), as shown in Figure 4. The 4-bit address/ control code determines the MAX5251’s response outlined in Table 1. The connection between DOUT and the serial-interface port is not ne ...

... (Figure 3). The serial input word consists of two address bits and two control bits followed by 10+2 data bits (MSB first), as shown in Figure 4. The 4-bit address/ control code determines the MAX5251’s response outlined in Table 1. The connection between DOUT and the serial-interface port is not ne ...

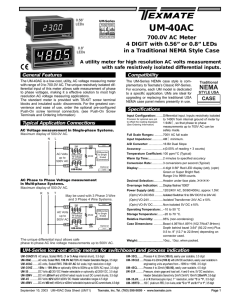

NEMA

... CN-PUSH/UM04 . Connector: Push-on Terminal Block, 9 to 36VDC/12 to 24 V AC $18 CN-PUSH/UM05 . Connector: Push-on Terminal Block, 5V DC . . . . . . . . . . . . . . . $18 CN-UM/ANLGC . . Connector: Pinout Changer to match Analogic AN20M02 etc . . $30 OP-N4SEAL/UM . NEMA 4 lens cover for UM Series mete ...

... CN-PUSH/UM04 . Connector: Push-on Terminal Block, 9 to 36VDC/12 to 24 V AC $18 CN-PUSH/UM05 . Connector: Push-on Terminal Block, 5V DC . . . . . . . . . . . . . . . $18 CN-UM/ANLGC . . Connector: Pinout Changer to match Analogic AN20M02 etc . . $30 OP-N4SEAL/UM . NEMA 4 lens cover for UM Series mete ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.