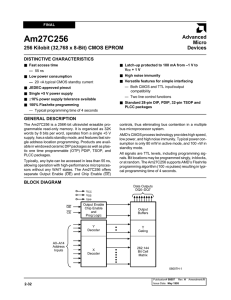

Am27C256

... ± 0.25 V is applied to the VPP pin, OE is at VIH, and CE is at VIL. For programming, the data to be programmed is applied 8 bits in parallel to the data output pins. The Flashrite algorithm reduces programming time by using 100 µs programming pulses and by giving each address only as many pulses as ...

... ± 0.25 V is applied to the VPP pin, OE is at VIH, and CE is at VIL. For programming, the data to be programmed is applied 8 bits in parallel to the data output pins. The Flashrite algorithm reduces programming time by using 100 µs programming pulses and by giving each address only as many pulses as ...

Low-Power, Current Feedback Operational Amplifier With Disable

... The output capability of the OPA684 also sets a new mark in performance for low-power current feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA684 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is complemented by ...

... The output capability of the OPA684 also sets a new mark in performance for low-power current feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA684 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is complemented by ...

ONET8531T 数据资料 dataSheet 下载

... capacitance is 0.2 pF and the bond-wire inductance is 0.3 nH. The small signal bandwidth strongly depends on environmental parasitics. Careful attention to layout parasitics and external components is necessary to achieve optimal performance. Input referred RMS noise = (RMS output noise) ÷ (gain at ...

... capacitance is 0.2 pF and the bond-wire inductance is 0.3 nH. The small signal bandwidth strongly depends on environmental parasitics. Careful attention to layout parasitics and external components is necessary to achieve optimal performance. Input referred RMS noise = (RMS output noise) ÷ (gain at ...

BD95514MUV

... The BD95514MUV controls the duty cycle and output voltage based upon the input voltage at this pin, so voltage variations or oscillations on this line can cause operation to become unstable. This pin also acts as the voltage input for the switching block, so insufficient coupling impedance can also ...

... The BD95514MUV controls the duty cycle and output voltage based upon the input voltage at this pin, so voltage variations or oscillations on this line can cause operation to become unstable. This pin also acts as the voltage input for the switching block, so insufficient coupling impedance can also ...

AD9744 数据手册DataSheet 下载

... Edits to Features.................................................................................1 Edits to Product Highlights..............................................................1 Edits to DC Specifications................................................................2 Edits to Dynamic ...

... Edits to Features.................................................................................1 Edits to Product Highlights..............................................................1 Edits to DC Specifications................................................................2 Edits to Dynamic ...

Op-Amp Voltage Amplifiers Word Document

... Voltage gain can be determined if either VOUT and VIN are known or if RF and RIN are known. The ‘-‘ sign in the formula indicates the inverting action of this amplifier, so at any moment if the input voltage is positive, the output will be negative, and vice versa. If you are designing an amplifier ...

... Voltage gain can be determined if either VOUT and VIN are known or if RF and RIN are known. The ‘-‘ sign in the formula indicates the inverting action of this amplifier, so at any moment if the input voltage is positive, the output will be negative, and vice versa. If you are designing an amplifier ...

GAIN +4 STABLE WIDEBAND VOLTAGE LIMITING AMPLIFIER OPA699M FEATURES APPLICATIONS

... gains ≥ +4. Two buffered limiting voltages take control of the output when it attempts to drive beyond these limits. This new output limiting architecture holds the limiter offset error to ±15 mV. The op amp operates linearly to within 30 mV of the limits. The combination of narrow nonlinear range a ...

... gains ≥ +4. Two buffered limiting voltages take control of the output when it attempts to drive beyond these limits. This new output limiting architecture holds the limiter offset error to ±15 mV. The op amp operates linearly to within 30 mV of the limits. The combination of narrow nonlinear range a ...

MAX197 Multi-Range (±10V, ±5V, +10V, +5V), _______________General Description

... impedance input source, which settles in less than 1.5µs, is required to maintain conversion accuracy at the maximum conversion rate. In the external acquisition control mode (D5 = 1), the T/H enters its tracking mode on the first WR rising edge and enters its hold mode when it detects the second WR ...

... impedance input source, which settles in less than 1.5µs, is required to maintain conversion accuracy at the maximum conversion rate. In the external acquisition control mode (D5 = 1), the T/H enters its tracking mode on the first WR rising edge and enters its hold mode when it detects the second WR ...

New Topology of a Three Phase Dynamic Voltage Restorer (DVR

... system has been considered with the load is represented by a series equivalent rated at 415Vrms, 5KVA at 0.95 load power factor. Simulation and experimental parameters are given in Table 1.The performance of the DVR for different supply disturbances is tested under various operating conditions. Seve ...

... system has been considered with the load is represented by a series equivalent rated at 415Vrms, 5KVA at 0.95 load power factor. Simulation and experimental parameters are given in Table 1.The performance of the DVR for different supply disturbances is tested under various operating conditions. Seve ...

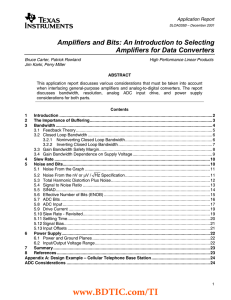

Amplifiers and Bits: An Introduction to Selecting Amplifiers for Data Converters

... The closed loop gain modifies the open loop gain A by 1+Aβ. Because logarithms are being used, divisions can be accomplished by subtraction of the quantities. Therefore, at low frequencies before the internal compensation break point, the closed loop gain in the figure above is 110 dB – 70 dB, or 40 ...

... The closed loop gain modifies the open loop gain A by 1+Aβ. Because logarithms are being used, divisions can be accomplished by subtraction of the quantities. Therefore, at low frequencies before the internal compensation break point, the closed loop gain in the figure above is 110 dB – 70 dB, or 40 ...

Test method to measure the surface voltages created on

... garment surface and charge on it couples more closely to the fieldmeter than the charge transferred to the garment surface. This brief pulse is of opposite polarity to the following excursion that leads into the slow decay of surface voltage as charge dissipates over the garment surface. An example ...

... garment surface and charge on it couples more closely to the fieldmeter than the charge transferred to the garment surface. This brief pulse is of opposite polarity to the following excursion that leads into the slow decay of surface voltage as charge dissipates over the garment surface. An example ...

Understanding Pipelined ADCs - Tutorial - Maxim

... interstage gain amplifiers, and thus significant linear settling time. A purely flash ADC, however, has a large bank of comparators, each consisting of wideband, low-gain preamps followed by a latch. The preamps, unlike those amplifiers in a pipelined ADC, must provide gains that do not need to be l ...

... interstage gain amplifiers, and thus significant linear settling time. A purely flash ADC, however, has a large bank of comparators, each consisting of wideband, low-gain preamps followed by a latch. The preamps, unlike those amplifiers in a pipelined ADC, must provide gains that do not need to be l ...

MAX8758 Step-Up Regulator with Switch Control and Operational Amplifier for TFT LCD

... transistor (TFT) liquid-crystal display (LCD) applications. The step-up DC-DC regulator provides the regulated supply voltage for the panel source driver ICs. The converter is a high-frequency (640kHz/1.2MHz), current-mode regulator with an integrated 14V n-channel power MOSFET. The high-switching f ...

... transistor (TFT) liquid-crystal display (LCD) applications. The step-up DC-DC regulator provides the regulated supply voltage for the panel source driver ICs. The converter is a high-frequency (640kHz/1.2MHz), current-mode regulator with an integrated 14V n-channel power MOSFET. The high-switching f ...

UCC28730 Constant-Voltage, Constant-Current

... turn-off time. An internal leading-edge blanking time of 225 ns eliminates sensitivity to the MOSFET turn-on current spike. It should not be necessary to place a bypass capacitor on the CS pin. The target output current in constant-current (CC) regulation determines the value of RCS. The values of R ...

... turn-off time. An internal leading-edge blanking time of 225 ns eliminates sensitivity to the MOSFET turn-on current spike. It should not be necessary to place a bypass capacitor on the CS pin. The target output current in constant-current (CC) regulation determines the value of RCS. The values of R ...

A 6.25 Gb/s Voltage-Time Conversion Based Fractionally Spaced

... To alleviate these effects, we have recently proposed in [11] circuits and systems techniques that customize fractionally spaced equalizers [12] for high-speed link receivers, integrating ISI reduction and phase synchronization into a single control loop. A typical receive symbol-spaced equalization ...

... To alleviate these effects, we have recently proposed in [11] circuits and systems techniques that customize fractionally spaced equalizers [12] for high-speed link receivers, integrating ISI reduction and phase synchronization into a single control loop. A typical receive symbol-spaced equalization ...

High-Efficiency, 8A, Current-Mode Synchronous Step-Down Switching Regulator MAX15108 General Description Features

... to reduce current consumption and achieve a higher efficiency at light output load. The low RDS(ON) integrated switches ensure high efficiency at heavy loads while minimizing critical inductance, making the layout design a much simpler task with respect to discrete solutions. The IC’s simple layout ...

... to reduce current consumption and achieve a higher efficiency at light output load. The low RDS(ON) integrated switches ensure high efficiency at heavy loads while minimizing critical inductance, making the layout design a much simpler task with respect to discrete solutions. The IC’s simple layout ...

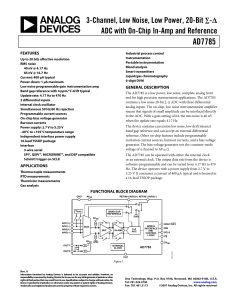

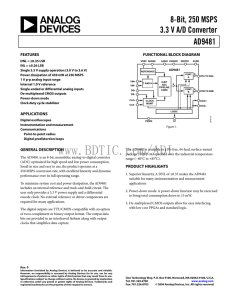

8-Bit, 250 MSPS 3.3 V A/D Converter AD9481

... input port. The resistance is measured statically and the capacitance and differential input impedances are measured with a network analyzer. Differential Analog Input Voltage Range The peak-to-peak differential voltage that must be applied to the converter to generate a full-scale response. Peak di ...

... input port. The resistance is measured statically and the capacitance and differential input impedances are measured with a network analyzer. Differential Analog Input Voltage Range The peak-to-peak differential voltage that must be applied to the converter to generate a full-scale response. Peak di ...

Op Amp Applications - 3DSCO Global Connection

... Determine resistor values by using color code. Evaluate a basic circuit and determine wither it is series, or parallel or seriesparallel. Learn to apply Thevenins Theorem to series-parallel circuits. Know and understand Ohm’s Law. ...

... Determine resistor values by using color code. Evaluate a basic circuit and determine wither it is series, or parallel or seriesparallel. Learn to apply Thevenins Theorem to series-parallel circuits. Know and understand Ohm’s Law. ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.