First Year Laboratory Scripts MODULE I

... instruments and there would be no time for investigating interesting physics if we spent time training you in the detailed use of each individual piece of equipment. Instead what we intend to do is to train you in the use of instruments in general and the approach you should adopt when handling any ...

... instruments and there would be no time for investigating interesting physics if we spent time training you in the detailed use of each individual piece of equipment. Instead what we intend to do is to train you in the use of instruments in general and the approach you should adopt when handling any ...

Hardware Error Rate Characterization with Below

... voltage (Vdd ) reduces power consumption at a quadratic rate, at the expense of some timing errors. Prior research shows that every large CMOS chip has two voltage operating points: the rated voltage point and the critical voltage point [4, 5]. This leads to three operating regions for the processor ...

... voltage (Vdd ) reduces power consumption at a quadratic rate, at the expense of some timing errors. Prior research shows that every large CMOS chip has two voltage operating points: the rated voltage point and the critical voltage point [4, 5]. This leads to three operating regions for the processor ...

First Year Physics Laboratory

... notes refer to the situation as it exists at the time of writing, but the organisational details and the experiments on offer may be changed at short notice. You should watch the notice board and look for any handouts about differences. During the first semester, all students except those following ...

... notes refer to the situation as it exists at the time of writing, but the organisational details and the experiments on offer may be changed at short notice. You should watch the notice board and look for any handouts about differences. During the first semester, all students except those following ...

BU6904NUX - uri=media.digikey

... Back electromotive force causes regenerated current to power supply line, therefore take a measure such as placing a capacitor between power supply and GND for routing regenerated current. And fully ensure that the capacitor characteristics have no problem before determine a capacitor value. (when a ...

... Back electromotive force causes regenerated current to power supply line, therefore take a measure such as placing a capacitor between power supply and GND for routing regenerated current. And fully ensure that the capacitor characteristics have no problem before determine a capacitor value. (when a ...

Secong Order Circuit

... The time constant of a circuit is the time required for the response to decay by a factor of 1/e or 36.8% of its initial value. i(t) decays faster for small and slower for large . The general form is very similar to a RC source-free circuit. ...

... The time constant of a circuit is the time required for the response to decay by a factor of 1/e or 36.8% of its initial value. i(t) decays faster for small and slower for large . The general form is very similar to a RC source-free circuit. ...

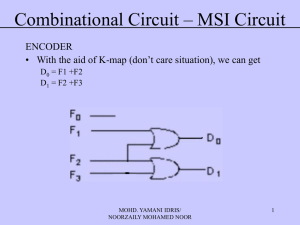

Kuliah 3(a) - FCSIT @ UM

... The steps: Get TT, take its input as address and output as data • Advantage: Boolean function is executed directly • Disadvantage: Didn't use the “don’t care” and variable input numbers is limited (e.g. 10 input – 1K, 16 input – 64K, 20 input – 1M) MOHD. YAMANI IDRIS/ NOORZAILY MOHAMED NOOR ...

... The steps: Get TT, take its input as address and output as data • Advantage: Boolean function is executed directly • Disadvantage: Didn't use the “don’t care” and variable input numbers is limited (e.g. 10 input – 1K, 16 input – 64K, 20 input – 1M) MOHD. YAMANI IDRIS/ NOORZAILY MOHAMED NOOR ...

Circuits

... In an electric circuit, fuses and circuit breakers act as safety devices. They prevent circuit overloads that can occur when too many appliances are turned on at the same time or when a short circuit occurs in one appliance. A short circuit occurs when a circuit with very low resistance is formed. T ...

... In an electric circuit, fuses and circuit breakers act as safety devices. They prevent circuit overloads that can occur when too many appliances are turned on at the same time or when a short circuit occurs in one appliance. A short circuit occurs when a circuit with very low resistance is formed. T ...

EECE251 Circuit Analysis I Set 4 - UBC ECE

... alarm clocks. Let's assume that such a clock's internal digital hardware requires a current of 1 mA at a typical voltage level of 3.0 V, but the hardware will function properly down to 2.4 V. Under these assumptions, we wish to design a circuit that will “hold” the voltage level for a short duration ...

... alarm clocks. Let's assume that such a clock's internal digital hardware requires a current of 1 mA at a typical voltage level of 3.0 V, but the hardware will function properly down to 2.4 V. Under these assumptions, we wish to design a circuit that will “hold” the voltage level for a short duration ...

ECE 2006 - Lecture 2

... transient behavior of basic RC and RL pairs. However, we must first state two important rules that will greatly facilitate our transient analysis of these circuits. Instantaneous Behavior: The Continuity Conditions Capacitance current and voltage are related as ic = C dvc/dt. The faster the change i ...

... transient behavior of basic RC and RL pairs. However, we must first state two important rules that will greatly facilitate our transient analysis of these circuits. Instantaneous Behavior: The Continuity Conditions Capacitance current and voltage are related as ic = C dvc/dt. The faster the change i ...

1 - Concordia University

... Consider the circuit of Figure 5. During the precharge phase, the output node is precharged to VDD. Capacitors Ca and Cb represent the parasitic capacitances of the internal nodes of the circuit. Assume now that during precharge all inputs are set 0 and the capacitance Ca is discharged. Assume furth ...

... Consider the circuit of Figure 5. During the precharge phase, the output node is precharged to VDD. Capacitors Ca and Cb represent the parasitic capacitances of the internal nodes of the circuit. Assume now that during precharge all inputs are set 0 and the capacitance Ca is discharged. Assume furth ...

High-speed CMOS circuit technique - Solid

... both are in the evaluation phase as shown in Fig. 10. Locally, this is not a problem because the clock delay is usually less than the gate delay. In a pure pipeline structure the condition between the clock delay and the data delay is still satisfactory. In the case of a large system, we propose two ...

... both are in the evaluation phase as shown in Fig. 10. Locally, this is not a problem because the clock delay is usually less than the gate delay. In a pure pipeline structure the condition between the clock delay and the data delay is still satisfactory. In the case of a large system, we propose two ...

Programmable Membership Function Circuits Using Analog MOS

... Abstract – Analog fuzzy controller circuit design for control applications is presented in this paper. The analog fuzzy logic controller (FLC) consists of three main cells: Membership function circuits (MFC), fuzzy inference circuit (FIC) and defuzzification circuit (DFC). The MFC has function to fu ...

... Abstract – Analog fuzzy controller circuit design for control applications is presented in this paper. The analog fuzzy logic controller (FLC) consists of three main cells: Membership function circuits (MFC), fuzzy inference circuit (FIC) and defuzzification circuit (DFC). The MFC has function to fu ...

Error Probability for M Signals

... involved in the expression in all but a few special cases is very difficult or impossible if N is fairly large (e.g. N 4). For the special case of orthogonal signals in the last chapter we derived the error probability as a single integral. Because of the difficulty of evaluating the error probabili ...

... involved in the expression in all but a few special cases is very difficult or impossible if N is fairly large (e.g. N 4). For the special case of orthogonal signals in the last chapter we derived the error probability as a single integral. Because of the difficulty of evaluating the error probabili ...

Chapter 6

... makes the dynamic circuit sensitive to crosstalk effect ( A wire routed over or close to a dynamic node may couple capacitively and destroy the state of the node) The other equally important form of capacitive coupling is called backgate coupling (input coupled to ...

... makes the dynamic circuit sensitive to crosstalk effect ( A wire routed over or close to a dynamic node may couple capacitively and destroy the state of the node) The other equally important form of capacitive coupling is called backgate coupling (input coupled to ...

DAC161P997 Single-Wire 16-bit DAC for 4

... The DAC161P997 is a 16-bit DAC realized as a ∑Δ modulator. The DAC’s output is a current pulse train that is filtered by the on-board low pass RC filter. The final output current is a multiplied copy of the filtered modulator output. This architecture ensures an excellent linearity performance, whil ...

... The DAC161P997 is a 16-bit DAC realized as a ∑Δ modulator. The DAC’s output is a current pulse train that is filtered by the on-board low pass RC filter. The final output current is a multiplied copy of the filtered modulator output. This architecture ensures an excellent linearity performance, whil ...

1 - Concordia University

... capacitances where the state of the input and output nodes are determined by the presence of charges on the capacitances of these nodes. This makes the dynamic gate very prone to noise and capacitive coupling during evaluation phase, and may result in a less robust circuit. Aside from these, we must ...

... capacitances where the state of the input and output nodes are determined by the presence of charges on the capacitances of these nodes. This makes the dynamic gate very prone to noise and capacitive coupling during evaluation phase, and may result in a less robust circuit. Aside from these, we must ...

W

... capacitances where the state of the input and output nodes are determined by the presence of charges on the capacitances of these nodes. This makes the dynamic gate very prone to noise and capacitive coupling during evaluation phase, and may result in a less robust circuit. Aside from these, we must ...

... capacitances where the state of the input and output nodes are determined by the presence of charges on the capacitances of these nodes. This makes the dynamic gate very prone to noise and capacitive coupling during evaluation phase, and may result in a less robust circuit. Aside from these, we must ...

A 256-kb 65-nm Sub-threshold SRAM Design for Ultra-Low

... are available [5] along with software policies to determine when to enter the lower leakage mode [2]. Voltage scaling for SRAM promises to continue, leading to sub-threshold storage modes and even sub-threshold operation for SRAMs operating in tandem with sub-threshold logic. One issue for deeply vo ...

... are available [5] along with software policies to determine when to enter the lower leakage mode [2]. Voltage scaling for SRAM promises to continue, leading to sub-threshold storage modes and even sub-threshold operation for SRAMs operating in tandem with sub-threshold logic. One issue for deeply vo ...

View File

... • Essential requirement to design PTL circuit is to ensure that every ckt node has at all times a low-resistance path to VDD or ground. Switch S1 is used to form AND Function of its controlling variable B and variable A at the CMOS inverter output. Y of PTL is connected to input of another inverter. ...

... • Essential requirement to design PTL circuit is to ensure that every ckt node has at all times a low-resistance path to VDD or ground. Switch S1 is used to form AND Function of its controlling variable B and variable A at the CMOS inverter output. Y of PTL is connected to input of another inverter. ...

CMOS Layout Design and Performance Analysis for

... The propagation delay of sequential circuits is the sum of propagation delay of master and slave logic during transparency. When the metastable failure occurs in master latch, it will increase its propagation. If one flip-flop in sequential circuits becomes metastable and produces a transition propa ...

... The propagation delay of sequential circuits is the sum of propagation delay of master and slave logic during transparency. When the metastable failure occurs in master latch, it will increase its propagation. If one flip-flop in sequential circuits becomes metastable and produces a transition propa ...

IOSR Journal of Computer Engineering (IOSR-JCE) e-ISSN: 2278-0661, p-ISSN: 2278-8727 PP 29-36 www.iosrjournals.org

... the amount of hardware required in the circuit. The output duty cycle is calculated with the help of a new duty cycle setting circuit without the need for a look-up table. The new design is developed in Hardware description language (HDL) to improve the design effort. The pulsewidth-control circuit ...

... the amount of hardware required in the circuit. The output duty cycle is calculated with the help of a new duty cycle setting circuit without the need for a look-up table. The new design is developed in Hardware description language (HDL) to improve the design effort. The pulsewidth-control circuit ...

ET304a Laboratory 5 Thevenin`s and Norton`s Theorem and the

... the open circuit voltage and short circuit currents of the test circuits. Use the principle of superposition along with Thenvenin's and Norton's theorems to reduce complex circuits to simple voltage and current source models. Compute the theoretical equivalents and compare them to the experimental e ...

... the open circuit voltage and short circuit currents of the test circuits. Use the principle of superposition along with Thenvenin's and Norton's theorems to reduce complex circuits to simple voltage and current source models. Compute the theoretical equivalents and compare them to the experimental e ...

Latest Placement Papers for your Dream Concern Eye shot of ABB

... (a)less than 50 (b)more than 60(c)in between 50 & 60 (d)none..........according to our conclusion answer will be none because if we apply two frequency component resultatnt frequency we can not say with such an ease.U should confirm the answer 2.In a ckt a single resistor is connected across a d.c. ...

... (a)less than 50 (b)more than 60(c)in between 50 & 60 (d)none..........according to our conclusion answer will be none because if we apply two frequency component resultatnt frequency we can not say with such an ease.U should confirm the answer 2.In a ckt a single resistor is connected across a d.c. ...

New Floating Capacitance Multipliers

... 1. Introduction One of the most limiting problems in the design of integrated circuits is constituted by the realization of silicon area. Moreover, in some sensor applications, it can be useful to deal with capacitance value higher than those normally given by capacitive sensors. In these cases, the ...

... 1. Introduction One of the most limiting problems in the design of integrated circuits is constituted by the realization of silicon area. Moreover, in some sensor applications, it can be useful to deal with capacitance value higher than those normally given by capacitive sensors. In these cases, the ...

A) Resistance, Voltage and Current Measurement using Analog

... during experiment; decide on the suitability of measurement. Safety first ~ Take care: electric shock, overload effect, limitation of instrument. Sampling ~ See the changing of parameter during measurement, which value should be taken when the parameter keeps on changing. Take enough samples till it ...

... during experiment; decide on the suitability of measurement. Safety first ~ Take care: electric shock, overload effect, limitation of instrument. Sampling ~ See the changing of parameter during measurement, which value should be taken when the parameter keeps on changing. Take enough samples till it ...