Flip-Flop Circuits

... depending on the current output. A simple example is a counter, where the next number to be output is determined by the current number stored. Circuits that remember their current output or state are often called sequential logic circuits. Clearly, sequential logic requires the ability to store the ...

... depending on the current output. A simple example is a counter, where the next number to be output is determined by the current number stored. Circuits that remember their current output or state are often called sequential logic circuits. Clearly, sequential logic requires the ability to store the ...

IC Temp Sensor Provides Thermocouple Cold

... provide a voltage to buck out the 0°C output of the LM335. To calibrate, adjust R1 so that V1 = <5°C T, where <5°C is the Seebeck coefficient and T is the ambient temperature in degrees Kelvin. Then, adjust R2 so that V1−V2 is equal to the thermocouple output voltage at the known ambient temperature ...

... provide a voltage to buck out the 0°C output of the LM335. To calibrate, adjust R1 so that V1 = <5°C T, where <5°C is the Seebeck coefficient and T is the ambient temperature in degrees Kelvin. Then, adjust R2 so that V1−V2 is equal to the thermocouple output voltage at the known ambient temperature ...

DATASHEET SEARCH SITE == WWW.ICPDF.COM

... 2-kΩ, 200-pF load rail-to-rail with 5-µs settling time; the output range is set using an external voltage reference. The 3-wire serial interface operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire™, and DSP interface standards. The outputs of all DACs may be updated simu ...

... 2-kΩ, 200-pF load rail-to-rail with 5-µs settling time; the output range is set using an external voltage reference. The 3-wire serial interface operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire™, and DSP interface standards. The outputs of all DACs may be updated simu ...

DAC7558 - Texas Instruments

... 2-kΩ, 200-pF load rail-to-rail with 5-µs settling time; the output range is set using an external voltage reference. The 3-wire serial interface operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire™, and DSP interface standards. The outputs of all DACs may be updated simu ...

... 2-kΩ, 200-pF load rail-to-rail with 5-µs settling time; the output range is set using an external voltage reference. The 3-wire serial interface operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire™, and DSP interface standards. The outputs of all DACs may be updated simu ...

Make a Delta-Sigma Converter Using a Microcontroller`s

... of the delta-sigma function is implemented with an external capacitor, CINT. The absolute accuracy of this external capacitor is not critical, only its stability from integration to integration, which occurs in a relatively short period of time. When RA3 of the PIC16C6XX is set high, the voltage at ...

... of the delta-sigma function is implemented with an external capacitor, CINT. The absolute accuracy of this external capacitor is not critical, only its stability from integration to integration, which occurs in a relatively short period of time. When RA3 of the PIC16C6XX is set high, the voltage at ...

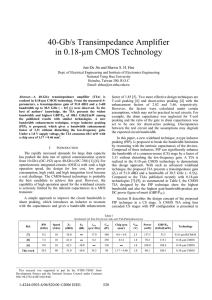

40-Gb/s Transimpedance Amplifier in 0.18

... The concept of PIP design technique is illustrated by a CS stage first in this section, which is the fundamental building block and will be applied directly to the proposed wideband TIA using a four-stage cascade configuration. Fig. 1 shows a simplified small-signal equivalent circuit model of a CS ...

... The concept of PIP design technique is illustrated by a CS stage first in this section, which is the fundamental building block and will be applied directly to the proposed wideband TIA using a four-stage cascade configuration. Fig. 1 shows a simplified small-signal equivalent circuit model of a CS ...

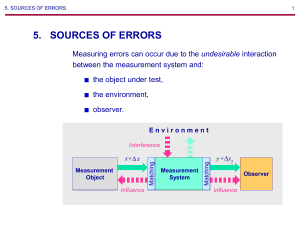

Measurement Theory Principles

... high-frequency measurement signals along transmission lines. If a transmission line is not terminated characteristically, reflections off the ends of the line will cause standing waves on the line; the line output signal is no longer a good measure for the line input ...

... high-frequency measurement signals along transmission lines. If a transmission line is not terminated characteristically, reflections off the ends of the line will cause standing waves on the line; the line output signal is no longer a good measure for the line input ...

Data Converter Fundamentals

... Monotonic D/A Converters • Where output alway increases as input increases — no negative slope in transfer-response • Important for some control loop applications • If max DNL < 1 LSB, converter is monotonic • Can be monotonic and have DNL > 1 LSB • If max INL < 0.5 LSB, converter is monotonic Missi ...

... Monotonic D/A Converters • Where output alway increases as input increases — no negative slope in transfer-response • Important for some control loop applications • If max DNL < 1 LSB, converter is monotonic • Can be monotonic and have DNL > 1 LSB • If max INL < 0.5 LSB, converter is monotonic Missi ...

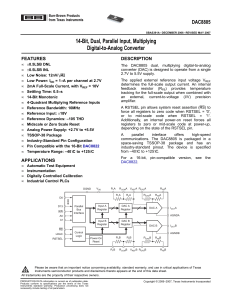

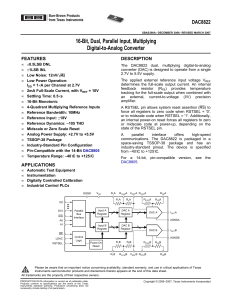

14-Bit, Dual, Parallel Input, Multiplying Digital-to

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... Design style is static through the use of static CMOS and static TG gates. TG can have are able to lower down power supply VDD from the nominal value because PMOS and NMOS devices are both used, hence there is full-logic swing [9]. Minimization of area is possible with TG gates because they can be m ...

... Design style is static through the use of static CMOS and static TG gates. TG can have are able to lower down power supply VDD from the nominal value because PMOS and NMOS devices are both used, hence there is full-logic swing [9]. Minimization of area is possible with TG gates because they can be m ...

LEM`s new class of Rogowski coil split

... are slightly different because at the sensor output we find that the voltage is in proportion, not to the primary current, but rather to its derivative: U = M*di/dt. M is the mutual inductance between the primary conductor and the coil, which to some extent represents the coupling between the primar ...

... are slightly different because at the sensor output we find that the voltage is in proportion, not to the primary current, but rather to its derivative: U = M*di/dt. M is the mutual inductance between the primary conductor and the coil, which to some extent represents the coupling between the primar ...

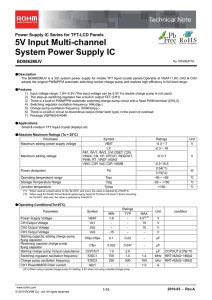

BD9862MUV

... raised by controlling and making the lowest On Duty of PWM signal to be 7%(typ.) and reducing the number of switching times. ・LDO Block This is a power supply to operate the internal circuit. In addition, it can be used as input of VIN2B. The output voltage is 3.5V(typ.), and the maximum load is 10m ...

... raised by controlling and making the lowest On Duty of PWM signal to be 7%(typ.) and reducing the number of switching times. ・LDO Block This is a power supply to operate the internal circuit. In addition, it can be used as input of VIN2B. The output voltage is 3.5V(typ.), and the maximum load is 10m ...

Dual, Parallel Input, 16-Bit, Multiplying Digital-to

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

Low Power Fir Filter Design Using Truncated Multiplier A.Deepika , A.Bhuvaneswari

... widely used in digital signal applications such as speech coding, image processing, sampling of multiple systems, etc. Although the stability and linear phase is guaranteed, the complexity and power consumption of the linear phase FIR filter are usually much higher than that of the infinite impulse ...

... widely used in digital signal applications such as speech coding, image processing, sampling of multiple systems, etc. Although the stability and linear phase is guaranteed, the complexity and power consumption of the linear phase FIR filter are usually much higher than that of the infinite impulse ...

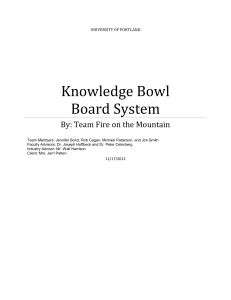

Design Document V1.1 - University of Portland

... Figure 1 shows the block diagram of the Knowledge Bowl System and how each component will interact. The main components are the administrator controller, player controllers, logic unit, and display. The administrator controller contains the reset and clear buttons. The reset button resets the clock ...

... Figure 1 shows the block diagram of the Knowledge Bowl System and how each component will interact. The main components are the administrator controller, player controllers, logic unit, and display. The administrator controller contains the reset and clear buttons. The reset button resets the clock ...

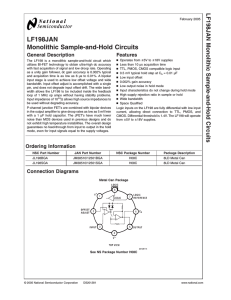

LF198JAN Monolithic Sample-and-Hold Circuits Monolithic General Description

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

final bxamination

... An output voltage of a transformer show 20 Vp-p if it is measured using an Oscilloscope. Determine the output voltage of transformer if it is measured using AC Voltmeter. (3 marks) ...

... An output voltage of a transformer show 20 Vp-p if it is measured using an Oscilloscope. Determine the output voltage of transformer if it is measured using AC Voltmeter. (3 marks) ...

Figure.1. 16-Transistor full adder circuit [2]

... being motivated by three basic design goals, viz. minimizing the transistor count, minimizing the power consumption and increasing the speed, [4].Most of the VLSI applications, such as digital-signal processing and microprocessors, use arithmetic operation. Addition, subtraction, multiplication, and ...

... being motivated by three basic design goals, viz. minimizing the transistor count, minimizing the power consumption and increasing the speed, [4].Most of the VLSI applications, such as digital-signal processing and microprocessors, use arithmetic operation. Addition, subtraction, multiplication, and ...

+ – Series Circuits - Eleanor Roosevelt High School

... Voltage drop for the device decreases, the total current is decreased, resistance is increased ...

... Voltage drop for the device decreases, the total current is decreased, resistance is increased ...

Worst-case design of op amp circuits

... Capacitor tolerances, while not discussed in detail here, are handled in the same manner. Capacitor tolerances vary much more than resistor tolerances because of the radically different methods used to manufacture capacitors. Electrolytic capacitors often have purchase tolerances of +80, –20%; but s ...

... Capacitor tolerances, while not discussed in detail here, are handled in the same manner. Capacitor tolerances vary much more than resistor tolerances because of the radically different methods used to manufacture capacitors. Electrolytic capacitors often have purchase tolerances of +80, –20%; but s ...

APPLICATION BULLETIN

... Gain A in this expression contains the frequency dependence that shapes the circuit’s frequency response. Note that the denominator of this response contains the feedback factor Z1/(Z1 + Z2). This makes the denominator 1 + Aβ and this relates the circuit to the model presented next. To more complete ...

... Gain A in this expression contains the frequency dependence that shapes the circuit’s frequency response. Note that the denominator of this response contains the feedback factor Z1/(Z1 + Z2). This makes the denominator 1 + Aβ and this relates the circuit to the model presented next. To more complete ...

ATTACHMENT 11 Exelon Generation Company, LLC Calculation L-003445, “Core Thermal Power

... equipment by a ratio of at least 4:1 such that calibration standard errors can be considered negligible with respect to the M&TE specifications. This is considered a reasonable assumption since M&TE equipment is typically certified to its required accuracy under laboratory conditions using instrumen ...

... equipment by a ratio of at least 4:1 such that calibration standard errors can be considered negligible with respect to the M&TE specifications. This is considered a reasonable assumption since M&TE equipment is typically certified to its required accuracy under laboratory conditions using instrumen ...

Op Amp Performance Analysis

... Gain A in this expression contains the frequency dependence that shapes the circuit’s frequency response. Note that the denominator of this response contains the feedback factor Z1/(Z1 + Z2). This makes the denominator 1 + Aβ and this relates the circuit to the model presented next. To more complete ...

... Gain A in this expression contains the frequency dependence that shapes the circuit’s frequency response. Note that the denominator of this response contains the feedback factor Z1/(Z1 + Z2). This makes the denominator 1 + Aβ and this relates the circuit to the model presented next. To more complete ...

Backward Secondary-Wave Coherence Errors in Photonic Bandgap

... magnitudes (only about 3–10 times smaller than that of primary waves for a 300-m coil composed of 3–10 times smaller than that of primary waves for a 300-m coil composed of a PBF with a loss of a PBF with a loss of 20 dB/km). Obviously, those back-reflection-induced secondary waves produce 20 dB/km) ...

... magnitudes (only about 3–10 times smaller than that of primary waves for a 300-m coil composed of 3–10 times smaller than that of primary waves for a 300-m coil composed of a PBF with a loss of a PBF with a loss of 20 dB/km). Obviously, those back-reflection-induced secondary waves produce 20 dB/km) ...

A Case For Teaching Mixed Logic In Digital Design

... To understand mixed logic, the concepts of positive and negative logic and assertion levels must first be defined. Positive logic is defined as a high voltage level representing a logic 1 and a low voltage level representing a logic 0. Negative logic is the reverse, i.e., a low voltage level represe ...

... To understand mixed logic, the concepts of positive and negative logic and assertion levels must first be defined. Positive logic is defined as a high voltage level representing a logic 1 and a low voltage level representing a logic 0. Negative logic is the reverse, i.e., a low voltage level represe ...

![Figure.1. 16-Transistor full adder circuit [2]](http://s1.studyres.com/store/data/001255487_1-858a4a45c9148a769c8279528fccbe9b-300x300.png)