MAX3291,92 - Part Number Search

... operate from a single +5V supply and offer a low-current shutdown mode that reduces supply current to 100nA. They feature driver output short-circuit current limiting and a fail-safe receiver input that guarantees a logic-high output if the input is open circuit. A 1/4-unitload receiver input impeda ...

... operate from a single +5V supply and offer a low-current shutdown mode that reduces supply current to 100nA. They feature driver output short-circuit current limiting and a fail-safe receiver input that guarantees a logic-high output if the input is open circuit. A 1/4-unitload receiver input impeda ...

OPA692 数据资料 dataSheet 下载

... The OPA692 provides an easy to use, broadband fixed gain video buffer amplifier. Depending on the external connections, the internal resistor network may be used to provide either a fixed gain of +2 video buffer or a gain of +1 or –1 voltage buffer. Operating on a very low 5.1mA supply current, the ...

... The OPA692 provides an easy to use, broadband fixed gain video buffer amplifier. Depending on the external connections, the internal resistor network may be used to provide either a fixed gain of +2 video buffer or a gain of +1 or –1 voltage buffer. Operating on a very low 5.1mA supply current, the ...

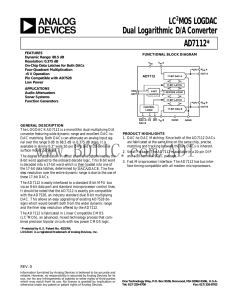

AD7112 数据手册DataSheet 下载

... Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any other digital grounds to this analog ground point. Low impedance analog and digital power supply common returns are essential for ...

... Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any other digital grounds to this analog ground point. Low impedance analog and digital power supply common returns are essential for ...

Single-Supply, High-Speed, Precision

... (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. (2) ...

... (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. (2) ...

BW n - TI E2E Community

... ROUT is the effect of RO, Aol, and β controlling VO – Closed Loop feedback (β) forces VO to increase or decrease as needed to accommodate VO loading – Closed Loop (β) increase or decrease in VO appears at VOUT as a reduction in RO – ROUT increases as Loop Gain (Aolβ) decreases ...

... ROUT is the effect of RO, Aol, and β controlling VO – Closed Loop feedback (β) forces VO to increase or decrease as needed to accommodate VO loading – Closed Loop (β) increase or decrease in VO appears at VOUT as a reduction in RO – ROUT increases as Loop Gain (Aolβ) decreases ...

TPS40200-HT 数据资料 dataSheet 下载

... external clock, RC must be pulled below 150 mV for 20 ns or more. The external clock frequency must be higher than the free-running frequency of the converter as well. When synchronizing the controller, if RC is held low for an excessive amount of time, erratic operation may occur. The maximum amoun ...

... external clock, RC must be pulled below 150 mV for 20 ns or more. The external clock frequency must be higher than the free-running frequency of the converter as well. When synchronizing the controller, if RC is held low for an excessive amount of time, erratic operation may occur. The maximum amoun ...

ONET8531T 数据资料 dataSheet 下载

... The ONET8531T is a high-speed and high-gain limiting-transimpedance amplifier, used in optical receivers with data rates up to 12.5 Gbps. It features low input referred noise, 10 GHz bandwidth, 4.5 kΩ small signal transimpedance, and a received signal strength indicator (RSSI). The ONET8531T is avai ...

... The ONET8531T is a high-speed and high-gain limiting-transimpedance amplifier, used in optical receivers with data rates up to 12.5 Gbps. It features low input referred noise, 10 GHz bandwidth, 4.5 kΩ small signal transimpedance, and a received signal strength indicator (RSSI). The ONET8531T is avai ...

NCP1631PFCGEVB Interleaved PFC Stage Driven by the NCP1631 Evaluation Board User's

... are combined to form our 300−W PFC pre−regulator. This approach has several merits like the ease of implementation, the use of more but smaller components or a better heat distribution. Also, Interleaving extends the power range of Critical Conduction Mode (CrM) that is an efficient and cost−effecti ...

... are combined to form our 300−W PFC pre−regulator. This approach has several merits like the ease of implementation, the use of more but smaller components or a better heat distribution. Also, Interleaving extends the power range of Critical Conduction Mode (CrM) that is an efficient and cost−effecti ...

CD74HCT4067-Q1 数据资料 dataSheet 下载

... Supply voltage range, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to +7 V Input clamp current, IIK (VI < −0.5 V or VI > VCC + 0.5 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA Output clamp curre ...

... Supply voltage range, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to +7 V Input clamp current, IIK (VI < −0.5 V or VI > VCC + 0.5 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA Output clamp curre ...

a 1.75 MSPS, 4 mW 10-Bit/12-Bit Parallel ADCs AD7470/AD7472

... DVDD to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V VDRIVE to AGND/DGND . . . . . . . . . . . . . . . . –0.3 V to +7 V AVDD to DVDD . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V VDRIVE to DVDD . . . . . . . . . . . . . . . –0.3 V to DVDD + 0.3 V AGND to DGND . . . . . . ...

... DVDD to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V VDRIVE to AGND/DGND . . . . . . . . . . . . . . . . –0.3 V to +7 V AVDD to DVDD . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V VDRIVE to DVDD . . . . . . . . . . . . . . . –0.3 V to DVDD + 0.3 V AGND to DGND . . . . . . ...

INA101 数据资料 dataSheet 下载

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

harmonic reduction in a single-switch three-phase

... range complicates boost inductor design, device selection, and EMI filter design. The second example [4] concerns an output low-frequency ripple (sixth-order) feedback control PWM. For a rectifier with a resistive load and fed by a balanced threephase AC power, the sixth-order output voltage ripple ...

... range complicates boost inductor design, device selection, and EMI filter design. The second example [4] concerns an output low-frequency ripple (sixth-order) feedback control PWM. For a rectifier with a resistive load and fed by a balanced threephase AC power, the sixth-order output voltage ripple ...