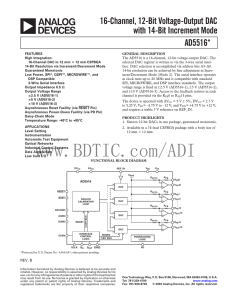

AD5516: 英文产品数据手册下载

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

OPA2677 Dual, Wideband, High Output Current Operational Amplifier FEATURES

... distortion. Differential driver applications will deliver < –85dBc distortion at the peak upstream power levels of full rate ADSL. The high 200MHz bandwidth will also support the most demanding VDSL line driver requirements. ...

... distortion. Differential driver applications will deliver < –85dBc distortion at the peak upstream power levels of full rate ADSL. The high 200MHz bandwidth will also support the most demanding VDSL line driver requirements. ...

MAX1700/MAX1701 1-Cell to 3-Cell, High-Power (1A), Low-Noise, Step-Up DC-DC Converters General Description

... regulator, N-channel power MOSFET, P-channel synchronous rectifier, precision reference, and shutdown control. The MAX1701 contains all of the MAX1700 features plus a versatile gain amplifier, POK output, and a low-battery comparator (Figure 1). The MAX1700/ MAX1701 come in a 16-pin QSOP package, wh ...

... regulator, N-channel power MOSFET, P-channel synchronous rectifier, precision reference, and shutdown control. The MAX1701 contains all of the MAX1700 features plus a versatile gain amplifier, POK output, and a low-battery comparator (Figure 1). The MAX1700/ MAX1701 come in a 16-pin QSOP package, wh ...

ADS1100 数据资料 dataSheet 下载

... however, that active buffers introduce noise, and also introduce offset and gain errors. All of these factors should be considered in high-accuracy applications. Because the clock oscillator frequency drifts slightly with temperature, the input impedances will also drift. For many applications, this ...

... however, that active buffers introduce noise, and also introduce offset and gain errors. All of these factors should be considered in high-accuracy applications. Because the clock oscillator frequency drifts slightly with temperature, the input impedances will also drift. For many applications, this ...

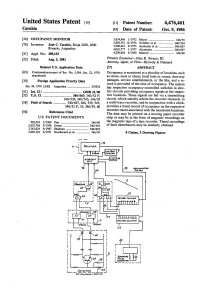

Occupancy monitor

... fault-controlled, sensor switch 22 which responds to the events which mark the beginning and the end of occu detection occurs, the printer 73 returns the detector identi?cation comparison pulses via a feedback line 70 pancy or of a fault condition. Switch 22 is connected in to said other decimal cou ...

... fault-controlled, sensor switch 22 which responds to the events which mark the beginning and the end of occu detection occurs, the printer 73 returns the detector identi?cation comparison pulses via a feedback line 70 pancy or of a fault condition. Switch 22 is connected in to said other decimal cou ...

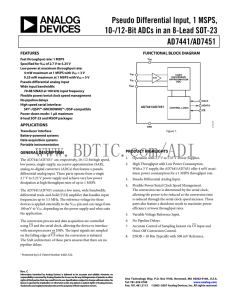

AD7441 数据手册DataSheet下载

... Reference Input for the AD7441/AD7451. An external reference in the range of 100 mV to VDD must be applied to this input. The specified reference input is 2.5 V. This pin is decoupled to GND with a capacitor of at least 0.1 μF. Noninverting Analog Input. Inverting Input. This pin sets the ground ref ...

... Reference Input for the AD7441/AD7451. An external reference in the range of 100 mV to VDD must be applied to this input. The specified reference input is 2.5 V. This pin is decoupled to GND with a capacitor of at least 0.1 μF. Noninverting Analog Input. Inverting Input. This pin sets the ground ref ...

Low Cost, High Speed Differential Amplifier AD8132

... frequency components of the signal. The AD8132 is used for either analog or digital video signals or for other high speed data transmission. The AD8132 is capable of driving either a Category 3 or Category 5 twisted pair or coaxial cable with minimal line attenuation. The AD8132 has considerable cos ...

... frequency components of the signal. The AD8132 is used for either analog or digital video signals or for other high speed data transmission. The AD8132 is capable of driving either a Category 3 or Category 5 twisted pair or coaxial cable with minimal line attenuation. The AD8132 has considerable cos ...

Rail-to-Rail, Very Fast, 2.5 V to 5.5 V, Single-Supply TTL/CMOS Comparator ADCMP603

... input offset voltage) to the 50% point of an output low-to-high transition. Propagation delay measured from the time the input signal crosses the reference (± the input offset voltage) to the 50% point of an output high-to-low transition. Propagation delay measured from the 50% point of the latch en ...

... input offset voltage) to the 50% point of an output low-to-high transition. Propagation delay measured from the time the input signal crosses the reference (± the input offset voltage) to the 50% point of an output high-to-low transition. Propagation delay measured from the 50% point of the latch en ...

Non-isolated, Phase Dimmable, Buck PFC LED Driver with Digital

... The TPS92075 controls the inductor current by controlling two features: (A) The peak inductor current, and (B) The cycle off-time. The following items summarize the basics of the switch operation in this hysteretic controller. • The main switch Q2 turns on and current ramps in the inductor. • The Q2 ...

... The TPS92075 controls the inductor current by controlling two features: (A) The peak inductor current, and (B) The cycle off-time. The following items summarize the basics of the switch operation in this hysteretic controller. • The main switch Q2 turns on and current ramps in the inductor. • The Q2 ...

icm_cairo

... device. What is novel about this design compared with previous common-gate schemes is that it is a totalFET based approach. That is, solely FETs are used to bias, load, and buffer stages. Also, the feedback resistor is connected from the output to the drain of M1 and not to the source of M1, as woul ...

... device. What is novel about this design compared with previous common-gate schemes is that it is a totalFET based approach. That is, solely FETs are used to bias, load, and buffer stages. Also, the feedback resistor is connected from the output to the drain of M1 and not to the source of M1, as woul ...

A Quad of Independently Func Comparators

... designed to meet the needs for a medium speed, TTL compatible comparator for industrial applications. Since no antisaturation clamps are used on the output such as a Baker clamp or other active circuitry, the output leakage current in the OFF state is typically 0.5 nA. This makes the device ideal fo ...

... designed to meet the needs for a medium speed, TTL compatible comparator for industrial applications. Since no antisaturation clamps are used on the output such as a Baker clamp or other active circuitry, the output leakage current in the OFF state is typically 0.5 nA. This makes the device ideal fo ...

Quadruple 8-Bit Digital-to-Analog Converters

... Separate on-chip latches are provided for each of the DACs. Data is transferred into one of these data latches through a common 8-bit TTL/CMOS-compatible (5 V) input port. Control inputs A0 and A1 determine which DAC is loaded when WR goes low. Only the data held in the DAC registers determines the ...

... Separate on-chip latches are provided for each of the DACs. Data is transferred into one of these data latches through a common 8-bit TTL/CMOS-compatible (5 V) input port. Control inputs A0 and A1 determine which DAC is loaded when WR goes low. Only the data held in the DAC registers determines the ...

AD7475 数据手册DataSheet下载

... CS to SCLK setup time Delay from CS until SDATA three-state disabled Data access time after SCLK falling edge SCLK low pulse width SCLK high pulse width SCLK to data valid hold time SCLK falling edge to SDATA high impedance SCLK falling edge to SDATA high impedance CS rising edge to SDATA high imped ...

... CS to SCLK setup time Delay from CS until SDATA three-state disabled Data access time after SCLK falling edge SCLK low pulse width SCLK high pulse width SCLK to data valid hold time SCLK falling edge to SDATA high impedance SCLK falling edge to SDATA high impedance CS rising edge to SDATA high imped ...

High PSR Low Drop-out Voltage Regulator (LDO)

... amplifier must have a open-loop DC gain of 70dB for dropout voltage, with a GBW of 1kHz. It is difficult to achieve a high DC gain with a single stage, therefore the use of two-stage amplifier topology is mandatory for the gain specifications. However, the two-stage amplifier topology is not optimal ...

... amplifier must have a open-loop DC gain of 70dB for dropout voltage, with a GBW of 1kHz. It is difficult to achieve a high DC gain with a single stage, therefore the use of two-stage amplifier topology is mandatory for the gain specifications. However, the two-stage amplifier topology is not optimal ...

OPA2683 Very Low-Power, Dual, Current-Feedback Operational Amplifier APPLICATIONS

... The output capability for the OPA2683 also sets a new mark in performance for very low-power, current-feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA2683 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is comple ...

... The output capability for the OPA2683 also sets a new mark in performance for very low-power, current-feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA2683 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is comple ...

ca3140-a - Intersil

... sinking current to the V- bus, transistor Q16 is the current sinking element. Transistor Q16 is mirror connected to D6, R7, with current fed by way of Q21, R12, and Q20. Transistor Q20, in turn, is biased by current flow through R13, zener D8, and R14. The dynamic current sink is controlled by volta ...

... sinking current to the V- bus, transistor Q16 is the current sinking element. Transistor Q16 is mirror connected to D6, R7, with current fed by way of Q21, R12, and Q20. Transistor Q20, in turn, is biased by current flow through R13, zener D8, and R14. The dynamic current sink is controlled by volta ...

LTC5569 - 300MHz to 4GHz 3.3V Dual Active Downconverting Mixer.

... RFA/RFB (Pin 1/Pin 4): Single-Ended RF Inputs for the A and B Mixers, Respectively. These pins are internally connected to the primary winding of the integrated RF transformers, which have low DC resistance to ground. Series DC-blocking capacitors must be used if the RF sources have DC voltage prese ...

... RFA/RFB (Pin 1/Pin 4): Single-Ended RF Inputs for the A and B Mixers, Respectively. These pins are internally connected to the primary winding of the integrated RF transformers, which have low DC resistance to ground. Series DC-blocking capacitors must be used if the RF sources have DC voltage prese ...

High-Efficiency, 8A, Current-Mode Synchronous Step-Down Switching Regulator with VID Control MAX15109 Features

... Note 2: Limit the junction temperature to +110NC for continuous operation at full current. Note 3: The WLP package is constructed using a unique set of package techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit ...

... Note 2: Limit the junction temperature to +110NC for continuous operation at full current. Note 3: The WLP package is constructed using a unique set of package techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit ...