... The addenda is used to describe the empty sample holder, support rod, and anything else which may generate a background signal during a susceptibility measurement. The capability for subtracting this background signal from the data recorded with a sample present is built into the software package. T ...

CMOS Layout Design and Performance Analysis for

... latch, it will increase its propagation. If one flip-flop in sequential circuits becomes metastable and produces a transition propagation delay is longer than expected, this transition may not have sufficient time to reach all destination flip-flops. A successive flip-flop captures this value while ...

... latch, it will increase its propagation. If one flip-flop in sequential circuits becomes metastable and produces a transition propagation delay is longer than expected, this transition may not have sufficient time to reach all destination flip-flops. A successive flip-flop captures this value while ...

1E6 Electricity and Magnetism

... Fig. 2 Schematic Diagram of a Non-inverting Amplifier Since the input resistance of the amplifier is very high, it can be assumed that the input current required into either input, V+ or V- is negligible and can be taken as zero for the purposes of analysis. In addition, if the loop gain, AOβ >>1, t ...

... Fig. 2 Schematic Diagram of a Non-inverting Amplifier Since the input resistance of the amplifier is very high, it can be assumed that the input current required into either input, V+ or V- is negligible and can be taken as zero for the purposes of analysis. In addition, if the loop gain, AOβ >>1, t ...

How to use the design tool (Ver 1.0) for FAN7631 www.fairchildsemi.com 1

... 2. Input Specifications Expected Input Power DC-Link Capacitor Frequency & Ripple voltage @ Nominal Minimum Input Voltage ...

... 2. Input Specifications Expected Input Power DC-Link Capacitor Frequency & Ripple voltage @ Nominal Minimum Input Voltage ...

Experiment - University of Guelph Physics

... The regulator circuit is as shown below: it uses a Zener diode as a voltage reference (VZ = 5.5V), and a single transistor connected as a voltage follower (or Emitter Follower). Double check to be sure you have not accidentally interchanged any of the transistor leads, also the connections on the Ze ...

... The regulator circuit is as shown below: it uses a Zener diode as a voltage reference (VZ = 5.5V), and a single transistor connected as a voltage follower (or Emitter Follower). Double check to be sure you have not accidentally interchanged any of the transistor leads, also the connections on the Ze ...

5_1-Clickers

... The current in an infinite solenoid with uniform magnetic field B inside is increasing so that the magnitude B in increasing with time as B=B0+kt. A circular loop of radius r is placed coaxially outside the solenoid as shown. Without calculating anything, determine the direction of the field Bind cr ...

... The current in an infinite solenoid with uniform magnetic field B inside is increasing so that the magnitude B in increasing with time as B=B0+kt. A circular loop of radius r is placed coaxially outside the solenoid as shown. Without calculating anything, determine the direction of the field Bind cr ...

Low Cost, Precision JFET Input Operational Amplifiers / ADA4000-1

... in both inverting and noninverting configurations. The devices are capable of driving up to 1000 pF of capacitive loads without oscillations in unity gain configurations. ...

... in both inverting and noninverting configurations. The devices are capable of driving up to 1000 pF of capacitive loads without oscillations in unity gain configurations. ...

AD6630 数据手册DataSheet 下载

... output limiting for ADC and SAW protection with ⬍10° phase variation in recovery from overdrive situations. Designed for “narrow-band” cellular/PCS receivers, the high linearity and low noise performance of the AD6630 allows for implementation in a wide range of applications ranging from ...

... output limiting for ADC and SAW protection with ⬍10° phase variation in recovery from overdrive situations. Designed for “narrow-band” cellular/PCS receivers, the high linearity and low noise performance of the AD6630 allows for implementation in a wide range of applications ranging from ...

Asynchronous Primitives in CML

... In this presentation, CML gates and their advantages and disadvantages are discussed. Also, a summary of a brief description of Asynchronous circuit is presented. It is the main goal of this project to integrate the CML primitives into Asynchronous circuits. ...

... In this presentation, CML gates and their advantages and disadvantages are discussed. Also, a summary of a brief description of Asynchronous circuit is presented. It is the main goal of this project to integrate the CML primitives into Asynchronous circuits. ...

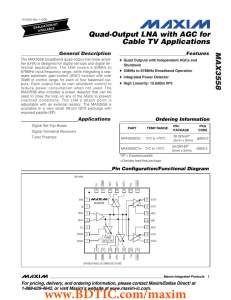

MAX3558

... Cable TV Applications The MAX3558 broadband LNA consists of a single input and four independent outputs. Each output has its own AGC and shutdown function. The LNA covers the 50MHz to 878MHz cable and terrestrial TV frequency range. In addition, the device includes a power detector that can be used ...

... Cable TV Applications The MAX3558 broadband LNA consists of a single input and four independent outputs. Each output has its own AGC and shutdown function. The LNA covers the 50MHz to 878MHz cable and terrestrial TV frequency range. In addition, the device includes a power detector that can be used ...

Simulation and Experimental Demonstration ofLow-/High

... Memristor was first postulated by Prof. Leon Chua in the year 1971, as the missing non-linear two terminal passive device relating magnetic flux and electric charge. The memristor behaves like a non-linear resistor having ‘memory’, as its present state is dependent upon the history of the current th ...

... Memristor was first postulated by Prof. Leon Chua in the year 1971, as the missing non-linear two terminal passive device relating magnetic flux and electric charge. The memristor behaves like a non-linear resistor having ‘memory’, as its present state is dependent upon the history of the current th ...

AD834 数据手册DataSheet 下载

... bipolar process used to fabricate the AD834, the outputs appear as a differential pair of currents at open collectors. To provide a single-ended ground referenced voltage output, some form of external current to voltage conversion is needed. This may take the form of a wideband transformer, balun, o ...

... bipolar process used to fabricate the AD834, the outputs appear as a differential pair of currents at open collectors. To provide a single-ended ground referenced voltage output, some form of external current to voltage conversion is needed. This may take the form of a wideband transformer, balun, o ...

ADS5421 数据资料 dataSheet 下载

... requires each of the analog inputs to be externally biased to a common-mode voltage of typically +2.5V. This allows a symmetrical signal swing while maintaining sufficient headroom to either supply rail. Communication systems are usually AC-coupled in between signal processing stages, making it conv ...

... requires each of the analog inputs to be externally biased to a common-mode voltage of typically +2.5V. This allows a symmetrical signal swing while maintaining sufficient headroom to either supply rail. Communication systems are usually AC-coupled in between signal processing stages, making it conv ...

Feedback compensation design for switched mode power supplies

... Feedback Compensation to meet the above requirements can frequency close to fZMpand considerable improvement in be performed, without much difficulty, for a buck converter output voltage response to be achieved, at the expense of and its derivative. However, for the converters with a non- more desig ...

... Feedback Compensation to meet the above requirements can frequency close to fZMpand considerable improvement in be performed, without much difficulty, for a buck converter output voltage response to be achieved, at the expense of and its derivative. However, for the converters with a non- more desig ...

1 Transimpedance Op-amp Circuit Board: The

... The explanation below is for 4 of the 8 possible circuits, as the other 4 circuits are mirrored on the other side of this circuit board, and component placement can be deduced from this tutorial. The transimpedance configuration that is implemented on these circuit boards is shown below. ...

... The explanation below is for 4 of the 8 possible circuits, as the other 4 circuits are mirrored on the other side of this circuit board, and component placement can be deduced from this tutorial. The transimpedance configuration that is implemented on these circuit boards is shown below. ...

MAX660 CMOS Monolithic Voltage Converter _______________General Description ___________________________ Features

... with a typical operating current of only 120µA provides ideal performance for both battery-powered and boardlevel voltage conversion applications. The MAX660 can also double the output voltage of an input power supply or battery, providing +9.35V at 100mA from a +5V input. A frequency control (FC) p ...

... with a typical operating current of only 120µA provides ideal performance for both battery-powered and boardlevel voltage conversion applications. The MAX660 can also double the output voltage of an input power supply or battery, providing +9.35V at 100mA from a +5V input. A frequency control (FC) p ...

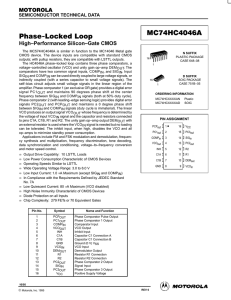

Phase-Locked Loop MC74HC4046A

... frequency between SIG IN and COMP IN signals (both at 50% duty cycle). Phase comparator 2 (with leading–edge sensing logic) provides digital error signals PC2 OUT and PCP OUT and maintains a 0 degree phase shift between SIG IN and COMP IN signals (duty cycle is immaterial). The linear VCO produces a ...

... frequency between SIG IN and COMP IN signals (both at 50% duty cycle). Phase comparator 2 (with leading–edge sensing logic) provides digital error signals PC2 OUT and PCP OUT and maintains a 0 degree phase shift between SIG IN and COMP IN signals (duty cycle is immaterial). The linear VCO produces a ...

CM8870/70C CMOS Integrated DTMF Receiver

... Before the registration of a decoded tone pair, the receiver checks for a valid signal duration (referred to as “characterrecognition-condition”). This check is performed by an external RC time constant driven by ESt. A logic high on ESt causes VC (See Figure 4) to rise as the capacitor discharges. ...

... Before the registration of a decoded tone pair, the receiver checks for a valid signal duration (referred to as “characterrecognition-condition”). This check is performed by an external RC time constant driven by ESt. A logic high on ESt causes VC (See Figure 4) to rise as the capacitor discharges. ...