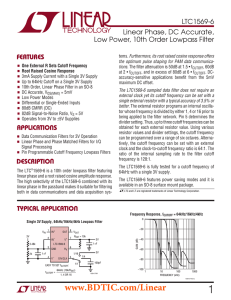

LTC1569-6 - Linear Phase, DC Accurate, Low Power, 10th Order Lowpass Filter

... frequency at which the filter AC response exhibits >1dB of gain peaking. Note 5: The minimum clock frequency is arbitrarily defined as the frequecy at which the filter DC offset changes by more than 5mV. Note 6: For more details refer to the Input and Output Voltage Range paragraph in the Applicatio ...

... frequency at which the filter AC response exhibits >1dB of gain peaking. Note 5: The minimum clock frequency is arbitrarily defined as the frequecy at which the filter DC offset changes by more than 5mV. Note 6: For more details refer to the Input and Output Voltage Range paragraph in the Applicatio ...

IEEE Transactions on Magnetics

... In this technique several pulses are produced in each half- cycle but the width of the pulses is not the same as in the case of multiple-pulse width modulation, however the width of each pulse is varied in accordance with the amplitude of the sine wave reference voltage. The width of the pulse at th ...

... In this technique several pulses are produced in each half- cycle but the width of the pulses is not the same as in the case of multiple-pulse width modulation, however the width of each pulse is varied in accordance with the amplitude of the sine wave reference voltage. The width of the pulse at th ...

modular honours degree course

... e) If, with zero input voltage the output voltage from the circuit in figure Q4 is -(1+R2/R1)xVos . Derive an equation for the output voltage from the same circuit if the input voltage is not zero. If the input offset voltage of the operational amplifier is Vos =1 mV and the resistor ratio R2/R1 = 9 ...

... e) If, with zero input voltage the output voltage from the circuit in figure Q4 is -(1+R2/R1)xVos . Derive an equation for the output voltage from the same circuit if the input voltage is not zero. If the input offset voltage of the operational amplifier is Vos =1 mV and the resistor ratio R2/R1 = 9 ...

A Digitally Controlled Oscillator System for SAW

... study. The DCO is part of a single-chip fully compliant quad-band GSM transceiver realized in a 90-nm digital CMOS process. By operating the DCO at a 4 GSM low-band frequency followed by and frequency dividers, the requirement of on-chip inductor the amount of gate oxide stress are relaxed. It was f ...

... study. The DCO is part of a single-chip fully compliant quad-band GSM transceiver realized in a 90-nm digital CMOS process. By operating the DCO at a 4 GSM low-band frequency followed by and frequency dividers, the requirement of on-chip inductor the amount of gate oxide stress are relaxed. It was f ...

MAX1177 16-Bit, 135ksps, Single-Supply ADC with 0 to 10V Input Range General Description

... The MAX1177 has an input scaler, which allows conversion of input voltages ranging from 0 to 10V, while operating from a single +5V analog supply. The input scaler attenuates and shifts the analog input to match the input range of the internal digital-to-analog converter (DAC). Figure 4 shows the eq ...

... The MAX1177 has an input scaler, which allows conversion of input voltages ranging from 0 to 10V, while operating from a single +5V analog supply. The input scaler attenuates and shifts the analog input to match the input range of the internal digital-to-analog converter (DAC). Figure 4 shows the eq ...

AD7720 数据手册DataSheet下载

... This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code transition (100 . . . 00 to 100 . . . 01 in bipola ...

... This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code transition (100 . . . 00 to 100 . . . 01 in bipola ...

Isolated Sigma-Delta Modulator AD7400 FEATURES

... that converts an analog input signal to a high speed, 1-bit data stream with on-chip digital isolation based on Analog Devices, Inc. iCoupler® technology. The AD7400 operates from a 5 V power supply and accepts a differential input signal of ±200 mV (±320 mV full scale). The analog input is continuo ...

... that converts an analog input signal to a high speed, 1-bit data stream with on-chip digital isolation based on Analog Devices, Inc. iCoupler® technology. The AD7400 operates from a 5 V power supply and accepts a differential input signal of ±200 mV (±320 mV full scale). The analog input is continuo ...

MAX2160/MAX2160EBG ISDB-T Single-Segment Low-IF Tuners General Description Features

... amplifiers, I and Q downconverting mixers, low-IF variablegain amplifiers, and bandpass filters providing in excess of 42dB of image rejection. The parts are capable of operating with either high-side or low-side local oscillator (LO) injection. The MAX2160/EBG’s variable-gain amplifiers provide in ...

... amplifiers, I and Q downconverting mixers, low-IF variablegain amplifiers, and bandpass filters providing in excess of 42dB of image rejection. The parts are capable of operating with either high-side or low-side local oscillator (LO) injection. The MAX2160/EBG’s variable-gain amplifiers provide in ...

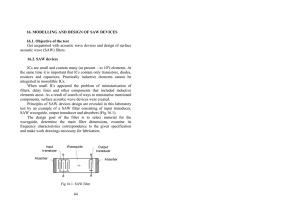

16. Modelling and design of SAW devices

... resistors and capacitors. Practically inductive elements cannot be integrated in monolithic ICs. When small ICs appeared the problem of miniaturisation of filters, delay lines and other components that included inductive elements arose. As a result of search of ways to miniaturise mentioned componen ...

... resistors and capacitors. Practically inductive elements cannot be integrated in monolithic ICs. When small ICs appeared the problem of miniaturisation of filters, delay lines and other components that included inductive elements arose. As a result of search of ways to miniaturise mentioned componen ...

AD827

... into an output voltage. Each of the AD539s two multipliers contains two internal 6 k feedback resistors; one is connected ...

... into an output voltage. Each of the AD539s two multipliers contains two internal 6 k feedback resistors; one is connected ...

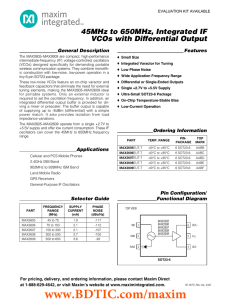

45MHz to 650MHz, Integrated IF VCOs with Differential Output General Description Features

... These low-noise VCOs feature an on-chip varactor and feedback capacitors that eliminate the need for external tuning elements, making the MAX2605–MAX2609 ideal for portable systems. Only an external inductor is required to set the oscillation frequency. In addition, an integrated differential output ...

... These low-noise VCOs feature an on-chip varactor and feedback capacitors that eliminate the need for external tuning elements, making the MAX2605–MAX2609 ideal for portable systems. Only an external inductor is required to set the oscillation frequency. In addition, an integrated differential output ...

Phase-Locked Loop Basics (PLL) - Dennis Fischette`s PLL Tutorials

... • Divide VCO by N fref = fvco/N • Divider may be internal to PLL or after CPU clock tree • Max FBDIV frequency should be greater than max VCO frequency to avoid “run-away” • Minimize FBDIV latency to reduce VDD-induced jitter seen at phase detector • Loop Phase Margin Degradation ~ nTdly – usuall ...

... • Divide VCO by N fref = fvco/N • Divider may be internal to PLL or after CPU clock tree • Max FBDIV frequency should be greater than max VCO frequency to avoid “run-away” • Minimize FBDIV latency to reduce VDD-induced jitter seen at phase detector • Loop Phase Margin Degradation ~ nTdly – usuall ...

Chapter 4 : Resonance Circuit

... Lower value of Q larger the bandwidth. (Lower the selectivity) ...

... Lower value of Q larger the bandwidth. (Lower the selectivity) ...

www.ko4bb.com

... • Divide VCO by N fref = fvco/N • Divider may be internal to PLL or after CPU clock tree • Max FBDIV frequency should be greater than max VCO frequency to avoid “run-away” • Minimize FBDIV latency to reduce VDD-induced jitter seen at phase detector • Loop Phase Margin Degradation ~ nTdly – usuall ...

... • Divide VCO by N fref = fvco/N • Divider may be internal to PLL or after CPU clock tree • Max FBDIV frequency should be greater than max VCO frequency to avoid “run-away” • Minimize FBDIV latency to reduce VDD-induced jitter seen at phase detector • Loop Phase Margin Degradation ~ nTdly – usuall ...

MAX1121 1.8V, 8-Bit, 250Msps Analog-to-Digital Converter with LVDS Outputs for Wideband Applications

... up to 250Msps while consuming only 477mW. At 250Msps and an input frequency of 100MHz, the MAX1121 achieves a spurious-free dynamic range (SFDR) of 68dBc. Its excellent signal-to-noise ratio (SNR) of 48.9dB at 10MHz remains flat (within 0.5dB) for input tones up to 500MHz. This makes the MAX1121 ide ...

... up to 250Msps while consuming only 477mW. At 250Msps and an input frequency of 100MHz, the MAX1121 achieves a spurious-free dynamic range (SFDR) of 68dBc. Its excellent signal-to-noise ratio (SNR) of 48.9dB at 10MHz remains flat (within 0.5dB) for input tones up to 500MHz. This makes the MAX1121 ide ...

STT-1 Quick Start Guide

... 8. SOURCE “MIC-LINE-DI" — selects the front-end input source as either microphone, line level, or 1/4" DI (instrument, keyboard, etc.). Mic, Line, and DI inputs all feed the same frontend amplifiers (selectable via switches as either vacuum tube or solid state, transformer-coupled or transformer-les ...

... 8. SOURCE “MIC-LINE-DI" — selects the front-end input source as either microphone, line level, or 1/4" DI (instrument, keyboard, etc.). Mic, Line, and DI inputs all feed the same frontend amplifiers (selectable via switches as either vacuum tube or solid state, transformer-coupled or transformer-les ...

AD826

... paralleled to obtain even higher load driving capability than that of a single amplifier (100 mA min guaranteed). R1 and R2 are included to limit current flow between amplifier outputs that would arise in the presence of any residual mismatch. ...

... paralleled to obtain even higher load driving capability than that of a single amplifier (100 mA min guaranteed). R1 and R2 are included to limit current flow between amplifier outputs that would arise in the presence of any residual mismatch. ...

Results

... In the first part of this lab, the objective was to study the response of the voltage across a capacitor in an RLC circuit as a function of input. It was shown that the response consisted of a transient and steady state part. The type of transient response was dependent on the resistor used. It was ...

... In the first part of this lab, the objective was to study the response of the voltage across a capacitor in an RLC circuit as a function of input. It was shown that the response consisted of a transient and steady state part. The type of transient response was dependent on the resistor used. It was ...