MAX187/MAX189 +5V, Low-Power, 12-Bit Serial ADCs General Description Features

... stringent than those for a successive-approximation ADC without a T/H. The typical input capacitance is 16pF. The amplifier bandwidth should be sufficient to handle the frequency of the input signal. The MAX400 and OP07 work well at lower frequencies. For higher-frequency operation, the MAX427 and O ...

... stringent than those for a successive-approximation ADC without a T/H. The typical input capacitance is 16pF. The amplifier bandwidth should be sufficient to handle the frequency of the input signal. The MAX400 and OP07 work well at lower frequencies. For higher-frequency operation, the MAX427 and O ...

asynchronous analog-discrete converter using an analog signal

... are involved, the interface becomes much more complex, being then necessary a way of transforming eletronically the signals from the analog form for the digital one. For this the analog-digital converters (CAD) and the digital-analog converters (DAC) are used. All these architectures possess their a ...

... are involved, the interface becomes much more complex, being then necessary a way of transforming eletronically the signals from the analog form for the digital one. For this the analog-digital converters (CAD) and the digital-analog converters (DAC) are used. All these architectures possess their a ...

VOLTAGE LEVEL TRANSLATION (SL) - Family

... and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critic ...

... and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critic ...

BD9302FP

... 0.01 μF or less may cause overshoot to the output voltage. If any startup-related function (sequence) of other power supply is provided, use a high-accuracy product (e.g. ¥ 5R) or the like. Furthermore, since the soft start time varies with the input voltage, output voltage, load, coil, output capac ...

... 0.01 μF or less may cause overshoot to the output voltage. If any startup-related function (sequence) of other power supply is provided, use a high-accuracy product (e.g. ¥ 5R) or the like. Furthermore, since the soft start time varies with the input voltage, output voltage, load, coil, output capac ...

ADS5410 数据资料 dataSheet 下载

... selected depending on the application. Rin and Cin can be placed to isolate the source from the switching inputs of the ADC and to implement a low pass RC filter to limit the input noise in the ADC. Although not needed, it is recommended to lay out the circuit with placement for those 3 components, ...

... selected depending on the application. Rin and Cin can be placed to isolate the source from the switching inputs of the ADC and to implement a low pass RC filter to limit the input noise in the ADC. Although not needed, it is recommended to lay out the circuit with placement for those 3 components, ...

Wording for TIA-1083

... 10. If any of the above results do not meet the requirements of clause Error! Reference source not found., change the volume control setting, or move the probe to another location within the measurement area specified in step 3, or both, and repeat steps 4 through 8 above until all of the requiremen ...

... 10. If any of the above results do not meet the requirements of clause Error! Reference source not found., change the volume control setting, or move the probe to another location within the measurement area specified in step 3, or both, and repeat steps 4 through 8 above until all of the requiremen ...

Offset Error

... CONVERSION TIME - is the time required for a complete measurement by an analog-to-digital converter. Since the Conversion Time does not include acquisition time, multiplexer set up time, or other elements of a complete conversion cycle, the conversion time may be less than the Throughput Time. Numbe ...

... CONVERSION TIME - is the time required for a complete measurement by an analog-to-digital converter. Since the Conversion Time does not include acquisition time, multiplexer set up time, or other elements of a complete conversion cycle, the conversion time may be less than the Throughput Time. Numbe ...

AN14 - Designs for High Performance Voltage-to-Frequency Converters

... input steps. Instead, the charge is fed back directly to the oscillator, which can respond immediately. Although this approach permits fast response, it also requires attention to parasitics to achieve high linearity and low drift. ...

... input steps. Instead, the charge is fed back directly to the oscillator, which can respond immediately. Although this approach permits fast response, it also requires attention to parasitics to achieve high linearity and low drift. ...

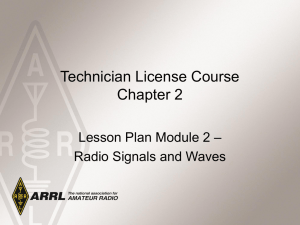

C. Wavelength

... • Instead of varying amplitude, if we vary the frequency in step with the information waveform – FM is produced. • FM signals are much more resistant to the effects of noise but require more bandwidth. • FM bandwidth (for voice) is between 5 and 15 kHz. ...

... • Instead of varying amplitude, if we vary the frequency in step with the information waveform – FM is produced. • FM signals are much more resistant to the effects of noise but require more bandwidth. • FM bandwidth (for voice) is between 5 and 15 kHz. ...

LMK00105 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator

... Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information. When using differential signals with VCM outside of the acceptable range for the specified VID, the clock must be AC coupled. The ESR requirements stated are what is necessary in order to ...

... Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information. When using differential signals with VCM outside of the acceptable range for the specified VID, the clock must be AC coupled. The ESR requirements stated are what is necessary in order to ...

74LS151 - ECE Labs

... the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters ...

... the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters ...

Experiment 9: Driven RLC Circuits

... When we put these elements together we will see that at low frequencies the capacitor will “dominate” (it fills up limiting the current) and current will lead whereas at high frequencies the inductor will dominate (it fights the rapid changes) and current will lag. At resonance the frequency is such ...

... When we put these elements together we will see that at low frequencies the capacitor will “dominate” (it fills up limiting the current) and current will lead whereas at high frequencies the inductor will dominate (it fights the rapid changes) and current will lag. At resonance the frequency is such ...

4.2.3 – Resonant Filters

... It will probably not come as a surprise to you that the inductor also behaves differently in an a.c. circuit compared to a d.c. one, again to signify its use in an a.c. circuit we call it’s ‘resistance’ to the flow of current reactance. The reactance of an inductor is given by the formula X L 2fL ...

... It will probably not come as a surprise to you that the inductor also behaves differently in an a.c. circuit compared to a d.c. one, again to signify its use in an a.c. circuit we call it’s ‘resistance’ to the flow of current reactance. The reactance of an inductor is given by the formula X L 2fL ...

Analog Applications Journal

... Introduction to phase-locked loop system modeling . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Phase-locked loops (PLLs) are one of the basic building blocks in modern electronic systems. They have been widely used in communications, multimedia and many other applications. Starting from a ...

... Introduction to phase-locked loop system modeling . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Phase-locked loops (PLLs) are one of the basic building blocks in modern electronic systems. They have been widely used in communications, multimedia and many other applications. Starting from a ...

![[PDF]](http://s1.studyres.com/store/data/008779546_1-e58bb7eeacffbdd4ead5276b5caa02c6-300x300.png)