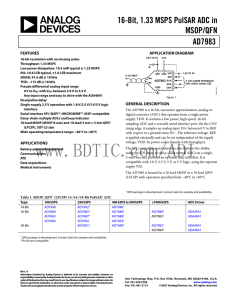

AD7983 数据手册DataSheet下载

... Convert Input. This input has multiple functions. On its risng edge, it initiates the conversions and selects the interface mode of the part: chain or CS mode. In CS mode, it enables the SDO pin when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion res ...

... Convert Input. This input has multiple functions. On its risng edge, it initiates the conversions and selects the interface mode of the part: chain or CS mode. In CS mode, it enables the SDO pin when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion res ...

74CBTLV3257 1. General description Quad 1-of-2 multiplexer/demultiplexer

... common select (S) and output enable (OE) inputs. The low ON resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. When pin OE = LOW, one of the two switches is selected (low-impedance ON-state) with pin S. Whe ...

... common select (S) and output enable (OE) inputs. The low ON resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. When pin OE = LOW, one of the two switches is selected (low-impedance ON-state) with pin S. Whe ...

74CBTLV3253 1. General description Dual 1-of-4 multiplexer/demultiplexer

... common select inputs (S0, S1) and two output enable inputs (1OE, 2OE). The low ON resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. When pin nOE = LOW, one of the four switches is selected (low-impedance O ...

... common select inputs (S0, S1) and two output enable inputs (1OE, 2OE). The low ON resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. When pin nOE = LOW, one of the four switches is selected (low-impedance O ...

PCAL9554B; PCAL9554C 1. General description Low-voltage 8-bit I

... conflicts. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in ACPI power switches, sensors, push buttons, LEDs, fan control, etc. In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5. ...

... conflicts. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in ACPI power switches, sensors, push buttons, LEDs, fan control, etc. In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5. ...

Scheduler

... QoS (Quality of Service) mechanisms are becoming increasingly popular in current networks. This is mainly due to the varied type of applications (such as voice, video, real-time streaming data) concurrently using the network. These applications typically require different levels of performance in te ...

... QoS (Quality of Service) mechanisms are becoming increasingly popular in current networks. This is mainly due to the varied type of applications (such as voice, video, real-time streaming data) concurrently using the network. These applications typically require different levels of performance in te ...

ADC081500 High Performance, Low Power, 8

... Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronous to this signal. This signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. The DCLK outputs are not active during a calibration cycle. ...

... Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronous to this signal. This signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. The DCLK outputs are not active during a calibration cycle. ...

GENERAL DESCRIPTION FEATURES

... Sleep mode is entered under two different conditions: bus low and undervoltage. An enable bit makes entry into Sleep optional for each condition. Sleep mode is not entered if a charger is connected (VPLS > VDD + 50mV) or if a charge current of 1.6mV / RSNS is measured from SNS to VSS. The DS2784 exi ...

... Sleep mode is entered under two different conditions: bus low and undervoltage. An enable bit makes entry into Sleep optional for each condition. Sleep mode is not entered if a charger is connected (VPLS > VDD + 50mV) or if a charge current of 1.6mV / RSNS is measured from SNS to VSS. The DS2784 exi ...

PTN3381D - NXP Semiconductors

... DVI v1.0 or HDMI v1.3a specification. By using PTN3381D, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381D main high-sp ...

... DVI v1.0 or HDMI v1.3a specification. By using PTN3381D, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381D main high-sp ...

PTN3381B Enhanced performance HDMI/DVI level shifter with

... or HDMI v1.3a specification. By using PTN3381B, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381B main high-speed diffe ...

... or HDMI v1.3a specification. By using PTN3381B, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381B main high-speed diffe ...

PRO-2014-0192-uPnP_cloud_update - FTP

... description document (DDD) than can be retrieved by means of HTTP. The device description contains information about the device and the implemented services in the device. The service description location can be derived from the information in the device description and can also be retrieved by mean ...

... description document (DDD) than can be retrieved by means of HTTP. The device description contains information about the device and the implemented services in the device. The service description location can be derived from the information in the device description and can also be retrieved by mean ...

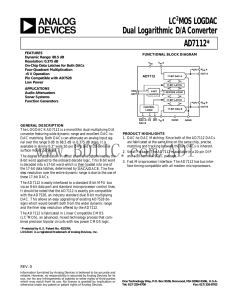

AD7112 数据手册DataSheet 下载

... Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any other digital grounds to this analog ground point. Low impedance analog and digital power supply common returns are essential for ...

... Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any other digital grounds to this analog ground point. Low impedance analog and digital power supply common returns are essential for ...

Institutionen f r systemteknik ö

... A Tactical Data Link (TDL) system has been deployed in many military missions as a winning strategy. The performance of a TDL system is governed by the MAC protocol. The MAC protocol that is able to provide more flexibility and high quality of services is more desirable. However, most MAC protocols ...

... A Tactical Data Link (TDL) system has been deployed in many military missions as a winning strategy. The performance of a TDL system is governed by the MAC protocol. The MAC protocol that is able to provide more flexibility and high quality of services is more desirable. However, most MAC protocols ...

Berkeley NOW - Computer Science Division

... • 16 transmit power settings • For each transmit power setting, each node transmits 20 packets. • Receivers log successfully received packets. • Nodes transmit one after the other in a token-ring fashion • No collisions. ...

... • 16 transmit power settings • For each transmit power setting, each node transmits 20 packets. • Receivers log successfully received packets. • Nodes transmit one after the other in a token-ring fashion • No collisions. ...

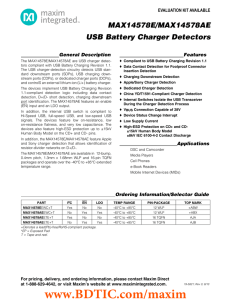

MAX14578E/MAX14578AE USB Battery Charger Detectors EVALUATION KIT AVAILABLE General Description

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

ccna4-mod3-PPP

... – Link Access Procedure, Balanced (LAPB) for X.25 – Link Access Procedure on the D channel (LAPD) for ISDN – Link Access Procedure for Modems (LAPM) and PPP for modems – Link Access Procedure for Frame Relay (LAPF) for Frame Relay ...

... – Link Access Procedure, Balanced (LAPB) for X.25 – Link Access Procedure on the D channel (LAPD) for ISDN – Link Access Procedure for Modems (LAPM) and PPP for modems – Link Access Procedure for Frame Relay (LAPF) for Frame Relay ...

Datasheet - Integrated Device Technology

... reduced. Even though the differential input can handle full rail LVCMOS signaling, it is recommended that the amplitude be reduced. The datasheet specifies a lower differential amplitude, however this only applies to differential signals. For single-ended applications, the swing can be larger, howev ...

... reduced. Even though the differential input can handle full rail LVCMOS signaling, it is recommended that the amplitude be reduced. The datasheet specifies a lower differential amplitude, however this only applies to differential signals. For single-ended applications, the swing can be larger, howev ...

21-04-0164-04-0000-Freescale_March2005

... Who advertises this information and how frequently is it done? • MIH-Beacon information may be exchanged by the network controller only during association with the MN Or, it may be exchanged more frequently – in this case MN may choose to look for this only when required, or it may choose to batte ...

... Who advertises this information and how frequently is it done? • MIH-Beacon information may be exchanged by the network controller only during association with the MN Or, it may be exchanged more frequently – in this case MN may choose to look for this only when required, or it may choose to batte ...