![Wiley Publishing - CCNA For Dummies [2000].](http://s1.studyres.com/store/data/008049680_1-a9b72081a3d6e4abe69a6bd824c30e5a-300x300.png)

Chapter 5 - Ethernet

... The two commonly used methods are: CSMA/Collision Detection • The device monitors the media for the presence of a data signal • If a data signal is absent, indicating that the media is free, the device transmits the data • If signals are then detected that show another device was transmitting at the ...

... The two commonly used methods are: CSMA/Collision Detection • The device monitors the media for the presence of a data signal • If a data signal is absent, indicating that the media is free, the device transmits the data • If signals are then detected that show another device was transmitting at the ...

12-Bit Input-Buffered 80 MSPS ADC with JESD204A Output Interface

... The ADS61JB23 is a high-performance, low-power, single channel analog-to-digital converter with an integrated JESD204A output interface. Available in a 6 mm x 6 mm QFN package, with both single-lane and dual-lane output modes, the ADS61JB23 offers an unprecedented level of compactness. The output in ...

... The ADS61JB23 is a high-performance, low-power, single channel analog-to-digital converter with an integrated JESD204A output interface. Available in a 6 mm x 6 mm QFN package, with both single-lane and dual-lane output modes, the ADS61JB23 offers an unprecedented level of compactness. The output in ...

Computer Networking : Principles, Protocols and Practice

... interface and there is one physical link between each host and the center of the star. The node at the center of the star can be either a piece of equipment that amplifies an electrical signal, or an active device, such as a piece 2 In this book, we focus on networks that are used on Earth. These ne ...

... interface and there is one physical link between each host and the center of the star. The node at the center of the star can be either a piece of equipment that amplifies an electrical signal, or an active device, such as a piece 2 In this book, we focus on networks that are used on Earth. These ne ...

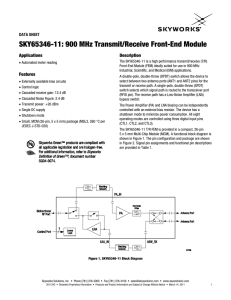

SKY65344-21 数据资料DataSheet下载

... 2500 MHz high-efficiency transmit path and a low-loss bidirectional path. The bidirectional path can be used to directly connect the antenna port to a directional RF port. ...

... 2500 MHz high-efficiency transmit path and a low-loss bidirectional path. The bidirectional path can be used to directly connect the antenna port to a directional RF port. ...

8-Bit Micro Power OCTAL Digital-to-Analog Converter with Rail

... providing the widest possible output dynamic range. The DAC088S085 has a 16-bit input shift register that controls the mode of operation, the power-down condition, and the DAC channels' register and output value. All eight DAC outputs can be updated simultaneously or individually. A power-on reset c ...

... providing the widest possible output dynamic range. The DAC088S085 has a 16-bit input shift register that controls the mode of operation, the power-down condition, and the DAC channels' register and output value. All eight DAC outputs can be updated simultaneously or individually. A power-on reset c ...

74CBTLVD3244 1. General description 8-bit level-shifting bus switch with 4-bit output enables

... The 74CBTLVD3244 is a dual 4-pole, single-throw bus switch. The device features two output enable inputs (nOE) that each control four switch channels. The switches are disabled when the associated nOE input is HIGH. Schmitt trigger action at control inputs makes the circuit tolerant of slower input ...

... The 74CBTLVD3244 is a dual 4-pole, single-throw bus switch. The device features two output enable inputs (nOE) that each control four switch channels. The switches are disabled when the associated nOE input is HIGH. Schmitt trigger action at control inputs makes the circuit tolerant of slower input ...

AD7798 数据手册DataSheet下载

... Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK has a Schmitt-triggered input, making the interface suitable for opto-isolated applications. The serial clock can be continuous, with all data transmitted in a continuous train of pulses. Alternatively, i ...

... Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK has a Schmitt-triggered input, making the interface suitable for opto-isolated applications. The serial clock can be continuous, with all data transmitted in a continuous train of pulses. Alternatively, i ...

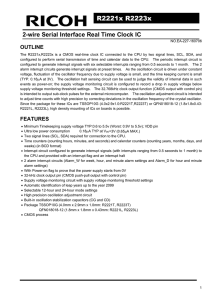

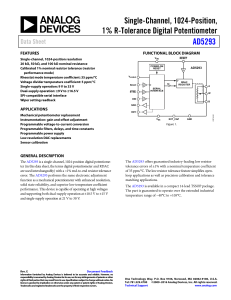

AD5293 - Analog Devices

... The AD5293 is a single-channel, 1024-position digital potentiometer (in this data sheet, the terms digital potentiometer and RDAC are used interchangeably) with a <1% end-to-end resistor tolerance error. The AD5293 performs the same electronic adjustment function as a mechanical potentiometer with e ...

... The AD5293 is a single-channel, 1024-position digital potentiometer (in this data sheet, the terms digital potentiometer and RDAC are used interchangeably) with a <1% end-to-end resistor tolerance error. The AD5293 performs the same electronic adjustment function as a mechanical potentiometer with e ...

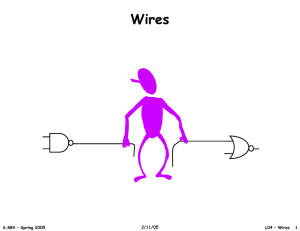

Wires - Massachusetts Institute of Technology

... – make wires wider, increase in C is less than increase in C because of fringing fields – use parallel vias at contacts – floorplanning to keep wires short – careful routing to avoid unnecessary layer changes (vias) ...

... – make wires wider, increase in C is less than increase in C because of fringing fields – use parallel vias at contacts – floorplanning to keep wires short – careful routing to avoid unnecessary layer changes (vias) ...

ch05

... (RTL) Design Slides to accompany the textbook Digital Design, First Edition, by Frank Vahid, John Wiley and Sons Publishers, 2007. ...

... (RTL) Design Slides to accompany the textbook Digital Design, First Edition, by Frank Vahid, John Wiley and Sons Publishers, 2007. ...

92 1. PURPOSE The purpose of this experiment is to show

... WARNING: An ammeter must never be placed across a voltage source; it must only be used in series with a load that does not draw more than the full scale current. 2.3. The Ohmmeter In general, an ohmmeter is designed to measure resistance in the low, mid or high range. The mid-range of an ohmmeter is ...

... WARNING: An ammeter must never be placed across a voltage source; it must only be used in series with a load that does not draw more than the full scale current. 2.3. The Ohmmeter In general, an ohmmeter is designed to measure resistance in the low, mid or high range. The mid-range of an ohmmeter is ...

Maxim MAX13487 - RS232 converter

... The MAX13487E/MAX13488E +5V, half-duplex, ±15kV ESD-protected RS-485/RS-422-compatible transceivers feature one driver and one receiver. The MAX13487E/ MAX13488E include a hot-swap capability to eliminate false transitions on the bus during power-up or live insertion. The MAX13487E/MAX13488E feature ...

... The MAX13487E/MAX13488E +5V, half-duplex, ±15kV ESD-protected RS-485/RS-422-compatible transceivers feature one driver and one receiver. The MAX13487E/ MAX13488E include a hot-swap capability to eliminate false transitions on the bus during power-up or live insertion. The MAX13487E/MAX13488E feature ...

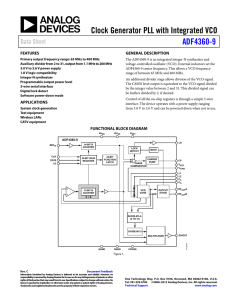

ADF4360-9 Clock Generator PLL with Integrated VCO (Rev. C)

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

TMDS171 3.4 Gbps TMDS Retimer (Rev. D)

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absol ...

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absol ...

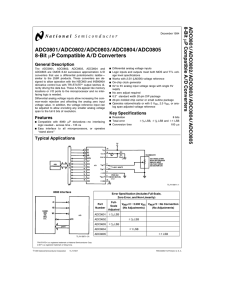

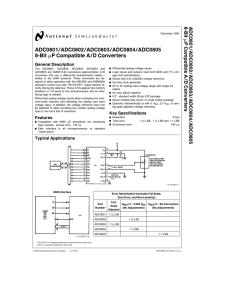

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit mP Compatible A/D Converters 8-Bit m

... Note 4: For VIN( b ) t VIN( a ) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see block diagram) which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the VCC supply. Be careful, during testing a ...

... Note 4: For VIN( b ) t VIN( a ) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see block diagram) which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the VCC supply. Be careful, during testing a ...

74CBTLVD3245 1. General description 8-bit level-shifting bus switch with output enable

... This document contains data from the objective specification for product development. ...

... This document contains data from the objective specification for product development. ...

The DatasheetArchive - Datasheet Search Engine

... The following design considerations are general in nature and must be followed regardless of final use or configuration: 1. Paths to ground should be made as short as possible. 2. The ground pads of the SKY65346-11 have special electrical and thermal grounding requirements. These pads are the main t ...

... The following design considerations are general in nature and must be followed regardless of final use or configuration: 1. Paths to ground should be made as short as possible. 2. The ground pads of the SKY65346-11 have special electrical and thermal grounding requirements. These pads are the main t ...

JRAX/SA3: Title of Activity - Indico

... • The circuit information held by the MP/MA includes the following: – Operational status Up, Down, Degraded, Unknown – Admin status Normal operations, Maintenance, Troubleshooting, UnderRepair, Unknown Note: the GN2 project does not mandate *how* to populate the XML file (in MP) or database (in MA) ...

... • The circuit information held by the MP/MA includes the following: – Operational status Up, Down, Degraded, Unknown – Admin status Normal operations, Maintenance, Troubleshooting, UnderRepair, Unknown Note: the GN2 project does not mandate *how* to populate the XML file (in MP) or database (in MA) ...

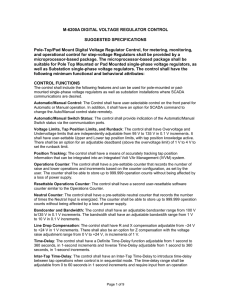

Suggested Specification

... the control automatically reads to allow user login. The control’s design shall include the ability to disable ports and services not required for normal or emergency operations. In cases where disabling is not possible, the port or service shall be password and access level protected through a comm ...

... the control automatically reads to allow user login. The control’s design shall include the ability to disable ports and services not required for normal or emergency operations. In cases where disabling is not possible, the port or service shall be password and access level protected through a comm ...