11 mW Power, 2.3 V to 5.5 V, Complete DDS AD9838

... Serial Clock Input. Data is clocked into the AD9838 on each falling edge of SCLK. Active Low Control Input. FSYNC is the frame synchronization signal for the input data. When FSYNC is taken low, the internal logic is informed that a new word is being loaded into the device. Logic Output. The compara ...

... Serial Clock Input. Data is clocked into the AD9838 on each falling edge of SCLK. Active Low Control Input. FSYNC is the frame synchronization signal for the input data. When FSYNC is taken low, the internal logic is informed that a new word is being loaded into the device. Logic Output. The compara ...

MIDAS 4x System Design 1.5 MB

... Customer Support Department. 2. Be prepared to supply the Customer Support representative with the model number, serial number, and a description of the problem. 3. To ensure that the product is not damaged during shipping, pack the product in its original shipping carton/packaging. 4. Ship the prod ...

... Customer Support Department. 2. Be prepared to supply the Customer Support representative with the model number, serial number, and a description of the problem. 3. To ensure that the product is not damaged during shipping, pack the product in its original shipping carton/packaging. 4. Ship the prod ...

BDTIC T D A 5 2 2 1

... detector as is the output of the 10.7 MHz center frequency VCO. The demodulator gain is typically 200µV/kHz. The passive loop filter output that is comprised fully on chip is fed to both the VCO and the modulation format switch described in more detail below. This signal is representing the demodula ...

... detector as is the output of the 10.7 MHz center frequency VCO. The demodulator gain is typically 200µV/kHz. The passive loop filter output that is comprised fully on chip is fed to both the VCO and the modulation format switch described in more detail below. This signal is representing the demodula ...

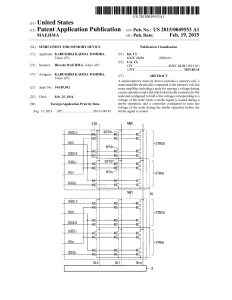

M40Z300W

... capacitors are used to store energy which stabilizes the VCC bus. The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be ...

... capacitors are used to store energy which stabilizes the VCC bus. The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be ...

i ?g 255` i

... and detects the state of the memory cell through the bit line. The memory 10 can store data of two (or more) bits in one memory cell. Therefore, the data circuit and page buffer 3 ...

... and detects the state of the memory cell through the bit line. The memory 10 can store data of two (or more) bits in one memory cell. Therefore, the data circuit and page buffer 3 ...

4-channel half-duplex m-lvds line transceivers

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

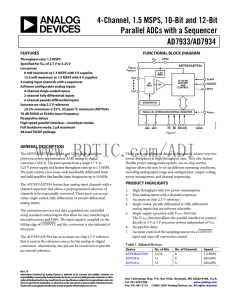

AD7933 数据手册DataSheet下载

... VDD = VDRIVE = 2.7 V to 5.25 V, internal/external VREF = 2.5 V, unless otherwise noted. fCLKIN = 25.5 MHz, fSAMPLE = 1.5 MSPS; TA = TMIN to TMAX, unless otherwise noted. ...

... VDD = VDRIVE = 2.7 V to 5.25 V, internal/external VREF = 2.5 V, unless otherwise noted. fCLKIN = 25.5 MHz, fSAMPLE = 1.5 MSPS; TA = TMIN to TMAX, unless otherwise noted. ...

Abstract Verilog Part 2

... memories take place at the next clock edge just like with registers. Reads, however, can be either asynchronous or synchronous. In asynchronous (combinational) memories, the memory output value changes whenever the read address changes. In synchronous (pipelined) memories, the memory output value do ...

... memories take place at the next clock edge just like with registers. Reads, however, can be either asynchronous or synchronous. In asynchronous (combinational) memories, the memory output value changes whenever the read address changes. In synchronous (pipelined) memories, the memory output value do ...

Q1 on FINAL

... The upper layer protocols will determine the frame was lost and request retransmission. ...

... The upper layer protocols will determine the frame was lost and request retransmission. ...

37.0-40.0 GHz GaAs Receiver (USB) SMT, 7x7 mm R1008-QB Features

... system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Package Attachment - This packaged product from Mimix Broadband is provided as a rugged surface mount package compatible with high volume so ...

... system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Package Attachment - This packaged product from Mimix Broadband is provided as a rugged surface mount package compatible with high volume so ...

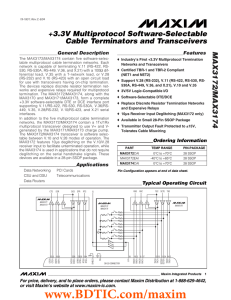

MAX3172/MAX3174 +3.3V Multiprotocol Software-Selectable Cable Terminators and Transceivers General Description

... a high-impedance state in no-cable mode, allowing this output line to be shared with other receivers (the receiver output has an internal pullup resistor to pull the output HIGH if not driven). Also, in no-cable mode, the transmitter output enters a high-impedance state so that this output can be sh ...

... a high-impedance state in no-cable mode, allowing this output line to be shared with other receivers (the receiver output has an internal pullup resistor to pull the output HIGH if not driven). Also, in no-cable mode, the transmitter output enters a high-impedance state so that this output can be sh ...

Series NRX Circuit Breaker Wiring Diagrams

... 3. If a Communication Module is used, see Figures 7, 8 or 9 for different wiring. A Communication Module will require 24VDC power which in turn provides isolated power to the Digitrip in the circuit breaker. If a Communication Module is not used, and if auxiliary voltage is desired for Alarms or dis ...

... 3. If a Communication Module is used, see Figures 7, 8 or 9 for different wiring. A Communication Module will require 24VDC power which in turn provides isolated power to the Digitrip in the circuit breaker. If a Communication Module is not used, and if auxiliary voltage is desired for Alarms or dis ...

CY7C63413C, CY7C63513C, CY7C63613C Low

... eliminates the need for firmware to attempt to compensate if the upper four bits happened to increment right after the lower 8 bits are read. The CY7C63413C/513C/613C include an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB devic ...

... eliminates the need for firmware to attempt to compensate if the upper four bits happened to increment right after the lower 8 bits are read. The CY7C63413C/513C/613C include an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB devic ...

DS90UB933-Q1 FPD-Link III Serializer for 1-MP/60

... GPO[3] can be configured to be the output for input signals coming from the GPIO[3] pin on the deserializer or can be configured to be the output of the local register setting on the Input/Output, serializer. It can also be configured to be the input clock pin when the DS90UB933-Q1 LVCMOS serializer ...

... GPO[3] can be configured to be the output for input signals coming from the GPIO[3] pin on the deserializer or can be configured to be the output of the local register setting on the Input/Output, serializer. It can also be configured to be the input clock pin when the DS90UB933-Q1 LVCMOS serializer ...

差分放大器系列AD8321 数据手册DataSheet 下载

... The AD8321 is primarily intended for use as the return path (also called upstream path) Power Amplifier (PA) or line driver in cable modem applications. Upstream data is modulated in either QPSK or QAM format. This is done either in DSP or by a dedicated QPSK/QAM modulator such as the AD9853 or othe ...

... The AD8321 is primarily intended for use as the return path (also called upstream path) Power Amplifier (PA) or line driver in cable modem applications. Upstream data is modulated in either QPSK or QAM format. This is done either in DSP or by a dedicated QPSK/QAM modulator such as the AD9853 or othe ...

GTL2006PW

... leak to the power supply if they are pulled high while the device is unpowered. The GTL inputs will also not leak to the power supply under the same conditions. The LVTTL totem pole outputs, however, are not open drain type outputs and there will be current flow on these pins if they are pulled high ...

... leak to the power supply if they are pulled high while the device is unpowered. The GTL inputs will also not leak to the power supply under the same conditions. The LVTTL totem pole outputs, however, are not open drain type outputs and there will be current flow on these pins if they are pulled high ...

AD7190 数据手册DataSheet下载

... CS falling edge to SCLK active edge setup time4 Data valid to SCLK edge setup time Data valid to SCLK edge hold time CS rising edge to SCLK edge hold time ...

... CS falling edge to SCLK active edge setup time4 Data valid to SCLK edge setup time Data valid to SCLK edge hold time CS rising edge to SCLK edge hold time ...

Understanding LDO Dropout

... Calculating LDO Dropout First, it is necessary to understand what is happening to the LDO during dropout. A typical LDO has an n-channel or a p-channel FET pass element. The control circuitry modulates the gate of the FET so that it operates in the linear region. Figure 1 shows a typical FET V-I cur ...

... Calculating LDO Dropout First, it is necessary to understand what is happening to the LDO during dropout. A typical LDO has an n-channel or a p-channel FET pass element. The control circuitry modulates the gate of the FET so that it operates in the linear region. Figure 1 shows a typical FET V-I cur ...